### Design of a Lightweight Real-Time Streaming Kernel

Bas van Sisseren

Distributed and Embedded Systems, University of Twente.

Date:

August 13, 2007

#### Committee:

ir. P.G. Jansenprof. dr. ir. G.J.M. Smitir. M.H. Wiggersir. T. Hofmeijer

#### Abstract

This report describes a flexible real-time kernel, which is optimised for data-streams, to be used for multi-processor environments.

Currently, two processors are used: the MSP430 and the ARM 946E-S. For the first architecture, an in-house kernel has been developed by Tjerk Hofmeijer. For the ARM architecture, the currently available kernel implementations either lack support for dynamic real-time scheduling or are not available.

This document describes the kernel *BasOS*, which was developed within this project. BasOS is a flexible real-time kernel with low memory usage, efficient interrupt handling, both real-time and non-real-time scheduling. The kernel has a programmer-friendly interface and supports several peripherals, like the USART (serial port), USB and the Montium processors.

Also, several tools, which support the use of BasOS: a stack usage predictor, a loader of dynamic tasks and a second stage boot loader.

#### Preface

In this report, I have described the aspects of my assignment to extend and implement a real-time kernel for the Basic Concept Verification Platform (BCVP) and Highly integrated Concept Verification Platform (HiCVP). Unfortunately, the HiCVP is still under development. Therefore all development has been done on the BCVP, the predecessor of the HiCVP.

This document is mainly written for people interested in the kernel mechanisms of BasOS and for those who would like to write device drivers and applications for the kernel.

The reasons why I have chosen to implement a kernel is because I've always wanted to write a system without being dependent on other software. The other reason is that I like to bind optimal solutions to complex environments.

I hereby would like to thank my committee for supporting me in various ways in the process of designing the kernel and writing this report. I would also like to thank Pascal Wolkotte and Lodewijk Smit for helping me find my way on the BCVP platform and the extensive support they have given me. I would like to thank Albert Molderink and Marcel Hamer for putting various parts of the kernel into discussion. Last but not least, I would like to thank the many proofreaders of this document.

# Contents

| 1        | Intr | oducti                  | on 4                                                                                                                                            |

|----------|------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | $\operatorname{Proble}$ | $m description \dots \dots$               |

|          | 1.2  | Docun                   | nent overview                                                                                                                                   |

| <b>2</b> | Stat | te of tl                | ne Art 6                                                                                                                                        |

|          | 2.1  | Currei                  | $t implementations \ldots 6$           |

|          |      | 2.1.1                   | DCOS                                                                                                                                            |

|          |      | 2.1.2                   | eCos                                                                                                                                            |

|          |      | 2.1.3                   | TinyOS                                                                                                                                          |

|          |      | 2.1.4                   | RTlinux                                                                                                                                         |

|          |      | 2.1.5                   | Summary                                                                                                                                         |

|          | 2.2  | The B                   | asic Concept Verification Platform                                                                                                              |

|          |      | 2.2.1                   | The ARM Architecture                                                                                                                            |

|          |      | 2.2.2                   | Memory Layout                                                                                                                                   |

|          | 2.3  | Impuls                  | se handling                                                                                                                                     |

|          | 2.4  | Real-t                  | ime Scheduling                                                                                                                                  |

|          |      | 2.4.1                   | Earliest Deadline First with deadline Inheritance (EDFI)                                                                                        |

|          |      | 2.4.2                   | EDFI Feasibility Analysis                                                                                                                       |

| 3        | Ker  | nel De                  | sign 17                                                                                                                                         |

| 0        | 3.1  |                         | ation Interface                                                                                                                                 |

|          | 0.1  | 3.1.1                   | Tasks                                                                                                                                           |

|          |      | 3.1.2                   | Signals and conditions                                                                                                                          |

|          |      | 3.1.2                   | Pipes                                                                                                                                           |

|          | 3.2  |                         | $\begin{array}{c} 1 \text{ pos} \\ 1 \text{ pts} \\ \dots \\ $          |

|          | 3.3  |                         | $1$ ing-oriented Scheduling $\dots \dots \dots$ |

|          | 0.0  | 3.3.1                   | Delaying the task release                                                                                                                       |

|          |      | 3.3.2                   | Aperiodic tasks                                                                                                                                 |

|          |      | 3.3.3                   | The scheduling model                                                                                                                            |

|          |      | 3.3.4                   | The scheduler impulse handlers                                                                                                                  |

|          |      | 0.0.1                   |                                                                                                                                                 |

| 4        | Imp  | lemen                   |                                                                                                                                                 |

|          | 4.1  | Memo                    | ry Management                                                                                                                                   |

|          |      | 4.1.1                   | Heap Memory                                                                                                                                     |

|          | 4.2  | Tasks                   |                                                                                                                                                 |

|          |      | 4.2.1                   | Scheduling                                                                                                                                      |

|              |                                      | 4.2.2 Signalling                                               | 29        |  |  |  |

|--------------|--------------------------------------|----------------------------------------------------------------|-----------|--|--|--|

|              |                                      | 4.2.3 Feasibility Analysis                                     | 29        |  |  |  |

|              | 4.3                                  | Interrupt Handling                                             | 31        |  |  |  |

|              |                                      | 4.3.1 Race-condition risks                                     | 31        |  |  |  |

| 5            | Пез                                  | vice Drivers                                                   | <b>34</b> |  |  |  |

| U            | 5.1                                  | USART                                                          | 34        |  |  |  |

|              | 0.1                                  | 5.1.1 Code example                                             | 34        |  |  |  |

|              | 5.2                                  | Universal Serial Bus                                           | 35        |  |  |  |

|              | 0.2                                  | 5.2.1 Code example                                             | 35        |  |  |  |

|              | 5.3                                  | The routing network and Montium processors                     | 36        |  |  |  |

|              | 0.0                                  | 5.3.1 Configuration of the montium lanes                       | 36        |  |  |  |

|              |                                      | 5.3.2 Code example                                             | 37        |  |  |  |

|              |                                      |                                                                | 01        |  |  |  |

| 6            |                                      | amples                                                         | 39        |  |  |  |

|              | 6.1                                  | Writing Applications                                           | 39        |  |  |  |

|              |                                      | 6.1.1 Tasks, Signals, Pipes, Resources                         | 39        |  |  |  |

|              |                                      | 6.1.2 System Calls                                             | 43        |  |  |  |

|              | 6.2                                  | Tools                                                          | 43        |  |  |  |

|              |                                      | 6.2.1 Stack usage prediction                                   | 43        |  |  |  |

|              |                                      | 6.2.2 Dynamic Application Loading                              | 44        |  |  |  |

|              |                                      | 6.2.3 Second Stage USB Boot-loader                             | 45        |  |  |  |

| 7            | $\mathbf{Rec}$                       | commendations                                                  | <b>47</b> |  |  |  |

|              | 7.1                                  | Memory management                                              | 47        |  |  |  |

|              |                                      | 7.1.1 Memory Allocation Algorithm                              | 47        |  |  |  |

|              |                                      | 7.1.2 Splitting memory in kernel-memory and application-memory | 47        |  |  |  |

|              | 7.2                                  | Scheduler                                                      | 47        |  |  |  |

|              |                                      | 7.2.1 Other scheduling algorithms                              | 47        |  |  |  |

|              | 7.3                                  | Drivers                                                        | 48        |  |  |  |

|              |                                      | 7.3.1 Usage of PDCs                                            | 48        |  |  |  |

|              |                                      | 7.3.2 Montium                                                  | 48        |  |  |  |

|              |                                      | 7.3.3 Implement more drivers                                   | 48        |  |  |  |

|              | 7.4                                  | Usage of Cyclic Asynchronous Buffers                           | 49        |  |  |  |

| 8            | Cor                                  | nclusions                                                      | 50        |  |  |  |

| U            | 001                                  |                                                                | 00        |  |  |  |

|              | Bib                                  | liography                                                      | 51        |  |  |  |

| Α            | Acronyms 53                          |                                                                |           |  |  |  |

| в            | 3 GCC Cross-compiler build script 55 |                                                                |           |  |  |  |

| $\mathbf{C}$ | C Kernel API 57                      |                                                                |           |  |  |  |

| D            | D Example Code 63                    |                                                                |           |  |  |  |

|              |                                      | -                                                              |           |  |  |  |

# Chapter 1 Introduction

A kernel is the basis for every operating system of a computing platform. It is a program that acts as an intermediary between between a user of a computer and the computer hardware. It supports basic functions such as memory management, hardware interrupt handling and task-switching. Furthermore, it gives an application an environment in which it can run, has support for inter-task communications, divides resources between the running applications and handles the communication with hardware.

Compared to generic kernels (e.g. in Windows, Linux), real-time kernels not only just divide the available resources between the running applications, but can also guarantee that the application will run with timely guarantees, under the assumption that the application respects its real-time constraints.

In a real-time system, an application is split in one or more tasks. Each task can have a set of runtime constraints, such as task duration, task deadline and task resource usage.

There are two most common types of real-time systems. Hard real-time systems, where missing such a deadline can result in disaster, and soft real-time systems, where missing a deadline only results in a performance loss.

#### 1.1 Problem description

Within the Embedded Systems group at the University of Twente, there is a need for such a soft real-time kernel. Most projects currently use the Dimitri or eCos kernels. These kernels offer too restricted scheduling possibilities or have a large memory footprint (more than 100 KB) and unnecessary overhead due to their supported features like a runtime reconfigurable hardware abstraction layer with excessive use of callback functions and in-kernel debugging.

The aim for this project is to have a lightweight real-time kernel for the platform that is currently used most at the Embedded Systems group, that is the Basic Concept Verification Platform (BCVP). The BCVP board has two ARM9 processors, several timers, a serial port, an USB device-port and several more peripherals. The BCVP also has an FPGA board, which can be used for emulating a Montium processor [6]. The kernel we are designing will be used for streaming real-time applications, such as MPEG4 decoding, and test-applications for the Montium environment. The kernel needs to be able to control the serial port, the USB device-port and the Montium processor, while keeping a low memory footprint (less than 50 KB). Features which this kernel should have are memory allocation, advanced interrupt handling, flexible real-time Quality of Service (QoS) scheduling (preferably EDFI) and dynamic task insertion and deletion.

#### **1.2** Document overview

Chapter 2 will describe existing work. Current kernel implementations will be discussed. An introduction in the BCVP architecture is given. Furthermore, fast interrupt handling by using impulse handlers and the EDFI scheduling algorithm is described.

In Chapter 3, the design of the kernel itself will be described. What does the application interface, that we have in mind, look like. Which adaptations do we have to make to the given theories and which problems do we expect to have.

Chapter 4 describes implementation issues. What are the trade-offs between the possible choices. Why did we choose for a specific implementation.

Chapter 5 gives an overview of the currently available device drivers in BasOS. It also describes how these devices can be accessed from an application.

In Chapter 6, the interaction with the kernel is described. What should an application implement. How is a dynamic task specified and how is it activated within a running kernel. Chapter 7 will give a list of all recommendations.

Finally, the conclusions can be found in Chapter 8.

### Chapter 2

# State of the Art

This chapter gives an overview of previous work. It describes existing kernel implementations, the Basic Concept Verification Platform, scheduling techniques and interrupt handling.

#### 2.1 Current implementations

There are many existing real-time and non-real-time kernels available. As stated in Chapter 1, every kernel has its own characteristics. Most kernels are not written with few memory in mind and often do not have support for real-time tasks. Others are, but are often optimised for one or several pre-defined task-sets.

Within the 4S-project [11] a long list of kernels have been evaluated. From this list, the most interesting kernels have been selected. The criteria we used for selecting these kernels were:

- Is the source available.

- Does the kernel have support for the ARM architecture.

- Are there drivers available for the BCVP peripherals.

- Does it have a low memory footprint. (less than 50 KB)

- Does it have support for real-time scheduling.

None of the selected kernels matched all criteria, but four kernels were close enough. We will have a closer look at these four kernels.

#### 2.1.1 DCOS

DCOS [4] is a lightweight kernel, written for the MSP430 processor. It has been developed by Tjerk Hofmeijer at the University of Twente. The kernel uses EDFI scheduling [5] and first-fit memory heap allocation. It has a low memory footprint. It uses impulses [7] for fast interrupt handling. Unfortunately, the only implementation available is for the 16-bit MSP430 and it only has support for the EDFI scheduling algorithm. (see Section 2.4.1 for a description of EDFI scheduling)

#### 2.1.2 eCos

eCos [14] is a rather complete kernel. It is developed within the open source community and there is an implementation available for the BCVP platform. The kernel has USB, ethernet, serial and flash support. Unfortunately, the kernel does not have support for real-time tasks. Also, the kernel is not very memory efficient.

#### 2.1.3 TinyOS

TinyOS [17] is a very lightweight kernel developed for wireless embedded sensor networks. It was initially developed by the U.C. Berkeley EECS Department. Currently, numerous groups are actively contributing code to the project. TinyOS uses a pre-compiled set of tasks, which makes it less suitable for dynamic task loading and task migrations. There is no ARM support for TinyOS.

#### 2.1.4 RTlinux

RTlinux is one of the more familiar real-time kernels. It is built on top of (or actually below) Linux. Therefore, when using this kernel, running Linux is also necessary, which needs many resources. An advantage is that interaction with Linux facilitates writing tasks for this platform. Due to its large footprint, this kernel is less interesting than the previously discussed kernels.

#### 2.1.5 Summary

None of the described kernels is flexible enough to suit as a basis for our kernel. Adapting one of these already existing kernels would take more time than partially redesigning and reimplementing it. When we would choose to adapt such a kernel, this would lead to matching ideas that are not well suited to live together.

Instead, we prefer to re-use only parts of the code of the existing kernels. For example, the EDFI scheduling and heap management from the DCOS kernel and the eCos BCVP driver implementations are interesting enough to be used in our own kernel.

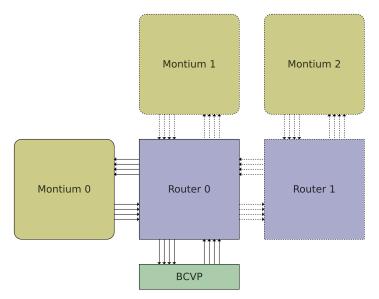

#### 2.2 The Basic Concept Verification Platform

We are using the BCVP (seen in Figure 2.1) as the development platform for our kernel. In the 4S-project [11], it is used for building applications in the field of Digital Radio Mondiale (DRM) and MPEG4 decoding. The 4S-project mission statement is:

4S will realize flexible and reconfigurable building blocks to pave the way for new consumer devices and applications like digital information broadcasting, ambient intelligence devices and 3G/4G multimedia terminals.

Eventually, the BCVP will be replaced by the *Highly integrated Concept Verification Platform* (HiCVP), but since the HiCVP is not available yet, the BCVP is the best alternative. There are only a few small changes between the BCVP and HiCVP. On the BCVP there are two ARM processors available. On the HiCVP there is just one ARM processor. Furthermore, peripherals use different memory addresses and interrupt vectors.

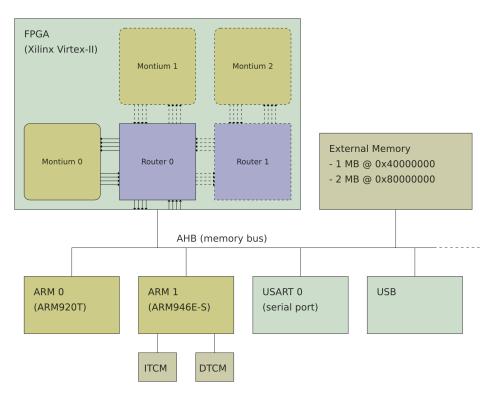

Figure 2.1: The Basic Concept Verification Platform (BCVP)

Figure 2.2: Schematic overview of the BCVP

A simplified schematic overview of the BCVP is given in Figure 2.2. The BCVP has two ARM processors, the ARM920T (on the BCVP known as ARM0) and the ARM946E-S (on the BCVP known as ARM1). Both processors can access all peripherals by using the memory bus. Only the currently used peripherals are shown. We will give a description of all given blocks.

#### $\mathbf{ARM0}$

The ARM0 (ARM920T) processor is one of the two processors available on the BCVP. On boot, the ARM0 processor is disabled.

#### $\mathbf{ARM1}$

The ARM1 (ARM946E-S) processor is the second processor available. On boot, this processor starts the *RedBoot* application, found in flash memory. RedBoot [15] provides a simple command-line interface for loading other applications.

#### ITCM

Instruction Tightly-coupled Memory. The ITCM is only accessible from ARM1 and has a size of 32 KB.

#### DTCM

Data Tightly-coupled Memory. The DTCM is only accessible from ARM1 and has a size of 64 KB.

#### External memory

The BCVP has 3 MB of external memory. One block of 1 MB is available for ARM0, but can also be accessed by ARM1 and one block of 2 MB is available for ARM1 (ARM0 cannot access this memory).

#### USART0

Universal Synchronous Asynchronous Receiver Transmitter. In total, three USARTS are available. The BCVP has one serial port available, which can be controlled via USART0. (the other two USARTs are used for communications inside the BCVP board)

#### $\mathbf{USB}$

USB Device Peripheral. This peripheral acts as a USB device on the USB bus.

#### FPGA

There are two variants of the BCVP. One has an FPGA Virtex-II 3000 and the other an FPGA Virtex-II 8000. An FPGA is configurable hardware; it emulates one or more Montium processors, its Hydra CCU and a routing network. (see the descriptions below)

The Virtex-II 3000 can only emulate one router and one Montium, while the Virtex-II 8000 can emulate two routers and three Montiums.

#### Routers

The routing network routes all communication between the BCVP and Montiums and between the Montiums itself. The routing network is a connection oriented switch for Montium processors. [6]

#### Montium

The Montium processor [6] is an energy-efficient, reconfigurable processor, which has been developed at the University of Twente. It is optimised for highly regular computations.

The BCVP emulates the Montium tiles by using an FPGA, the planned HiCVP will have four Montium tiles.

#### Hydra CCU

The Hydra CCU (Hydra Communication and Control Unit) [6] is the interface which communicates with the Montium processors. It can load new code into the Montium chips, read and write parameter blocks, and start and stop the Montium processor.

The BCVP also has a MultiICE debugging interface available, but this interface caused huge system call overhead and is therefore not used anymore.

#### 2.2.1 The ARM Architecture

On the BCVP, the ARM946E-S (in BCVP documentation often referred to as ARM1) is always online. It can be debugged via the JTAG interface. Therefore development has mainly taken place using this CPU.

Compared to the ARM946E-S, the ARM926EJ-S (the ARM processor that is available on the HiCVP) is quite similar. In addition to the ARM946E-S, it has support for running Java byte-code and has support for virtual memory.

A short introduction in the ARM architecture will now be given. (see the ARM reference documentation [12] for a more complete specification)

#### **ARM CPU-Modes and Exceptions**

The ARM architecture has 7 CPU-modes and 16 general-purpose registers, including the program counter register. Some registers are "banked", which means that these registers are masked by a CPU-mode specific register. Every CPU-mode has its own stack pointer. (see Table 2.1 for all registers and CPU-modes)

| System                  | Fast Interrupt | Supervisor  | Abort      | Interrupt  | Undefined     |

|-------------------------|----------------|-------------|------------|------------|---------------|

| / User $ $ (FIQ) $ $ (S |                | (SVC)       | (ABT)      | (IRQ)      | (UND)         |

| r0                      | r0             | r0          | r0         | r0         | r0            |

| r1                      | r1             | r1          | r1         | r1         | r1            |

| r2                      | r2             | r2          | r2         | r2         | r2            |

| r3                      | r3             | r3          | r3         | r3         | r3            |

| r4                      | r4             | r4          | r4         | r4         | r4            |

| r5                      | r5             | r5          | r5         | r5         | r5            |

| r6                      | r6             | r6          | r6         | r6         | r6            |

| r7                      | r7             | r7          | r7         | r7         | r7            |

| r8                      | r8_fiq         | r8          | r8         | r8         | r8            |

| r9                      | r9_fiq         | r9          | r9         | r9         | r9            |

| r10                     | r10_fiq        | r10         | r10        | r10        | r10           |

| r11                     | r11_fiq        | r11         | r11        | r11        | r11           |

| r12                     | r12_fiq        | r12         | r12        | r12        | r12           |

| r13                     | r13_fiq        | $r13\_svc$  | $r13\_abt$ | r13_irq    | $r13_{-}und$  |

| r14                     | r14_fiq        | $r14\_svc$  | r14_abt    | r14_irq    | $r14$ _und    |

| r15                     | r15            | r15         | r15        | r15        | r15           |

| CPSR                    | CPSR           | CPSR        | CPSR       | CPSR       | CPSR          |

|                         | SPSR_fiq       | $SPSR\_svc$ | $SPSR_abt$ | $SPSR_irq$ | $SPSR_{-}und$ |

Table 2.1: Available ARM registers

All CPU-modes except for the user mode are privileged CPU-modes. In these modes, the task can access CPU-specific registers (e.g. for configuring memory protection or changing the CPU-mode).

The ARM architecture also specifies seven exception vectors, normally placed at memory offset 0. These exceptions are used for handling a soft reset, an error or an interrupt. When such an exception is called, the processor switches to the exception's CPU-mode to keep the user's registers intact. In Table 2.2 an overview is given of all exceptions and their CPU-mode.

| Address    | Exception             | CPU-mode             | Description                     |

|------------|-----------------------|----------------------|---------------------------------|

| 0x00000000 | Reset                 | Supervisor (SVC)     |                                 |

| 0x00000004 | Undefined instruction | Undefined (UND)      |                                 |

| 0x0000008  | Software interrupt    | Supervisor (SVC)     | System calls                    |

| 0x0000000c | Instruction abort     | Abort (ABT)          | Read-error on instruction-fetch |

| 0x00000010 | Data abort            | Abort (ABT)          | Read- or write-error            |

| 0x0000018  | Interrupt             | $\operatorname{IRQ}$ |                                 |

| 0x0000001c | Fast interrupt        | FIQ                  |                                 |

Table 2.2: ARM Architecture Exception Vectors

#### 2.2.2 Memory Layout

The BCVP has a total of 3 MB RAM available. The ARM920T (ARM0) can only access 1 MB, the ARM946E-S (ARM1) can access all memory. All peripherals use memory-mapped IO, as is common on ARM architectures. Most are available above address **0xf0000000**. See Table 2.3 for the BCVP memory layout.

Interesting to note is that the internal memory block contains two Tightly-coupled Memory (TCM) blocks. These blocks can be accessed more quickly than the external memory. One block with a size of 32 KB is optimised for instructions (the ITCM) and the other, which has a size of 64 KB, is optimised for data (the DTCM). If the kernel is small enough, placing the code in TCM will yield an interesting performance gain.

| Address             | Description     |  |  |

|---------------------|-----------------|--|--|

| 0x00000000          | Internal memory |  |  |

| 0x30000000          | Montium Hydra   |  |  |

| 0x40000000          | 1 MB RAM (ARM0) |  |  |

| 0x50000000          | Flash memory    |  |  |

| 0x80000000          | 2 MB RAM (ARM1) |  |  |

| 0 x f 0 0 0 0 0 0 0 | Peripherals     |  |  |

Table 2.3: BCVP physical memory layout

#### 2.3 Impulse handling

In a single processor environment, it is in general preferred to handle interrupts in an interrupt disabled state. When updating various kernel variables from an interrupt handler, it should be guaranteed this variable cannot be changed by another interrupt handler. On the other hand, interrupts could be left in a disabled state, but this might be a risk for interrupt handlers that need to react quickly.

A way to solve this problem is by using impulse handling [7]. The interrupt handler is then split in two halves. The first half, directly called on interrupt and still in interrupt-disabled state, can acknowledge the interrupt and check whether the second half should be run. If the second half should run, a flag is set.

When the first half has finished processing, it checks whether there are pending interrupts. If there are interrupts waiting and the impulse handler is not already active, the impulse handler is flagged as active, the processor is set in interrupt-enabled state and the delayed second half handlers will be processed with a specific priority. By handling the pending interrupts sequentially, only one handler can be active at a time. A handler can then safely update internal kernel variables without the risk of a second handler reading or updating the same resource.

Since the processor is in interrupt-enabled state while handling the second half handlers, it is possible that a new pending interrupt will arrive. The already running impulse handler will pick this up and the handling works as expected.

After all second half handlers have been handled, the impulse handler is flagged as inactive, the processor is set in interrupt-disabled state and the interrupt handler will return. The interrupt-handler pseudo-code is as follows:

```

interrupt:

handle_interrupt_first_half();

if ( impulse_bits_set && ! impulse_handler_running )

{

/* run impulse handler */

impulse_handler_running = true;

enable_interrupts();

while( delayed_interrupt_waiting() )

{

handle_delayed_interrupts();

}

disable_interrupts();

impulse_handler_running = false;

}

interrupt_return; // enable interrupts, restore CPU-mode and return

```

#### 2.4 Real-time Scheduling

Assume an application with a task-set  $\Omega$  as given in Table 2.4. There are four tasks (a task has symbol  $\tau_i$ , with  $1 \leq i \leq 4$ ) and each task has its own relative deadline  $(D_i)$ , period  $(T_i)$ , runtime  $(C_i)$  and shared resources. Every  $T_i$  time units, the task  $\tau_i$  is released, after which it has  $D_i$  time units to complete its task. The release time of a task of invocation j of  $\tau_i$  is  $r_i^j$ . Then the absolute deadline of this release is  $r_i^j + D_i = d_i^j$ .

The definition of a resource, given by Butazzo [3, page 181]: "A resource is any software structure that can be used by a process to advance its execution. Typically, a resource can be a data structure, a set of variables, a main memory area, a file, or a set of registers of a peripheral device."

In our example, there are two resources, A and B. When a task needs exclusive use of a resource, the resource is denoted in uppercase. When a task allows sharing of the resource, the resource is denoted in lowercase. For instance, reading from a memory block can be shared between tasks, but writing to this memory block should be done exclusively by one task at a time.

The inherited deadline  $\Delta_i$  is the smallest deadline interval of a task with which  $\tau_i$  shares an exclusive resource. For instance, task 3 shares resource A with task 1 and 2. Both task 1 and 2 need exclusive use of the resource. Task 3 inherits the smallest deadline interval, which is the deadline of task 1.

| Ω        | $D_i$ | $T_i$ | $C_i$ | $\Delta_i$ | Shared resources |

|----------|-------|-------|-------|------------|------------------|

| $\tau_1$ | 11    | 19    | 2     | 11         | $\{A\}$          |

| $\tau_2$ | 19    | 23    | 5     | 11         | $\{AB\}$         |

| $	au_3$  | 25    | 31    | 7     | 11         | $\{a\}$          |

| $	au_4$  | 30    | 37    | 11    | 19         | $\{B\}$          |

Table 2.4: A task-set  $\Omega$

#### 2.4.1 Earliest Deadline First with deadline Inheritance (EDFI)

There are various real-time scheduling algorithms, differing in performance, complexity and applicability. The most common algorithms are compared in [3] on pages 75 and 107. One of the more interesting scheduling algorithms is Earliest Deadline First with deadline Inheritance (EDFI), described in [5]. EDFI is an extension on Earliest Deadline First (EDF), which gives us the possibility to control shared resource locking from within the scheduler itself (this form of real-time tasks is also known as real-time transactions). The EDFI algorithm is, just as the EDF algorithm, lightweight and gives good results on generic tasks.

We give a short introduction on how EDFI scheduling works. A task-set example can be found in Table 2.4:

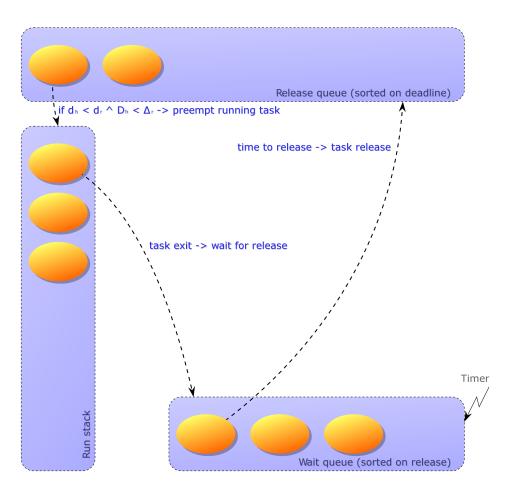

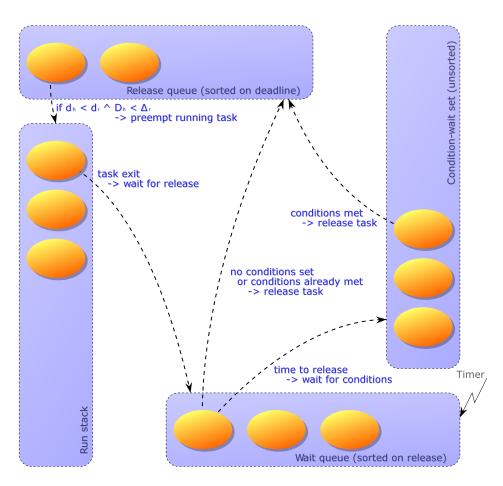

The EDFI scheduler (see Figure 2.3) has two queues, the wait and released queue, and one run stack, all ordered to absolute deadline (earliest deadline first). Every task is periodically released (every  $T_i$  time units) from the wait queue into the released queue.

When a task at the head of the released queue ( $\tau_h$ ) has an earlier deadline than the currently running task ( $\tau_r$ ) and the absolute deadline ( $D_h$ ) is smaller than the inherited deadline of the currently running task ( $\Delta_r$ ),  $\tau_h$  will preempt  $\tau_r$  and become the new running task. (In short, preemption will take place when  $d_h < d_r \land D_h < \Delta_r$ )

When a task finishes or reaches its deadline, the task is removed from the run stack (or released queue) and inserted back into the wait queue, waiting for its next release.

#### 2.4.2 EDFI Feasibility Analysis

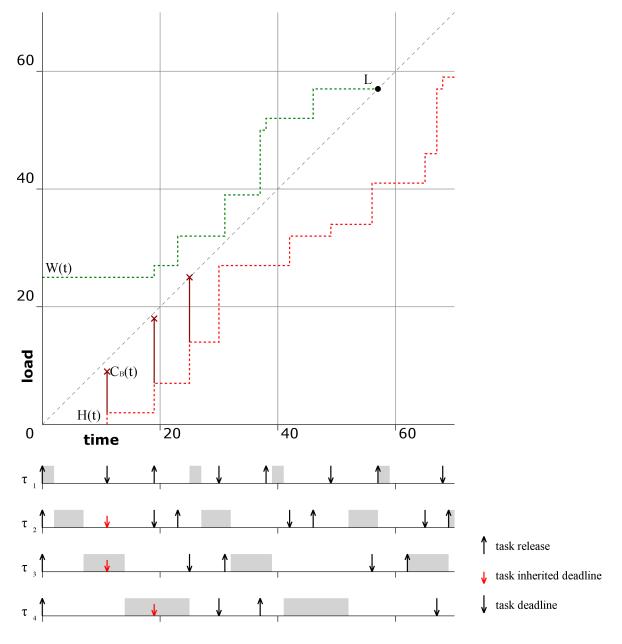

For determining whether a given task-set is feasible, we have to examine the processor demand H(t), the workload W(t) and the blocking load  $C_B(t)$ . H(t) represents the total amount of CPU time that must be available between 0 and t for  $\Omega$  to be schedulable to make all deadlines met so far. W(t) represents the cumulative amount of CPU time that is consumable by all task releases between time 0 and t. [5, page 3]

$C_B(t)$  is the possible blocking load, caused by the shared resources. L is the point where W(t) = t. (the point where the CPU first becomes idle)

The task-set  $\Omega$  is feasible [5] if

$$\forall t \in \langle 0, L] : H(t) + C_B(t) \le t.$$

The feasibility analysis of a task-set can be represented in a figure. Figure 2.4 shows an analysis of the task-set given in Table 2.4. The diagonal in the graph represents the amount of work done. The vertical distance between the W(t) and the diagonal represents the amount of work still to do in released tasks. At point L, which is the point where the diagonal touches the W(t) function, there is no more work to do and the system becomes idle. The H(t) function represents the amount of work that must be finished. If H(t) crosses the diagonal, then more work would have to be finished than there is time available. The  $C_B(t)$  represents the maximum potential blocking load, which is given by  $C_B(t) = max_{\Omega}\{C_{\tau} | \Delta_{\tau} \leq t < D_{\tau}\}$ . The schedulability analysis tracks W(t) and H(t) until either W(t) touches the diagonal or  $H(t) + C_B(t)$  crosses it. If  $H(t) + C_B(t)$  crosses the diagonal, the task set is not schedulable. If W(t) touches before  $H(t) + C_B(t)$  could cross, the task set is feasible.

Figure 2.3: EDFI Scheduler: wait queue, release queue and the run stack

Below the graph, the task bars are shown with a possible scheduling. An upward arrow represents the release of the task. A downward arrow represents the deadline of the task. A small downward arrow represents the inherited deadline of the task. The blocks represent a possible scheduling of the given task-set.

Figure 2.4: EDFI feasibility analysis of the task-set in Table 2.4

### Chapter 3

# Kernel Design

The emphasis of this chapter is on the design of the kernel. Questions are: what interface should a kernel offer to its applications. Which design decisions have been made.

#### 3.1 Application Interface

A processor should run applications. The interaction with the kernel should be simple and minimal. The kernel is to provide a convenient interface between the computer hardware and the applications. The main tasks of the kernel are scheduling, memory management, interrupt handling and communication with devices.

#### 3.1.1 Tasks

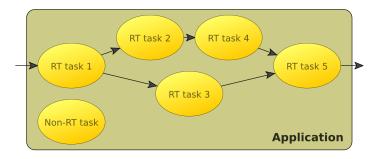

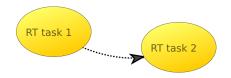

Every application consists of a number of tasks. Every real-time task has its own set of real-time constraints, which we already mentioned in Section 2.4 (relative deadline, used processor time, the period between two consecutive task instances, shared resources, etc.). A task often responds to a certain input, after which it produces an output. Especially in streaming applications, this can result in data-flows as given in Figure 3.1. One task receives input from an external input. When the task is released, it processes this input and sends the result to one or more other tasks.

One of the ideas of BasOS is to optimise this process by partially moving the data streams into the kernel and let the scheduler use this knowledge to minimise delays. These techniques will be described further on in this section.

Figure 3.1: Tasks: an application can be seen as a number of tasks

#### Non real-time tasks

For our target applications, we in general prefer real-time tasks. However, for management and configuration we can also use non-real-time tasks. Reasons for using non-real-time tasks are:

- Non-real-time tasks will not be terminated when they miss their deadline, because there is no deadline.

- In a non-real-time task, we can wait for events to take place. (e.g. wait until data is available in a pipe)

- Using dynamic memory allocation cannot give us real-time guarantees at the moment. If we use dynamic memory allocation in a real-time task, a deadline could result in memory leakage.

- When configuring a new set of real-time tasks, the kernel needs to dynamically allocate new task-structures, pipe-structures, etc. This depends on dynamic memory allocation, which cannot be done real-time.

For these tasks, the kernel uses a simple TDMA scheduling algorithm, which runs in the slack time of the real-time scheduler. With this scheduling model, the scheduler sequentially gives every non-real-time task a time-slice of a predefined amount of time. When a real-time task is activated, the non-real-time task is preempted. On return, the non-real-time scheduler continues with the preempted task, which then runs for the time left over in its current time-slice.

#### 3.1.2 Signals and conditions

In conventional EDFI scheduling a task is periodically released. When dealing with input that is not always immediately available, as in a streaming-oriented environment, it is preferable to activate a task when all conditions for activating are met.

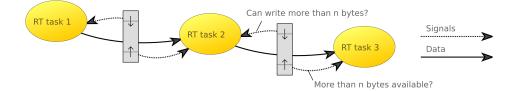

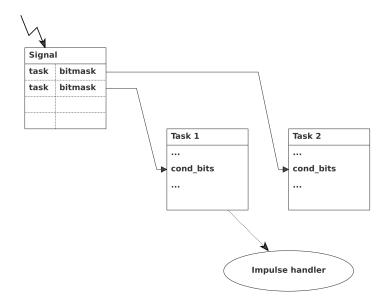

A condition is met when the kernel has received a signal for a specific task. A signal can be received from other tasks, external events or by kernel logic like pipes and timers. (see Figure 3.2)

Every task-structure has a bitmask, which keeps track of the currently active conditions. When a task receives a signal, the kernel updates the bitmask in the task-structure and when all defined conditions have been met, the task can be released from the condition-wait set<sup>1</sup>. A signal can be sent to a task at any given moment. When a task is released, the set of met conditions is cleared. This gives the kernel the ability only to start a task when there is input available and there is space available to write its output.

Figure 3.2: Signals: activating a task

<sup>&</sup>lt;sup>1</sup>The condition-wait set will be described in Section 3.3.

#### Instance-independent conditions

When one task has written data into a pipe and the kernel has activated the second task by sending a signal, it does not necessarily mean that the pipe is empty after the second task is finished.

As described before, the conditions are met per task instance. To solve this problem, we introduce instance-independent conditions. When a task is released, all conditions except for the instance-independent conditions are cleared. The instance-independent conditions will stay active until someone sends a signal-clear.

#### 3.1.3 Pipes

There are various ways to send data from one task to another. You can use shared memory and implement your own communications channel or use pipes. (see Figure 3.3)

Pipes internally have a circular buffer of which the size is specified on creation. Tasks can send data to another task (or device) by writing into a pipe. The pipe-object itself then takes care of signalling other tasks when sufficient data has been written into the pipe. In the pipe-object two signals are available: the not-full signal and the not-empty signal. The not-full signal is sent when data is read from the pipe and the amount of **free** space becomes more than  $wr_threshold$  bytes. The not-empty signal is sent when data is written to the pipe and the amount of **used** space becomes more than  $rd_threshold$  bytes. These thresholds can be configured dynamically by updating the  $rd_threshold$  and  $wr_threshold$  fields<sup>2</sup>.

Figure 3.3: Pipes: data transfer from one task to another

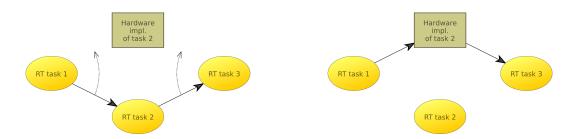

To keep the kernel interface as generic as possible, all data-streams from and to the hardware have been implemented as pipes. This gives us the same flexibility as we have when using a pipe for sending data between tasks. Also, if we are switching between a software implementation of a task and a hardware implementation or Montium implementation, the task sending data to this task and the task receiving data from this task do not need another interface.

For example, Figure 3.4 shows an implementation switch. If one would dynamically switch over to the hardware implementation of task 2, one could remove task 2 from the scheduler and reconnect the pipes to and from this task to the hardware implementation.

Switching between two implementations can be done by giving the first task a pointer to the new input pipe. When all data has been read from the old pipes, these structures can be deleted. The application itself is responsible for cleaning up the old structure of pipes and tasks. The application also needs to solve the timing difference (glitch) between the old and new implementations.

<sup>&</sup>lt;sup>2</sup>Changing the pipe-structure fields is discussed more in-depth in Chapter 6.

Figure 3.4: Rerouting pipes to an alternative implementation

#### 3.2 Interrupts

When an interrupt is received by the ARM processor, the kernel starts the interrupt handler, which will handle the first part of the interrupt. Depending on what should be done by the interrupt handler, the handler can handle the complete interrupt, send a signal to one or more tasks or activate an impulse handler<sup>3</sup> to handle the second part of the interrupt.

#### 3.3 Streaming-oriented Scheduling

The EDFI real-time scheduler [5] from Section 2.4.1 works with two queues and a stack. Every task is released periodically, independent of whether it has anything to do. We have based our model on this periodic task model and adapted it in such a way it can also be used for aperiodic tasks.

#### 3.3.1 Delaying the task release

As described in Section 3.1.2, whether a task has anything to do is encoded in its conditions. While not all conditions have been met, it is a waste of time to release the task, only to find out that the task cannot do anything yet.

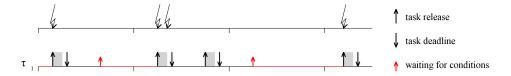

We can however delay the scheduling when not all conditions for the task to release have been met. Where a task should be released in the normal EDFI scheduler, it is now put on hold while not all conditions have been met. For example, the first task-bar in Figure 3.5 describes a task that is scheduled with EDFI. The second task-bar describes a task which is delayed at its third release.

Figure 3.5: EDFI scheduling without signal-delaying and with signal-delaying

Baruah et al.[1] proved the following theorem:

"If for any interval with length L, all work load offered during [0, L] can be resolved before or at L, then this can be concluded for any arbitrary time interval [t, t+L]."

<sup>&</sup>lt;sup>3</sup>See Section 2.3 for a discussion of the impulse handler.

Jansen et al.[5, page 3] commented on this:

"Therefore all tasks in  $\Omega$  are released simultaneously at t = 0, in which case they will produce the largest response time. If the tasks in  $\Omega$  can make their deadlines from t = 0, they can make their deadlines from any point in time."

This means that tasks can be delayed without affecting the result of the EDFI schedulability analysis described in Section 2.4.2.

#### 3.3.2 Aperiodic tasks

With this same technique, we can also implement aperiodic tasks. (Figure 3.6) An aperiodic task is scheduled as if it is a periodic task, whereby the task's period is the minimum time between two instances of the task, and the trigger to activate the task is modelled as a condition for the task to run. The worst scenario for such an aperiodic task, the scenario wherein the task is continuously activated, then resembles the scheduling of a periodic task.

Figure 3.6: EDFI scheduling on aperiodic task

#### 3.3.3 The scheduling model

In the scheduling algorithm, this delay is implemented by introducing a fourth group, the condition-wait set (see Figure 3.7). This set is inserted between the wait queue and the release queue. When a task starts a new period, the task is removed from the wait queue and inserted in the condition-wait set. When all conditions have been met, the task is released and inserted into the release queue.

#### 3.3.4 The scheduler impulse handlers

The scheduler currently uses four impulse handlers. A brief description will be given for every impulse handler. The handlers are discussed from high priority to low priority.

#### "Task received signal"

This impulse handler checks the condition-wait set for tasks which have all their conditions met. These tasks will be removed from the condition-wait set and inserted into the released queue. The impulse handler will then activate the "Schedule" impulse handler.

#### "Task exit"

The currently running task called the SYS\_exit() system-call. The current task is removed from the run stack and inserted into the wait queue. The impulse handler will then activate the "Schedule" impulse handler.

Figure 3.7: EDFI Scheduler, extended with a condition-wait set

#### "Received timer interrupt"

This handler is called when a task can be released from the wait queue or when a deadline has been met. The timers within the scheduler are updated. When a task in the release queue or run stack reaches its deadline, the task is moved to the wait queue. When a task from the wait queue reaches the end of its current period, the task moves to the condition-wait set or released queue. When the impulse handler is finished, it will activate the "Schedule" impulse handler.

#### "Schedule"

This impulse handler checks whether the currently running task (if any) should be preempted by the task on the head of the release queue.

If there are no real-time tasks available, the first task on the tdma queue is activated if it still has time left in its time-slice. When the end of the time-slice is reached, the task will be placed at the end of the tdma queue with a new time-slice.

### Chapter 4

# Implementation

This chapter describes the decisions and optimisations made in the implementation of the kernel.

#### 4.1 Memory Management

As described in Section 2.2.2, the BCVP has 2 MB at **0x8000000** available for application code running on ARM1. We only can use it from approx. address **0x80008000**, because the RedBoot boot-loader uses the memory in between. If we are using the USB ELF-loader that is described in Section 6.2.3, we can use the full 2 MB.

#### 4.1.1 Heap Memory

All memory that initially is not in use by the kernel itself is defined as heap memory. The kernel can use the heap to dynamically allocate and de-allocate memory.

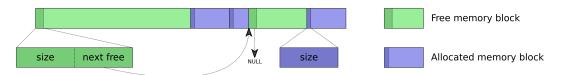

A widely used heap memory algorithm is the first free shrink algorithm [10] [4, pg. 59-61]. On initialisation, the heap is one big free memory block, but when time passes, it becomes fragmented. The kernel keeps a linked list of free memory blocks, and when memory is needed, it searches this list for the first block that fits the size request.

A memory block header starts with a word specifying the size of the block, including the size of the header. When the memory block is free, this word is followed by a pointer to the next free memory block. The last free memory block header contains a NULL-pointer. (see Figure 4.1)

Figure 4.1: Heap memory: free memory blocks and allocated memory blocks

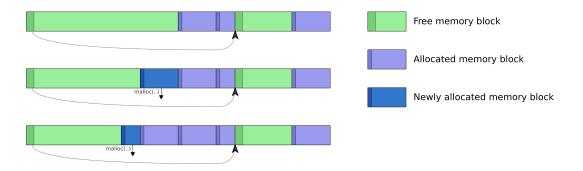

#### The algorithm used for allocating a block (Figure 4.2):

- Enlarge the requested size to a word-boundary and make sure that the required memory block can contain a free memory block header. (guarantee that there is enough space when we free this block)

- Start searching for a free memory block that is large enough to hold the requested memory.

- Split the block in two parts. The first part is the new free block and the second part is the allocated block. Only the size of the memory blocks needs to be updated, the linked list of free memory blocks doesn't change.

- Return the pointer to the data-part of the newly allocated memory block.

Figure 4.2: Allocating memory: two memory allocations

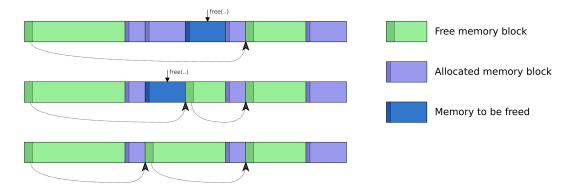

#### The algorithm used for freeing a block (Figure 4.3):

- Search the free memory blocks chain for the last free block before the given pointer. Since the first block in memory is always a free block, such a block is always available.

- Copy the next free pointer from the previous free block header to the current block header. The size the the current block header does not change when it becomes a free block.

- If the previous free block and the new free block are adjacent, merge them to prevent fragmentation of free blocks.

- If the new free block and the next free block are adjacent, also merge them.

As an optimisation on the DCOS implementation [4, pg. 59-61], the block size of a memory block in BasOS always includes the block header structures. When converting allocated memory block to a free memory block, only the linked list of free memory blocks needs to be updated.

#### 4.2 Tasks

As mentioned before, there are two types of tasks: real-time tasks (currently scheduled with the EDFI algorithm) and non-real-time tasks (scheduled with the TDMA algorithm). Both types of tasks use the same task structure, but some fields are used differently.

Figure 4.3: Freeing memory: two memory deallocations. on second free, two free blocks are merged

Every task in BasOS needs a task specification and a task context. The task specification (see Listing 4.1 and Table 4.1) specifies the entry-point, needed stack size, maximum runtime, the initial flags, its deadline, shared resources, etc..

For tasks with a private stack, the stack size is used for allocating enough space on the heap. For tasks with a shared stack, the value is used for guaranteeing that enough stack is available for the task to run.

Note that for non-real-time tasks, the deadline, period and resources fields are ignored. The cputime field is used for a different purpose. It specifies the length of the time- slice for the TDMA scheduler.

```

struct task_specification {

funcptr entry;

u32 stack_size;

u32 deadline;

u32 period;

u32 cputime;

u32 flags;

char *name;

task_resource_ptr *resource_sh;

task_resource_ptr *resource_ex;

};

```

Listing 4.1: The task specification struct

The task context (see Listing 4.2 and Table 4.2) is used for storing the current state of the task. Every task that is not using the shared context object should have a private context. When entering the impulse queue runner, the current task state is stored into the task context and when leaving the impulse queue runner, a new task state is retrieved from the currently active task context.

| entry                                                  | The entry-point of the task                                                |  |  |  |  |  |

|--------------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| stack_size                                             | The max. stack size (in bytes) used by the task                            |  |  |  |  |  |

| <b>deadline</b> The task deadline (in 1/32768 seconds) |                                                                            |  |  |  |  |  |

| period                                                 | The interval at which the task is released (in $1/32768$ seconds)          |  |  |  |  |  |

| cputime                                                | The max. time the task will run (in $1/32768$ seconds).                    |  |  |  |  |  |

|                                                        | For non-real-time tasks, this value specifies the length of the time-slice |  |  |  |  |  |

| flags Specifies the task's type and state:             |                                                                            |  |  |  |  |  |

|                                                        | - TASK_FLAG_RT:                                                            |  |  |  |  |  |

|                                                        | The task is a real-time task                                               |  |  |  |  |  |

|                                                        | - TASK_FLAG_CTXT_SHARED:                                                   |  |  |  |  |  |

|                                                        | The task will share the global task context (global stack)                 |  |  |  |  |  |

|                                                        | - TASK_FLAG_IDLING:                                                        |  |  |  |  |  |

|                                                        | When set, the task is initially inserted in the condition-wait set.        |  |  |  |  |  |

|                                                        | Otherwise, the task is initially inserted in the released queue            |  |  |  |  |  |

| <b>name</b> The name of the task. Used for debugging   |                                                                            |  |  |  |  |  |

| resource_sh                                            | The shared and exclusive resources needed by this task,                    |  |  |  |  |  |

| resource_ex                                            | specified as a pointer to a NULL terminated list                           |  |  |  |  |  |

Table 4.1: Description of all fields in the task specification structure

When a task is started that shares its context with already running tasks, the scheduler pushes the task state of the preempted task onto the shared stack and recycles the context object to use it for the new task. After the task has finished, the original context data is recovered from the shared stack.

```

struct task_context {

u32 cpsr;

u32 pc;

u32 r[15];

#ifdef CONTEXT_MEASURE_RUNTIME

u32 rt_runtime;

u32 rt_lstart;

#endif // CONTEXT_MEASURE_RUNTIME

void *heap_stack;

};

```

#### Listing 4.2: The task context struct

The task object itself (see Listing 4.3 and Table 4.3) contains information about its current state in the scheduler, the used condition bits (see Section 4.2.2 for more detailed information about these bits) and the tasks arguments.

| cpsr                                                        | Saved state of the $CPSR^a$ register                          |  |  |

|-------------------------------------------------------------|---------------------------------------------------------------|--|--|

| <b>pc</b> Saved state of the program counter (r15) register |                                                               |  |  |

| r[15]                                                       | Saved state of the r0 r14 registers                           |  |  |

| rt_runtime                                                  | The total time this context is running (in $1/32768$ seconds) |  |  |

| rt_lstart                                                   | The time when this context was last restarted                 |  |  |

| heap_stack                                                  | Pointer to the allocated memory for the stack                 |  |  |

<sup>a</sup> The Current Program Status Register (CPSR)

Table 4.2: Description of all fields in the task context structure

```

struct task {

struct task_context *context;

u32 stack_base;

struct task *shared_next;

u32 flags;

int use_count;

int absolute;

u32 delta;

const struct task_specification *spec;

u32 cond_bits;

u32 cond_bitmask_in_use;

u32 cond_bitmask_nonsticky;

u32 cond_bitmask_wake;

#ifdef CONTEXT_MEASURE_RUNTIME

u32 rt_runtime;

#endif // CONTEXT_MEASURE_RUNTIME

void *args;

struct task *next;

};

```

Listing 4.3: The task struct

#### 4.2.1 Scheduling

```

static struct task * task_rt_wait_queue;

static struct task * task_rt_cond_wait_set;

static struct task * task_rt_release_queue;

static struct task * task_rt_running_stack;

```

```

Listing 4.4: The four EDFI-scheduler queues

```

As described in Section 3.3, our EDFI scheduler has three queues and one stack. They are implemented as four linked lists. (see Listing 4.4)

| context                          | Pointer to the context object                                        |  |  |

|----------------------------------|----------------------------------------------------------------------|--|--|

| stack_base                       | The stack pointer on task release                                    |  |  |

| shared_next                      | Pointer to the preempted task with the same context object,          |  |  |

|                                  | when sharing contexts                                                |  |  |

| flags                            | Specifies the task's type and state:                                 |  |  |

|                                  | - TASK_FLAG_EXIT:                                                    |  |  |

|                                  | The task has ended                                                   |  |  |

|                                  | - TASK_FLAG_RT:                                                      |  |  |

|                                  | The task is a real-time task                                         |  |  |

|                                  | - TASK_FLAG_DESTROY:                                                 |  |  |

|                                  | The task needs to be destroyed (waiting for $use\_count$ to reach 0) |  |  |

|                                  | - TASK_FLAG_CTXT_SHARED:                                             |  |  |

|                                  | The task will share the global context                               |  |  |

|                                  | - TASK_FLAG_IDLING:                                                  |  |  |

|                                  | The task is waiting in the condition-wait set                        |  |  |

|                                  | - TASK_FLAG_WAITING:                                                 |  |  |

|                                  | The task is blocked. Waiting for a condition                         |  |  |

|                                  | - TASK_FLAG_ACTIVE:                                                  |  |  |

|                                  | The task is added to the scheduler                                   |  |  |

|                                  | - TASK_FLAG_TO_BE_REMOVED:                                           |  |  |

|                                  | The task should be removed from the scheduler                        |  |  |

| use_count                        | The number of references to this task object                         |  |  |

| absolute                         | The activation time relative to the previous task in the             |  |  |

|                                  | linked list or when on the head of the linked list                   |  |  |

|                                  | to the $time\_last\_updated$ variable.                               |  |  |

| delta                            | The inherited deadline                                               |  |  |

| spec                             | A pointer to the task specification structure                        |  |  |

| ${f cond\_bits}$                 | The currently triggered conditions (stored as bitmask)               |  |  |

| ${\rm cond\_bitmask\_in\_use}$   | Bitmask of all used bits                                             |  |  |

| ${\tt cond\_bitmask\_nonsticky}$ | Bitmask of all bits that have to be reset on task release            |  |  |

| ${\bf cond\_bitmask\_wake}$      | Bitmask of all bits that wake a task from its blocking wait state    |  |  |

| rt_runtime                       | The total time this task is running (in $1/32768$ seconds)           |  |  |

| args                             | The argument given to the entry point                                |  |  |

| next                             | Pointer to the next task in the queue or stack                       |  |  |

Table 4.3: Description of all fields in the task structure

#### The wait queue

The wait queue is the queue in which all tasks wait for the moment they can be released. The queue is sorted on earliest release first. The release time can be determined by looking at the left over deadline of the task  $(r_i^j + 1 = r_i^j + T_i = d_i^j + T_i - D_i)$ . From here, a task will move to the condition-wait set.

The time the task can be removed is stored as a cumulative value (over the  $task \rightarrow next$  linked list) in the  $task \rightarrow absolute$  field. The advantage of only storing the incremental value in the linked list is that we only have to update the first task-fields.

#### The condition-wait set

In the condition-wait set, a task will wait until all the task's defined conditions have been met. The set is implemented as a queue, which is not sorted. When all conditions have been met, the internal condition state is cleared, the deadline is activated and the task is inserted into the release queue. If no conditions have been defined for this task, the task will behave strict periodic and skip the condition-wait set.

#### The release queue

Just like the wait queue, tasks in the release queue are sorted, but now by their deadline. The same field  $task \rightarrow absolute$  is used, but now for the cumulative deadline. On every change in the release queue and run stack, the scheduler checks if the head of the release queue (the task with the first deadline) can preempt the task at the head of the run stack. If so, the task will move from the release queue to the run stack.

If a deadline is met before the end of a task, the task immediately moves to the wait queue.

#### The run stack

The run stack contains the currently running real-time task on top and below it all the preempted tasks. Similar to the wait queue and release queue, the field  $task \rightarrow absolute$  is stored as an incremental value. When a task ends or when its deadline is met, the task is removed from the run stack and inserted into the wait queue.

#### 4.2.2 Signalling

Every task (see Listing 4.3) has four variables for storing the signals it is listening to and whether they have been triggered already. Due to the limited length of these field, we can only attach 32 signals to one task.

The cond\_bitmask\_in\_use keeps track of which bits have been used and which haven't. The cond\_bits contain which of these bits have been triggered, cond\_bitmask\_nonsticky tells us which bits need to be reset when a task is inserted into the release queue. The cond\_bitmask\_wake tells us on which bit we are waiting if the task is blocking (only possible in a non-real-time task).

Since the task itself doesn't keep track of the signals it is waiting for, the signal object keeps a list of tasks and its assigned bitmasks. When a signal is triggered, the kernel will loop over the task-list in the signal object and sets and resets the corresponding bits in the cond\_bits in the task object. If all conditions have been met, which is when the cond\_bitmask\_in\_use is equal to the cond\_bits, the 'check task condition' impulse handler (which is a part of the scheduler) is triggered that will insert the task into the release queue. (see Figure 4.4)

Adding a task as a recipient for a signal is done by finding a free bit in the task's *signal\_bitmask\_in\_use* bitmask, mark this bit as 'used' and adding the task to the list of tasks and bitmask pairs in the signal structure.

#### 4.2.3 Feasibility Analysis

Every time a task is added to the scheduler, the scheduler checks whether the new task-set is feasible. In case of a feasible task-set, the new inherited deadlines are copied to the actual

Figure 4.4: Releasing a task: Signal is triggered, task releases impulse handler

tasks and the new task is added to the scheduler.

For testing the feasibility of the new task-set, an abstract task structure is used, see Listing 4.5. The feasibility analyser replays the tasks from time t = 0 to t = L. On every task release, W(t) is checked, and on every task deadline,  $H(t) + C_B(t)$  is checked.

```

struct task_abs {

const struct task_specification *spec;

struct task_abs *next;

struct task *task;

int absolute;

u32 delta;

};

```

Listing 4.5: The abstract task struct, used for testing the feasibility Feasibility-analysis pseudo-code (actually, this code just calculates the H(t), W(t) and  $C_B(t)$ functions as seen in Section 2.4.2):

```

feasibility_analysis(tasks):

H=0; // workload to be resolved

W=0; // workload offered

queue_wait = ();

queue_release = tasks;

t=0; // t_now

loop {

switch (task_next(queue_wait, queue_release, t, C)) {

}

}

```

```

case TASK_RELEASE:

// check offered load before the release

if ((t > 0) && (W <= t)) return FEASIBLE;

W += C;

break;

case TASK_DEADLINE:

H += C;

B = blocking_load(queue_wait, queue_release, t);

// check to be resolved load after the deadline

if (H + B > t) return NOT_FEASIBLE;

}

```

#### 4.3 Interrupt Handling

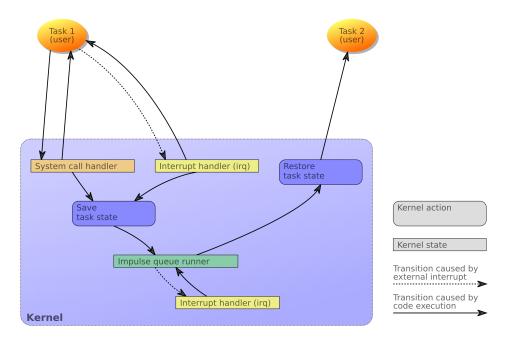

The kernel can be in one of the four states user, syscall, irq, impulse. Normally, the processor is handling a task, thus the kernel resides in user state. When a hardware interrupt arrives at the processor or when the task uses a syscall, the state changes to respectively irq or syscall. When the interrupt or syscall is handled, but there is no need to run an impulse handler, control is returned to the same task.

When there is a need to run an impulse handler, the context of the currently running task is saved and the impulse queue runner is called. When running the impulse handlers, interrupts are in the enabled state. New hardware interrupts thus might interrupt an impulse handler, but the new hardware interrupt will not start a second impulse queue runner. When all impulses have been handled, the context of the newly running task is restored (a task switch might have occurred), and the task will continue.

All these states and transitions between the states can be found in Figure 4.5. Note that hardware interrupts can only occur when the processor is in an interrupt enabled state, which is in the user and impulse state.

#### 4.3.1 Race-condition risks

These kernel states introduce one problem. Since the impulse handlers can be interrupted by a hardware interrupt, it is possible that both the impulse handler and the interrupt handler need to update the same kernel variables.

Normally, one would introduce semaphores or blocking mutexes in the kernel, but we wanted to keep our kernel lightweight, preferably without any possible blocking in the kernel. There are two solutions to this problem. One is to guarantee that none of the variables are accessed by both handlers simultaneously. The other option is to use atomic operations and (if necessary) disable the interrupts to update a variable.

To show what can and cannot be done, a few examples are given in Table 4.4.

When handling a system call or interrupt, only a few processor registers are saved to keep the overhead low. Only when needed, a full task state is saved. An interrupt handler can both interrupt a task and the impulse handler. In the first situation, the task state is not saved. In the second situation it is.

For allocating memory on the heap, we need to guarantee that we are the only process altering the heap control blocks. A task cannot give us these guarantees. In a system call

Figure 4.5: Kernel states and transitions

handler or impulse handler, we know we are the only process doing a malloc(). An interrupt handler can interrupt an impulse handler processing a malloc().

To move tasks between the task scheduling queues, we also need this guarantee. Because the current task is still active when handling a system call, we cannot change the run stack.

We must be able to update the flags field in the task structure when handling an interrupt. As a result, we have to guarantee we are updating the flags field atomically, when handling an interrupt handler. This is described in Section 4.3.1.

|         | $\operatorname{task}$ |                |                           |                       |                           |

|---------|-----------------------|----------------|---------------------------|-----------------------|---------------------------|

|         | state                 | interrupts     | safe to use               | move tasks in         | update                    |

| state   | active                | enabled        | $\operatorname{malloc}()$ | $RT \text{ queues}^a$ | task flags                |

| user    | yes                   | yes            | via syscall               | no                    | no                        |

| syscall | yes                   | no             | $\mathbf{yes}$            | $partially^{c}$       | yes                       |

| irq     | $depends^b$           | no             | no                        | no                    | yes                       |

| impulse | no                    | $\mathbf{yes}$ | $\mathbf{yes}$            | $\mathbf{yes}$        | $\operatorname{atomic}^d$ |

.

$^{\it a}\,$  Moving tasks between the wait queue, condition-wait set, release queue and run stack

$^{b}\ {\rm Which}\ {\rm actually}\ {\rm just}\ {\rm means}\ {\rm we}\ {\rm cannot}\ {\rm make}\ {\rm any}\ {\rm assumptions}\ {\rm about}\ {\rm it}$

$^{c}$  The current task state is not saved yet. Therefore, the run stack cannot be changed.

$^{d}$  We don't like updating the *flags* field, but sometimes we just have to.

The only possibility here is to disable the interrupts temporarily.

#### Table 4.4: All kernel states with some characteristics

In BasOS there are two activities where we may expect race-condition problems. These are task scheduling and in-kernel debugging.

#### **Task Scheduling**

When the kernel is handling an interrupt, the task\_send\_signal() and task\_clear\_signal() functions can be called. When that happens, the flags and cond\_bits will be updated and cond\_bitmask\_in\_use and cond\_bitmask\_wake will be read.

Since interrupts can occur while handling impulse handlers, the impulse handler should take care that these variables are not overwritten. When we take a close look of these four fields in the task structure, we notice that only two of them, *flags* and *cond\_bits*, are actually updated from the impulse handler.

The best way to update these two variables would be by using one assembler instruction which atomically sets or resets bits in memory. Unfortunately, the ARM architecture doesn't have such an instruction, so we have to disable the interrupts, update variable, and re-enable the interrupts:

```

ATOMIC(temp_variable);

task_ptr->flags |= TASK_FLAG_IDLING;

ATOMIC_END(temp_variable);

```

Note that when we are using a multi-processor environment, we probably also need to lock the bus and memory.

#### **In-Kernel Debugging**

In-kernel debugging is only used when testing or debugging a task-set or when something went wrong. We did not develop a full-blown debugger but are informed by using the printk() function. printk() writes a message to the console pipe. During the whole call, the processor is kept in an interrupt disabled state.

### Chapter 5

# **Device** Drivers

The implemented device drivers and how they are used.

#### 5.1 USART

The BCVP has 3 USARTs. Currently, only USART0 is supported (the physical serial connection), with a bit-rate of 115200, 8 bits data, no parity and one stop bit. The task for this driver is to provide a channel which can be used for sending debugging output, without the need to run a full blown debugger.