# UNIVERSITEIT TWENTE.

On the Modeling and Simulation of Novel Schottky Based Silicon Rectifiers

# **Master Thesis**

September 23, 2009 Report Number: 068.027/2009

> Author Tom van Hemert

# Supervisors

prof. dr. J. Schmitz dr. ir. R.J.E. Hueting dr. ir. C. Salm B. Rajasekharan, MSc.

Semiconductor Components Group Faculty of Electrical Engineering

# On the Modeling and Simulation of Novel Schottky based Silicon rectifiers

Master Thesis September 23, 2009 Report number 068.027/2009

> Semiconductor Components Group Faculty of Electrical Engineering Mathematics & Computer Science University of Twente P.O. Box 217 7500AE Enschede the Netherlands

Tom van Hemert

Author

**Supervisors** prof. dr. J. Schmitz dr. ir. R.J.E. Hueting dr. ir. C. Salm B. Rajasekharan, MSc.

# Abstract

This report has been written in conclusion to a master's project in the Semiconductor Components group at the University of Twente. The topic is the DC (Direct Current) current voltage characteristic of both the aMSM- (asymmetric Metal Semiconductor Metal) and the CP- (Charge Plasma) diode. We will make a comparison by focusing on the modeling and simulation of both devices, after comparing those to experimental obtained from conventional vertical Schottky diodes. This report reflects the work which has been done during this project and allows the reader to understand the DC current voltage characteristics of the proposed diodes.

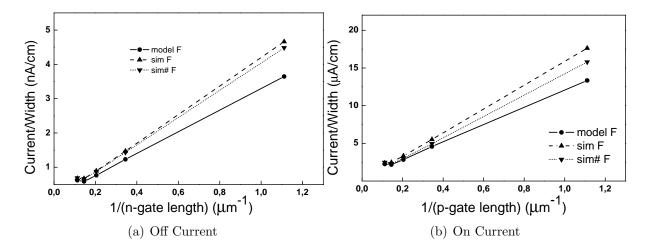

We present an analytical model for the IV characteristics of both diodes. This model is verified using the Synopsys device simulator. The model and the simulator show a good agreement. It was found that when one of the metal work functions is located much further away from silicon midgap then the other, then it is either the transport of holes or electrons which dominates the current. Both the on- and the off-current can be scaled independently from each other by scaling the n-metal gate and p-metal gate length.

An example is shown from which the metal work functions are extracted from experimental Schottky diode test structures. In this case proper scaling of both gate lengths can improve the on/off current ratio of the diode by a factor twenty. In another case work functions from literature were used, here the on/off current ratio couldn't be improved.

# Contents

| Abstract v |                    |                                            |               |  |

|------------|--------------------|--------------------------------------------|---------------|--|

| Ta         | ble o              | of Contents vi                             | ii            |  |

| 1          | <b>Intr</b><br>1.1 |                                            | <b>1</b><br>2 |  |

| <b>2</b>   | The                | eory                                       | <b>5</b>      |  |

|            | 2.1                | Schottky Barriers                          | 5             |  |

|            |                    | 2.1.1 Energy Band Diagram                  | 5             |  |

|            |                    | 2.1.2 Thermionic Emission Current          | 6             |  |

|            | 2.2                | the aMSM-Diode                             | 8             |  |

|            |                    | 2.2.1 Device Structure                     | 8             |  |

|            |                    | 2.2.2 Thermionic Emission Current          | 9             |  |

|            |                    | 2.2.3 Carrier Generation and Recombination | 2             |  |

|            |                    | 2.2.4 The proposed current model           | 2             |  |

|            | 2.3                | The Charge Plasma Diode                    | 3             |  |

|            |                    |                                            | 4             |  |

|            |                    | 2.3.2 The Charged Plasma's                 | 5             |  |

|            |                    | 2.3.3 Diffusion Current                    | 7             |  |

|            |                    |                                            | 1             |  |

|            |                    |                                            | 1             |  |

| 3          | Cali               | ibration 2                                 | 3             |  |

|            | 3.1                |                                            | 3             |  |

|            |                    |                                            | 3             |  |

|            |                    |                                            | 4             |  |

|            | 3.2                |                                            | 7             |  |

|            | 3.3                |                                            | 7             |  |

|            | 3.4                |                                            | 8             |  |

|            | 3.5                | 0.070                                      | 8             |  |

| 4          | Sim                | ulation 3                                  | 1             |  |

| -          | 4.1                |                                            | 1             |  |

|            | 4.2                |                                            | 3             |  |

|            |                    |                                            | 3             |  |

|            |                    | -                                          | 3             |  |

|            | 4.3                |                                            | 8             |  |

|            | 4.4                | 1                                          | 8             |  |

| 5            | Conclusions         5.1       Contribution of this work         5.2       Recommendations for further work         5.3       Acknowledgement | <b>43</b><br>43<br>44<br>45 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| $\mathbf{A}$ | A solution too the Poisson equation in a gated silicon body                                                                                  | 47                          |

| В            | Simulation Information         B.1       The Device Simulator         B.2       aMSM-diode Parameters         B.3       CP-diode Parameters  |                             |

| С            | Input filesC.1 Structure fileC.2 Simulation File                                                                                             | <b>55</b><br>55<br>58       |

| D            | Additional Simulations Results         D.1 Charge under the gates                                                                            | <b>63</b><br>63<br>63       |

| Li           | st of Symbols                                                                                                                                | 65                          |

| Li           | st of Abbreviations                                                                                                                          | 69                          |

| Bi           | bliography                                                                                                                                   | 73                          |

# Chapter 1 Introduction

The relentless scaling of the MOSFET (Metal Oxide Semiconductor Field Effect Transistor) devices during the last decades has recently resulted in devices with gate lengths below 30 nm. These small dimensions have, amongst other things, resulted in serious fluctuations in the dopant concentration and location. An example of a possible variation of the threshold voltage in nano-scale MOSFET has recently been shown by Li et al. [1]. They show that a variation of few hundred  $\mu V$  in the threshold voltage can be expected. Also it becomes rather difficult to control the doping activation, which was shown by Ho et al. [2].

In recent years SOI (Silicon on Insulator) and FinFET (Fin Field Effect Transistor) devices have been investigated as alternative device architectures. These do not necessarily require doping. For instance Chiang et al. [3] showed that the background doping, or impurity concentration, still results in a significant variation of the device characteristics.

Alternatively Schottky based devices, such as Schottky-based MOSFETs thoroughly discussed by Larson & Snyder [4], can be used to eliminate the relevance of doping and corresponding problems altogether. However the Schottky barrier cannot be measured directly. In this case there are two metal (non-ohmic) contacts to the silicon. Conventional Schottky diodes are made with doped silicon. Depending on the type of doping either hole or electron transport dominates the current. In this case an ohmic contact can be made by one of the metals. When a very lowly doped semiconductor is used none of the contacts will be ohmic, hence an metal semiconductor metal structure is made where both interfaces influence the total current.

In 2005 Yang [5] presented a carbon nanotube Schottky diode with asymmetrical metal contacts. The word asymmetrical arises from the very different metal work functions. In 2008 an asymmetrical Schottky barrier diode on a NiGe semiconductor was presented by Ang et al. [6]. They named the device an MSM diode, hence we will use the word aMSM (asymmetrical Metal semiconductor Metal) diode to name these type of devices. Figure 1.1 (a) shows an example of the aMSM-diode.

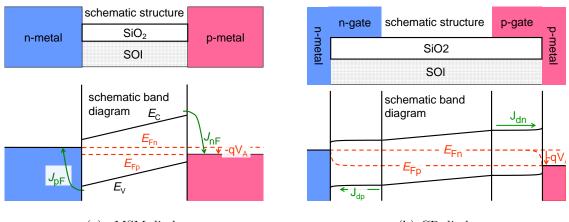

An alternative to the Schottky based device is the charged plasma (CP) diode as presented by Rajasekharan et al. [7]. Here two separate gates are placed on top of a thin silicon body. The metallic gates are isolated from the top of the body by a dielectric. Each of the metals forms a contact at both sides of the silicon body. Figure 1.1 (b) shows the structure and band diagram for this device. Recently this diode has been investigated using device simulations by Hueting et al. [8]. They concluded that the device shows good rectifying behavior depending on the metal work functions of the gates and device dimensions. While the current in the aMSM-diode only depends on the metal-semiconductor interface and hence it is expected that this type of diode does not allow for any scaling of the current by changing the device parameters except for the area. The current in the CP-diode is determined by the diffusion of carriers, hence it is expected that the current is dependent of both the metal-work function and the length of the gates. Therefore lithography can be used to scale the current through the device. In this report we will try to find the exact conditions under which the CP-diode is preferable.

(a) aMSM-diode

(b) CP-diode

Figure 1.1: Schematic structure and schematic band diagram for small forward voltages for: (a) the aMSM-diode, where the current is determined by thermionic emission (their transport is indicated by  $J_{nF}$  and  $J_{pF}$ ) across the Schottky barriers and (b) the CP diode, where the current is determined by the diffusion ( $J_{dn}$  and  $J_{dp}$ ) of carriers under the gates.

# 1.1 Outline

The goal of this work is to make a good comparison of the CP- and the aMSM-diode. To do this it is necessary to derive a model for the currents in both devices to predict the scaling dependence of both devices. This model can be verified using a device simulator. If the model is accurate then the model can be used to compare the performance of a CP to an aMSM-diode. Both the CP-diode and aMSM-diode have not yet been modeled. Hence we will start this work with an experimental analysis of the DC-characteristics of a Schottky junction. Then we will show how this can be used to model the IV characteristics of an aMSM-diode. Also we will present a solution to the characteristics of a CP-diode by combining an electrostatical solution of a FinFET device and the usual diode equations. In the next section we will discuss how the electron and hole barrier heights of different metals can be extracted from measurements on Schottky diodes. These results will be used as parameter inputs for a device simulator. By comparing the measured and simulated characteristics we can verify the simulator and barrier height extraction method. Then we will discuss simulation and modeling results on both the CP- and aMSM-diode. First we will verify our models using simulations, then we will discuss how the CP-diode can be scaled and when a CP-diode is attractive compared to an aMSM-diode. Finally we will draw conclusions from the modeling and simulation results. Also we will give a few recommendations for further work.

# Chapter 2 Theory

In this section we will start with a discussion on the transport of carriers through Schottky junction diodes. Then we will show how this theory can be applied to derive the current equations of an aMSM diode. Finally we will present a model for the CP-diode.

# 2.1 Schottky Barriers

Since the beginning of the twentieth century metal semiconductor rectifiers have found practical applications. When a metal is brought into intimate contact with a semiconductor, this results in a potential barrier. In 1938 Schottky [9] suggested that this potential barrier could arise from stable space charges in the semiconductor. His model gave rise to the now well known thermionic emission theory. The transport processes are reviewed by Rhoderick and Williams [10] and Sze [11]. We will give a brief summary of Sze's explanation of the basic Schottky device behavior.

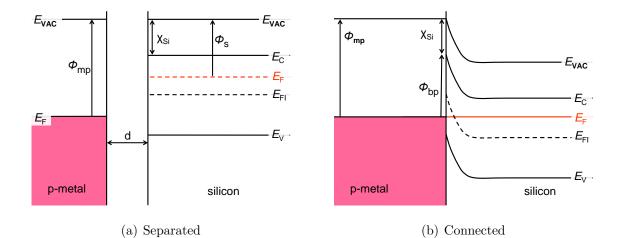

# 2.1.1 Energy Band Diagram

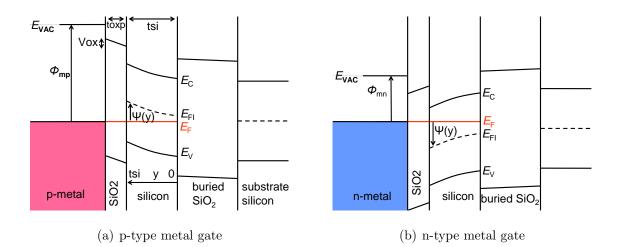

In figure 2.1 (a) a schematic band diagram of a metal and a semiconductor separated by a distance d are shown. The metal Fermi level  $E_{fm}$  indicates the level at which the occupancy of the states by electrons equals 0.5. Below this level the occupancy increases, and above it decreases. The distance between  $E_{fm}$  and the vacuum level is given by  $\phi_m$ .  $\phi_s$  indicates the silicon work function. The conduction band is indicated with  $E_C$ , the extrinsic Fermi level  $E_F$ , the intrinsic Fermi level  $E_{FI}$  and the valence band  $E_V$  are indicated in the same figure. The silicon electron affinity  $\chi_{Si}$  is the distance between the vacuum level  $E_{VAC}$  and the conduction band  $E_C$ . In figure (b) d has been reduced to zero. Therefore the vacuum levels and the extrinsic Fermi levels have to align at the interface. Here a p-type metal is used, therefore all the electrons are pushed away from the metal, hence leaving positive dopant ions which are stuck to the silicon lattice. The charge is compensated by accumulated electrons in the metal layer. The positive charge of the depleted dopant atoms pulls the energy bands downward into the silicon. This continues until the Fermi level is constant. If a n-type metal was used it would be vice versa. The region depleted of electrons is usually called the depletion or space-charge region.

In this case the metal tends to attract holes to and repels electrons from the metal we will call this metal a p-metal. If a metal attracts electrons (or actually repels holes) we will call it a n-metal. Hence, when  $\phi_m > \chi_{Si} + E_G/2$  we call it a p-metal. And when  $\phi_m < \chi_{Si} + E_G/2$  the metal is an n-metal. Often Schottky contacts are characterized

Figure 2.1: (a) a schematic band diagram of a metal and semiconductor. (b) When they are brought together both the extrinsic Fermi level  $E_F$  en the vacuum level have to align. Also the electron affinity  $\chi$  is a material constant, hence a region depleted of electrons is created adjacent to the interface at the semiconductor side

by their barrier height  $\phi_{bp}$  from which the number of carriers at the interface can be calculated. In this discussion we ignored the fact that interface states or even fixed charge might by present at the interface which could change the shape of the bands, as discussed by Rhoderick and Williams [10] and Sze [11]. Because we cannot characterize the metal work function and the interface states separately with a DC measurement we will use the barrier height to characterize the contact and ignore all different possible combinations of metal work function and interface states densities/distributions which could have led to the same barrier height. Note however that an indirect way to extract interface states is possible provided that a good model has been developed by Rhoderick and Williams [10] and Sze [11]. However, this is not a part of this work. The presence of image charge in the metal close to the interface and a field at the interface effectively reduces the potential barrier by an amount, i.e. the image force barrier lowering effect as explained by Rhoderick and Williams [10],

$$\delta\phi = \sqrt{\frac{q\mathcal{E}}{4\pi\epsilon_{Si}}},\tag{2.1}$$

where  $\mathcal{E}$  is the electric field and  $\epsilon_{Si}$  is the dielectric constant of silicon. This effect may be present in our measurements and is included in the extracted barrier heights. Because we use neither a high doping nor expect high barriers in our experiments, the field at the interface will be small and the image force barrier lowering effect negligible.

### 2.1.2 Thermionic Emission Current

The current transport across the interface can be characterized by the thermionic emission theory of Bethe [12]. The following assumptions have to hold (1) that the barrier height  $\phi_b >> u_t$ , where  $u_t$  is the thermal voltage, (2) thermal equilibrium is established at the interface that determines emission and (3) the existence of a net current flow does not affect this equilibrium. Hence we can superimpose the current flux from the semiconductor into the metal and from the metal into the semiconductor. The silicon in our example

| Semiconductor                | Ge   | Si   | GaAs (low field) | GaAs (high field) |

|------------------------------|------|------|------------------|-------------------|

| p-type                       | 0.34 | 0.66 | 0.62             | 0.62              |

| n-type $\langle 111 \rangle$ | 1.11 | 2.2  | 0.068            | 1.2               |

| n-type $\langle 100 \rangle$ | 1.19 | 2.1  | 0.068            | 1.2               |

**Table 2.1:** Values for  $m^*/m_0$  after Crowell [13]

in figure 2.1 (b) is n-type. Therefore the electron transport dominates the current, which allows to neglect the hole current. The electron current density from the semiconductor into the metal, called the forward current  $J_{nF}^{th}$ , depends on the concentration of electrons with energies sufficient to cross the potential barrier and which have a velocity in the direction off the metal. The current is given by,

$$J_{nF}^{th} = A_n^* T^2 e^{-\frac{\phi_{bp}}{u_t}} \cdot e^{\frac{V_A}{nu_t}},$$

(2.2)

where  $V_A$  is the applied voltage on the metal.  $\phi_{bp}$  is the electron barrier.  $A_n^*$  is the Richardson's constant, and n is the ideality factor. The latter characterizes the deviation from ideality of the slope, ideally this factor is 1. If an high forward bias is applied to a Schottky contact then the series resistance of the silicon has to be taken into account, otherwise the current would increase to infinity. In section 3.1 it is shown how this can be done. The reverse current is characterized by the energy electrons in the metal need to have to travel into the conduction band. This barrier height is constantly  $\phi_{bp}$  irrespective of the applied bias. Hence:

$$J_{nR}^{th} = A_n^* T^2 e^{-\frac{\varphi_{bp}}{u_t}},$$

(2.3)

the total electron current through the barrier is  $J_{nt}^{th} = J_{nF}^{th} - J_{nR}^{th}$ . The Richardson's constant characterizes the number of electrons at the interface having enough energy and the correct direction of velocity to cross the barrier. The Richardson's constant is given by:

$$A_{-}^{*} = \frac{4\pi q m^{*} k^{2}}{h^{3}} = 120 \cdot \frac{m^{*}}{m_{0}}$$

(2.4)

, where k and h are the Boltzmann's and Planck's constant respectively and  $m^*$  is the tunneling effective mass. Where  $A_{-}^*$  becomes  $A_n^*$  for electron and  $A_p^*$  for hole emission.  $m^*$  depends on the type of carrier and on the semiconductor. Some values for  $m^*/m_0$  are shown in table 2.1. A Schottky barrier can also be made by putting an n-metal on p-type silicon. The characteristics are similar except now holes determine the carrier transport. The hole barrier  $\phi_{bn}$  is the difference between the Fermi level and the valence band. When intrinsic or lowly doped silicon is used both the hole and electron carrier transport have to be taken into account. The current for a p-type Schottky contact (n-metal p-silicon) is the forward minus the reverse current:

$$J_n^{th} = A_n^* T^2 e^{-\frac{\phi_{bp}}{u_t}} \left( e^{\frac{V_A}{nu_t}} - 1 \right), \tag{2.5}$$

# 2.2 the aMSM-Diode

In the previous section the Schottky junction device characteristics has been briefly explained. In this section we will go one step further. Instead of connecting one metal to the silicon we will connect two metals with both n-type and p-type work functions to an intrinsic silicon layer. In this way we form an aMSM-diode. The current has to run through two Schottky junctions connected in series. The intrinsic or lowly doped silicon results in both metal-semiconductor interfaces to show non-ohmic behaviour. In this section we will discuss the device concept and use the Schottky theory to derive equations for the current in the device. Note that tunneling is neglected here which could become important for high electric fields, e.g. high reverse biases, high metal workfunction differences or short dimensions.

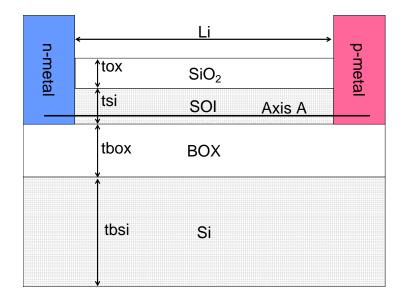

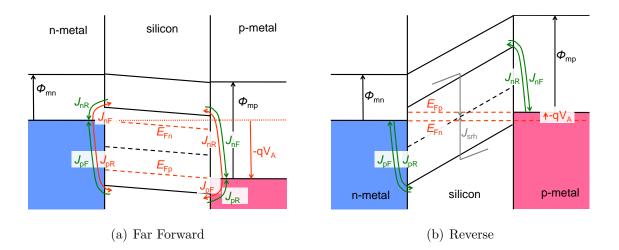

# 2.2.1 Device Structure

In figure 2.2 the device geometry of the diode is shown. The length of the intrinsic region is given by  $L_i$ , the thickness of the front oxide (SiO<sub>2</sub>) by  $t_{ox}$ , thickness of the intrinsic silicon (Silicon-On-Insulator or in short SOI) by  $t_{si}$ , and buried oxide (BOX) thickness  $t_{box}$ . The n-metal and p-metal layer are indicated in blue and pink respectively.

Figure 2.2: A schematic cross-section of the aMSM-diode. When a band diagram along axis A is made the IV relation of the p-metal and n-terminal can be derived. We assume that the band diagram is constant for various tsi.

The current through this device flows along Axis A. A schematic band diagram along this axis is shown in figure 2.3 (a). Here  $\phi_{mn}$  is the work function of the n-metal and  $\phi_{mp}$  is the work function of the p-metal. The hole barrier height at the n-metal silicon interface is given by  $\phi_{bn} = \chi_{Si} + E_G - \phi_{mn}$ . The electron barrier height at the p-metal interface is given by  $\phi_{bp} = \phi_{mp} - \chi_{Si}$ .

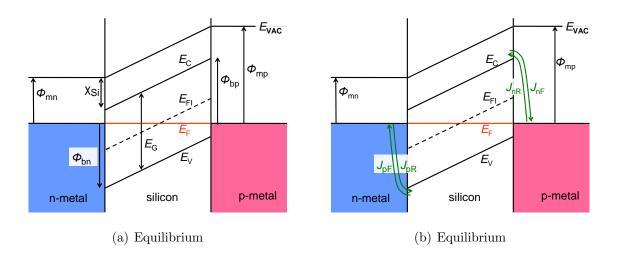

Figure 2.3: (a) Schematic band diagram of the proposed aMSM-diode under equilibrium conditions along axis A in figure 2.2. (b) The green arrows indicate the transport direction of carriers, their labels give the corresponding current components.

# 2.2.2 Thermionic Emission Current

When a bias is applied on the p-metal terminal both electrons and holes can flow into or out of the p-metal terminal. Hence the electron current is determined by a forward component  $J_{nF}^{th}$  and reverse component  $J_{nR}^{th}$ . Also the hole current consists of two components,  $J_{pF}^{th}$  and  $J_{pR}^{th}$ .

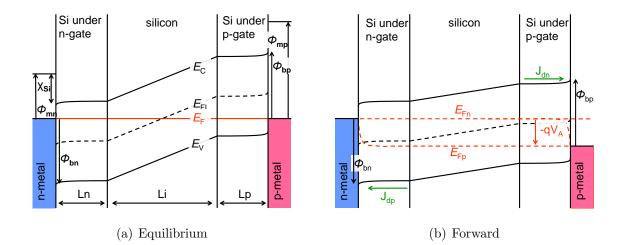

#### Equilibrium

Under equilibrium conditions the electron barrier is the highest at the p-metal interface which determines the thermal emission current. Hence the electron current at equilibrium is determined by the current across the p-metal silicon interface. The forward component is indicated by  $J_{nF}^{th}$ , the reverse current by  $J_{nR}^{th}$ . Both are determined by thermionic emission and can be expressed as:

$$J_{nR}^{th} = A_n^* T^2 e^{\frac{-\phi_{bp}}{u_t}}.$$

(2.6)

For the reverse current the distance between the Fermi level and the conduction band is given by the barrier height  $\phi_{bp}$ . For the forward current the number of electrons in the conduction band is reduced by this same factor so the forward current becomes:

$$J_{nF}^{th} = A_n^* T^2 e^{\frac{-\phi_{bp}}{u_t}},$$

(2.7)

both currents are equal but are in opposite direction, resulting in a net zero electron current. The hole current is determined by emission across the n-metal silicon interface. Analogue to the electron current both forward and reverse hole current are equal but opposite in direction, resulting in a net zero hole current. The reverse hole current is given by:

$$J_{pR}^{th} = A_p^* T^2 e^{\frac{-\phi_{bn}}{u_t}}.$$

(2.8)

Figure 2.4: Schematic band diagram of the proposed aMSM-diode. (a) When a small forward bias  $V_A$  is applied on the p-metal the forward components  $J_{nF}$  and  $J_{pF}$  increase with a factor  $exp(V_A/u_t)$ . (b) In flat band condition  $(V_A = \phi_{mp} - \phi_{mn})$  the forward currents components become limited by by thermionic emission from the metal into the silicon, this is indicated by the red arrows.

#### Forward biasing

When a small positive bias is applied on the p-metal terminal and the n-metal terminal is grounded, the p-metal Fermi level is slightly shifted down as indicated by  $-qV_A$  in figure 2.4(a), thereby effectively reducing the barrier height. The electron quasi-Fermi level  $E_{Fn}$ is determined or pinned by the Fermi level of the n-metal and the hole quasi-Fermi level  $E_{Fp}$  by the p-metal Fermi level. An applied bias causes splitting between both quasi-Fermi levels. If the silicon is shorter then it's corresponding Debye length, ideally the silicon is lowly doped and hence the Debye length will be very long <sup>1</sup>, then the splitting results in increased carrier concentrations at the metal semiconductor interfaces. The electron concentration in the silicon at the p-metal interface and the hole concentration in the silicon at the n-metal interface are both increased by a factor  $exp(qV_A/kT)$ , or in fact the barrier height has reduced by  $V_A$ . The reverse current does not depend on the applied bias. The forward current components become:

$$J_{nF}^{th} = A_n^* T^2 e^{\frac{-\phi_{bp}}{u_t}} e^{\frac{V_A}{u_t}}$$

(2.9)

and

$$J_{pF}^{th} = A_p^* T^2 e^{\frac{-\phi_{bn}}{u_t}} e^{\frac{V_A}{u_t}}.$$

(2.10)

#### Far forward biasing

When  $V_A = V_{FB} = (\phi_{mp} - \phi_{mn})$  the device is in flat band condition. This is shown in figure 2.4 (b). For the flatband condition the maximum thermionic emission current from the n-metal into the conduction band is equal to the emission current from the conduction band into the p-metal (labeled  $J_{nF}$  in red.). The red arrows in the figure are the currents which limit the total current. The reverse currents are still constant and

<sup>&</sup>lt;sup>1</sup>that is the length at which the charge carrier concentration (n or p) will drop by a factor 1/e

Figure 2.5: Schematic band diagram of the proposed aMSM-diode.(a) In far forward the red arrows indicate the current components which limit the current, this situation is comparable to flat band.(b) In reverse the forward components  $J_{nF}$  and  $J_{pF}$  are reduced. The SRH-current  $J_{srh}$  draws electrons from the right and holes from the left metal contact. Hence this current can be modeled parallel to the emission currents.

negligible. Unfortunately a further increase in applied voltage as shown in figure 2.5 (a) will not change the barrier height between the n-metal and the semiconductor. Hence the electron current remains limited by the barrier between the n-metal and the silicon. For the hole current the same effect applies, but now the p-metal silicon interface limits the current. This current is indicated by  $J_{pF}$  in red. Hence, for far forward bias holds:

$$J_{nF}^{th} = A_n^* T^2 e^{\frac{\phi_{bn} - E_G}{u_t}}$$

(2.11)

and

$$J_{pF}^{th} = A_p^* T^2 e^{\frac{\phi_{bp} - E_G}{u_t}}.$$

(2.12)

Often the currents will not reach these limits, this is caused by the resistance of the intrinsic region. If flat band conditions are reached then there will be no concentration differences in the intrinsic region any more. Hence a bias across the intrinsic region is required to generate a drift current. The electron and hole drift currents are easily described by multiplying the number of carriers in the intrinsic region, which now have become constant along axis A, charge, mobility and electric field. Now we find a hole and electron current density limited by the resistance:

$$J_{p,i}^{dr}(V_A > V_{FB}) = \frac{N_V q \mu_p (V_A - V_{FB})}{Li} e^{\frac{\phi_{bp} - E_G}{u_t}},$$

(2.13)

respectively

$$J_{n,i}^{dr}(V_A > V_{FB}) = \frac{N_C q \mu_n (V_A - V_{FB})}{Li} e^{\frac{\phi_{bn} - E_G}{u_t}}.$$

(2.14)

#### **Reverse** biasing

When a negative bias is applied on the p-metal terminal and the n-metal is grounded, the hole quasi-Fermi level shifts up compared to the electron quasi-Fermi level. This decreases

both carrier concentrations at the interfaces by a factor  $exp(qV_A/kT)$  resulting in a lower forward current components. Finally the current equations are equal to the forward case. But now  $V_A$  is negative and reduces the forward current until only the reverse current component is left.

## 2.2.3 Carrier Generation and Recombination

In practice the current in a PN-junction diode may be far in excess of that predicted by the diffusion theory especially for small forward biases. This current arises from the recombination for forward bias and generation of carriers for reverse bias through traps. Because of charge conservation, the empty places left behind by recombination have to be filled up. Eventually this results in a small current from the contacts. This is the so-called Shockley-Read-Hall [14][15] recombination/generation current, or in short SRH-current. The current will not be caused by Auger , as shown by Auger et al. [16], recombination because this requires a high number of minority carriers which are not present for small forward biases. Sah et al. [17] described the SRH-current in PN-junctions. We will use the SRH-current model in PN junctions as described by Pierret [18]. Traps at the intrinsic Fermi level have the highest probability of causing recombination, and hence affecting the SRH-current, therefore we neglect all other trap levels. Using  $L_i$  for the length of the intrinsic region we get:

$$J_{srh} = \frac{qn_i Li}{\tau_n + \tau_p} (e^{\frac{V_A}{2u_t}} - 1).$$

(2.15)

Here  $\tau_n$  and  $\tau_p$  are the electron and hole life time respectively. Note that the slope of the recombination/generation current is given by  $exp(V_A/2u_t)$ . For practical semiconductor devices the carrier lifetimes are almost unknown and very strongly dependent on fabrication. However, for good quality bulk silicon the lifetimes are well defined. Still, the chance that our model is in agreement with measurement data is quite small. Fortunately the model can help us to understand the device characteristics. For reverse and small forward biases the SRH-current can be modeled parallel to the diffusion currents because it draws a current only from the regions with either high hole or high electron concentration, which are not the regions which limit the thermionic emission. Hence electrons are drawn from the n-metal contact and holes from the p-metal contact.

### 2.2.4 The proposed current model

From equations 2.6 and 2.9 we find the thermionic emission electron current;

$$J_n^{th} = J_{nF}^{th} - J_{nR}^{th} = A_n^* T^2 e^{\frac{-\phi_{bp}}{u_t}} \left( e^{\frac{qV_A}{kT}} - 1 \right), \qquad (2.16)$$

and from equations 2.8 and 2.10 the thermionic emission hole current:

$$J_p^{th} = J_{pF}^{th} - J_{pR}^{th} = A_p^* T^2 e^{\frac{-\phi_{bn}}{u_t}} \left( e^{\frac{qV_A}{kT}} - 1 \right).$$

(2.17)

When biases above the flatband voltage are applied the electron current becomes limited by the sum of the reverse current 2.6, and maximum forward current, as in equation 2.11;

$$J_{n,max}^{th} = A_n^* T^2 \left( e^{\frac{\phi_{bn} - E_G}{u_t}} - e^{\frac{-\phi_{bp}}{u_t}} \right),$$

(2.18)

the hole current becomes also limited and is given derived from equation 2.8 and 2.12:

$$J_{p,max}^{th} = A_p^* T^2 \left( e^{\frac{\phi_{bp} - E_G}{u_t}} - e^{\frac{-\phi_{bn}}{u_t}} \right).$$

(2.19)

Let us limit the electron and hole current by the drift currents, equations 2.13 and 2.14, thermionic emission currents  $J_n^{th}$  and  $J_p^{th}$ , and maximum thermionic emission currents  $J_{n,max}^{th}$  and  $J_{p,max}^{th}$ :

$$J_{nt}^{th,-1} = J_n^{th,-1} + J_{n,max}^{th,-1} + J_{n,i}^{dr,-1},$$

(2.20)

and

$$J_{pt}^{th,-1} = J_p^{th,-1} + J_{p,max}^{th,-1} + J_{p,i}^{dr,-1}.$$

(2.21)

The SRH, hole and electron current are all parallel to each other, hence we can simply add them to find the total current density:

$$J_t = J_{nt}^{th} + J_{pt}^{th} + J_{srh}^{th} \tag{2.22}$$

For the total current current we can say that:

$$I_t = Z \cdot tsi \cdot J_t, \tag{2.23}$$

where Z is the width of the device.

# 2.3 The Charge Plasma Diode

As the name suggests a conventional PIN-diode consists of three regions: 1) a p-type region which is doped with acceptor-like atoms to form a region with a majority number of holes, 2) An undoped or intrinsic region, and 3) an n-type region, which is doped with donor-like atoms to form a majority of electrons. As explained in the introduction a way to fabricate an ultrathin p-i-n diode without employing an implantation process would be preferred. Such a device was proposed in 2008 by Rajasekharan et al. [7] for silicon-on-insulator (SOI) technology with a very thin oxide layer on the top. The p- and n-type regions are induced by a metal gate with a well chosen work function. These regions are not doped however we could say that a plasma of charged carriers is created in these thin regions. Hence the device is called Charge Plasma (CP) diode. At the extensions of the p- and n-type region the gates are directly contacted to the silicon layer. These metal gates form respectively the anode and cathode of the device.

At the end of 2008 a simulation study of the CP-diode was presented by Hueting et al. [8], discussing how the gate work functions and the device geometry should be chosen. It was claimed that to acquire a worthy rectifying behavior the difference in gate work functions should be at least 0.5 eV. Also the silicon thickness should be less than the Debye length, that is the length at which the charge carrier concentration (n or p) will drop by a factor 1/e in the direction of the gate-oxide-silicon junction. Therefore for too thick silicon layers there will be a plasma close to the gate, but there won't be a plasma close to the buried oxide. Hueting et al. also presented some simulation results, indicating that a charge plasma diode with a well chosen metal gate work function can achieve a good rectifying behavior.

## 2.3.1 Device Structure

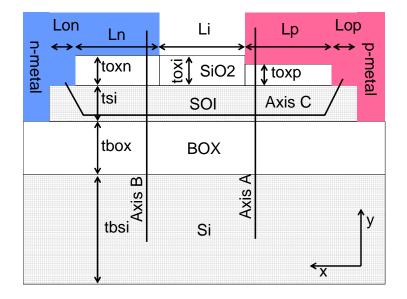

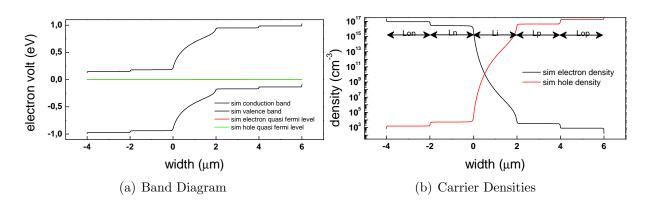

A schematic device geometry of the CP P-N diode is shown in figure 2.6. The blue region indicates the n-metal. The metal is named like this because its work function is chosen such that it induces an electron (negative carrier or n-type) plasma in the neighbouring silicon. We will refer to this gate as the n-gate (n-type metal gate). The gate made of p-metal is colored purple and induces a hole (positive carrier or p-type) plasma in the neighbouring silicon. We will refer to this gate as p-gate (p-type metal gate). The SiO<sub>2</sub> region is the silicon oxide insulator on top of the ultrathin silicon layer. The oxide adjacent to the n- and p-gate do not necessarily have the same thickness. Hence their thicknesses are indicated by toxn and toxp. The oxide thickness in the region which is not covered by gates is set at the maximum of both toxp and toxn. SOI stands for silicon on insulator, indicating the silicon. The oxide beneath the SOI layer is called the buried oxide (BOX). Beneath the buried oxide is another silicon layer, called the silicon substrate. The lengths Lon and Lop denote the overlap length of the metal, which effectively increases the direct contact area between the metal and the silicon. The length of the gates are given by Ln and Lp. The space between the gates indicates the length of the intrinsic region in the silicon and is given by Li.

As a start it would be useful to draw the band diagram under equilibrium conditions along axis A in figure 2.6. This will give an indication for the amount of charge carriers below the p-gate which we need for modeling the CP diode. Let us assume that this concentration in equilibrium will be constant along axis C under the p-gate. Then the band diagram of axis A will be valid all along the p-gate. A band diagram along axis B can be used to derive the carrier concentration below the n-gate. Finally these solutions can be used to construct the band diagram in equilibrium along axis C which is essential to find the current between the p- and n-metal terminals.

Figure 2.6: The schematic cross-section of the CP diode used for simulations showing all the parameters which characterize the CP P-N device geometry. We will start with a derivation of the carrier concentrations using schematic band diagrams along both axis A and B. Using their solutions we can derive the carrier concentrations along axis C.

### 2.3.2 The Charged Plasma's

In figure 2.7 (a) the band diagram along axis A of figure 2.6 is shown. When the gate induces a hole plasma under the gate then the gate is connected via a relatively low thermionic emission barrier to the holes over the length Lop and tsi to the silicon. Hence the Fermi level of the silicon adjacent to the metal and below the gate equals to the Fermi level of the gate. The p-gate work function  $\phi_{mp}$  shifts the silicon bands upwards. This brings the Fermi level closer to the valence band  $E_V$  which induces a hole plasma. For convenience sake, let us neglect the influence of the buried oxide and silicon substrate. Then all the charge which has to be taken into account is present in either the silicon or the metal layer, assuming no oxide charge or interface traps. If the concentration of holes in the charge plasma is higher than the doping concentration, then the presence of the dopant atoms can be neglected. The hole plasma in the silicon forms positive charge. The derivative of the potential is proportional to the charge, yielding an upward movement of the silicon bands along the y-axis as indicated in figure 2.7(a). The second derivative of potential is also proportional to the charge. Hence the silicon bands should become less flat along the y-axis. The same reasoning can be applied on figure 2.7 (b) to find a solution for the electron concentration under the n-gate.

Figure 2.7: (a) Schematic band diagram along the axis A of figure 2.6, the metal work function causes the band of the silicon to be shifted upwards yielding a hole plasma. (b) And along axis B, where the silicon bands are shifted downwards and an electron plasma is formed.

Using the band diagram sketch in figure 2.7 (a) we can derive an exact solution for the band diagram. There are still a few unknowns to solve. For example the voltage across the front oxide Vox, which is related to the electric field at the silicon front-oxide interface. Also we need to find a solution for the delta potential  $\Psi(y)$ , which is the difference between the extrinsic and intrinsic Fermi level divided by the electron charge, in the silicon. Inside the silicon both the delta potential and charge obey the Poisson equation. For ultrathin silicon layers and low gate voltages we can neglect the doping and minority carrier charge. Then the Poisson equation is given by:

$$\frac{\delta^2 \Psi}{\delta y^2} = u_t \delta e^{\frac{\Psi(y)}{u_t}},\tag{2.24}$$

where  $\delta$  is a measure for the amount of carriers and their influence on the delta potential:

$$\delta = \frac{n_i}{\epsilon_{Si} u_t},\tag{2.25}$$

here  $\epsilon_{Si}$  is the dielectric constant of silicon and  $u_t$  is the thermal voltage. We assumed that the intrinsic Fermi level  $E_{FI}$  lays exactly at the center of the band. This holds as long as  $N_V \approx N_C$ , which is valid in silicon.  $\Psi(y)$  is a function for the delta potential along y-axis in figure 2.7. All we need is a solution to this function. A similar problem shows up for the inversion charge in the subthreshold regime of a double gate MOSFET. A solution for this problem has been proposed by Taur [19] [20]. A demonstration of the validity of his solution can be found in appendix A. He proposes the following solution for the delta potential:

$$\Psi(y) = \Psi(0) - 2u_t \ln \cos(\beta y), \qquad (2.26)$$

$$\beta = \sqrt{\frac{\delta}{2}e^{\frac{\Psi(0)}{2u_t}}}.$$

(2.27)

Here  $\Psi(x)$  has a value  $\Psi(0)$  at the buried oxide-silicon interface and increases for y. Note that  $-\ln \cos(\beta y)$  is always positive. By applying the correct boundary conditions in our system we are able to derive the unknown variable  $\Psi(0)$ . Let us go back to figure 2.7 (a). The difference in vacuum level for the metal and the silicon is equal to the potential across the oxide Vox. The work function difference between the silicon and the metal is  $\phi_{ms} = \phi_{mp} - \chi_{Si} - E_G/2$ . The delta potential at the surface  $\Psi(y = tsi)$  is equal to the work function difference minus the potential across the oxide:

$$\phi_{ms} - V_{ox} = \Psi(y = tsi). \tag{2.28}$$

If there is no charge in the front oxide silicon interface then the dipole moments on both sides of this interface are equal. Hence  $\epsilon_{Si}\mathcal{E}_{Si} = \epsilon_{SiO2} \cdot \mathcal{E}_{SiO2}$  where  $\mathcal{E}$  denotes the electric field. The electric field in the silicon is given by the first derivative of the delta potential  $\mathcal{E}_{Si}=-\delta\Psi(y)/\delta y$ . There is no charge inside the oxide, hence the electric field in the oxide is constant. The potential across the oxide now must be  $V_{ox}=-tox \mathcal{E}_{SiO2}$  with tox = toxn or toxp. Thus the potential across the oxide is equal to:

$$V_{ox} = tox \frac{\epsilon_{Si}}{\epsilon_{SiO2}} \frac{\delta \Psi(y)}{\delta y}|_{y=tsi}.$$

(2.29)

Now equations 2.29 and 2.26 can be combined to one equation with one variable  $\Psi(0)$ :

$$\Psi(0) = \phi_{ms} + 2u_t \ln \cos(\beta y) - tox \frac{\epsilon_{Si}}{\epsilon_{SiO2}} \frac{\delta \Psi}{\delta y}|_{y=tsi}.$$

(2.30)

The structure in this equation is a relationship more or less according to x = exp(x)and can be solved by numerical iteration. When a solution for the unknown variable  $\Psi(0)$ is found the delta potential in the silicon as described by equation 2.26 can be calculated. The delta potential describes the distance between the intrinsic and extrinsic Fermi level in the silicon. Therefore the equilibrium carrier concentrations under the gate can be derived as a function of y. When  $\Psi(0)$  is derived for either the p-gate or the n-gate, their majority carrier concentrations can be expressed as;

$$p_p = n_i \cdot e^{\frac{\Psi(y)}{u_t}},\tag{2.31}$$

and:

$$n_n = n_i \cdot e^{\frac{-\Psi(y)}{u_t}},\tag{2.32}$$

where  $p_p$  is the hole concentration under the p-gate and  $n_n$  is the electron concentration under the n-gate. Now the majority carrier concentrations are known the minority carrier concentrations can be calculated:

$$n_p = \frac{{n_i}^2}{p_p},$$

(2.33)

and:

$$p_n = \frac{n_i^2}{n_n}.\tag{2.34}$$

The hole concentration under the n-gate is given by  $p_n$  and the electron concentration under the p-gate by  $n_p$ . Hence, since the majority carriers depend exponentially on the metal workfunctions, this also holds for the minority carriers. The careful reader must have noted that  $\Psi(y)$  is function of y. Hence the carrier concentrations depend on y. The highest number of minority carriers can be found at the silicon buried oxide interface. The largest concentration of minorities will dominate the diffusion current. Therefore we assume that the total current can be derived by using the carrier concentrations for y = 0.

#### 2.3.3 Diffusion Current

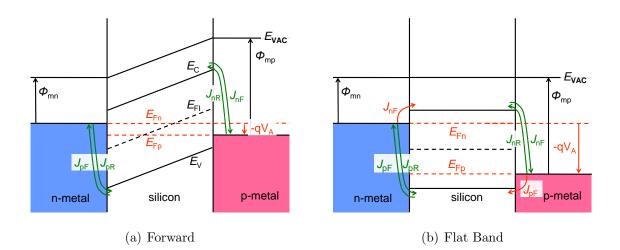

In the previous section a solution has been shown for the carrier densities under the pand n-gate in figure 2.6. When the gate work functions  $\phi_{mn}$  and  $\phi_{mp}$  are well chosen a positive charged plasma can be created under the p-gate and a negatively charged plasma under the n-gate. A region with the length *Li* is not covered by a gate, hence no charged plasma is created in this junction. The shortest current path between the n- and pgates is indicated by the Axis C in figure 2.6. Only for high forward voltages the region with the lengths *Lon* and *Lop* may become important. If we follow this axis we cross subsequently a n-metal, a negatively charged plasma under the gate oxide, an intrinsic region, a positively charged plasma under a gate and the p-gate. A band diagram under equilibrium conditions along this axis is shown in figure 2.8(a).

#### Equilibrium

In equilibrium no voltage is applied between the n- and p-gates. Hence the Fermi level in the band diagram of figure 2.8(a) is constant. The Fermi level in the silicon under the n-gate is close to the conduction band and indicates a strongly increased number of electrons and hence a negatively charged plasma. Under the p-gate the Fermi level is close to the valence band. In the "intrinsic" region no charge is present and when the substrate contacts are neglected the bands have to be straight lines. Also the bands in the intrinsic region have to connect to the bands in the regions under the gates. Together these requirements require band energies with a constant slope in the intrinsic region.

In reality the intrinsic region will have a low doping. As long as the length of intrinsic region is much shorter than the corresponding Debye length this will give no problems. There is Schottky barrier, as discussed in section 2.1, between the charged silicon and

Figure 2.8: Schematic band diagram along axis C of figure 2.6, the green and pink area indicate the metals. The gates with a length Lnrespectively Lp induce a charged plasma shown by the distance between the extrinsic and intrinsic Fermi level. An intrinsic region of length Li exists between the charged plasma's. (a) there is no current flow in equilibrium (b) when a small forward bias  $V_A$  is applied on the p-gate the diffusion

it's adjacent metal. This barrier is characterized by the barrier height. For now we will assume that this barrier doesn't limit the current. The hole barrier height at the n-metal silicon interface is given by  $\phi_{bn} = -\chi_{Si} + E_G - \phi_{mn}$ . The electron barrier height at the n-metal silicon interface is given by  $\phi_{bp} = \phi_{mp} - \chi_{Si}$ . These barrier heights induce a slightly more charged plasma compared to the regions under the gate. Under the gate the oxide has already absorbed part of the metal semiconductor work function difference which leads to a less charged plasma. This difference is also shown in the band diagram. Near the silicon metal interfaces the bands show a slight curvature, resulting in more charge. In equilibrium conditions no voltage is applied, hence there should be no current through the device.

We can also explain this by having another look at the band diagram. If no recombination or generation is present then the electron current should be constant throughout the device. The electron current will be determined by region in which it's has a very low concentration compared to the other regions. In equilibrium this is the case under the p-gate. Under this gate the electron concentration is constant and the bands are horizontal. Hence both diffusion and drift are excluded as possible current transport mechanisms and the resulting electron current will be zero. Off course a small deviation of this theory exists in the bands and concentrations close to the p-gate interface. As long as this region is much smaller then the gate length this will give no problems.

#### Forward

When the p-gate is biased positively compared to the n-metal the bands under the p-gate are shifted downward compared to the bands under the n-gate. Also the Fermi level is separated in two distinct Fermi levels, also called quasi-Fermi levels.  $E_{Fn}$  becomes the quasi-Fermi level for electrons and  $E_{Fp}$  the quasi-Fermi level for holes. Inside the device these quasi-Fermi levels are relatively constant. This was shown for p-n junction by Shockley [21]. We will follow Sze's conclusions [11]. The quasi-Fermi levels are constant because: (1) In the charged plasmas the semiconductor has not an equal number of holes and electrons so generation/recombination is not important here and both electron and hole current remain constant. (2) The length of the regions are much shorter than the diffusion length, typically 60  $\mu$ m for holes and 190  $\mu$ m for electrons, therefore the total drop of the quasi-Fermi levels cannot be significant. Under the gates the majority carriers quasi-Fermi levels are fixed by the gate semiconductor work function difference. Hence an applied voltage  $V_A$  will shift both quasi-Fermi levels apart from each other:

$$qV_A = E_{Fn} - E_{Fp}.\tag{2.35}$$

This applied voltage will increase the minority carrier concentration in the regions under the gates close intrinsic region by a factor  $exp(V_A/u_t)$  compared to equilibrium. The hole current is determined by the region with the lowest hole concentration. Which is the region under the n-gate. This can be observed in figure 2.8(b), under the n-gate the distance between the hole Fermi level and valence band is the largest giving the lowest number of holes. The n-gate mainly determines the potential in this region, therefore there is almost no potential drop and the current must be originate from diffusion current caused by carrier concentrations differences. The hole concentration at the n-metal silicon interface is much lower compared to the concentration at the intrinsic region interface. If we assume the hole concentration to degrade linearly the hole current is given by the derivative of the hole concentration multiplied with the diffusion constant and elementary charge:

$$J_p^d = \frac{p_n q D_p}{Ln} (e^{\frac{V_A}{u_t}} - 1), \qquad (2.36)$$

where  $D_p$  is the hole diffusion constant. The movement of the carriers corresponding to this hole diffusion current has been indicated in figure 2.8 (b) with a green arrow labelled  $J_{dp}$ . Here we assume the hole concentration at the n-gate intrinsic interface to be equal to  $p_n \cdot exp(V_A/u_t)$  and the hole concentration at the n-gate silicon interface to be much lower. The latter concentration will increase with increasing current as has been showed in the user guide [22]. Since at the contacts an effective surface recombination was assumed corresponding to the thermionic emission model, the minority carrier concentration at the contacts won't reach their equilibrium values. In fact these carrier concentrations are governed by the current densities and the boundary conditions. As long the forward voltages bias is not to high the effective surface recombination can be neglected and equation 2.36 should hold. The result is comparable to the PIN-diode theory showed by Baliga [23], except that he expects the intrinsic region to be the limiting region for carrier transport. This is true when the intrinsic region becomes very long. We can apply the same theory to derive the electron current. Which will result in:

$$J_n^d = \frac{n_p q D_n}{L p} (e^{\frac{V_A}{u_t}} - 1).$$

(2.37)

#### Far Forward

For increasing forward voltages the current will increase according to equations 2.36 and 2.37. However for high voltages this will not hold anymore. Some other process limits the current. In this work we will call this far forward. A band diagram of this situation has been sketched in figure 2.9 (a). The hole quasi Fermi level is closest to the valence band

in the region under the n-gate. Hence the concentration of holes under this gate is not the lowest any more. The lowest concentration of holes is found at the arrow labeled B.

Figure 2.9: Schematic band diagram along axis C of the proposed CP-diode. (a) When a large positive bias  $(V_A > V_{FB})$  is applied the device is in far forward. The current is determined by the diffusion of carriers from the metal to to the intrinsic region, the carrier transport directions are indicated by the green arrows. (b) When a negative bias is applied on the p-gate terminal the forward components become small and the reverse components stay.

The holes at the p-metal silicon interface have to diffuse through the silicon under the p-gate. An approximation for this current can be obtained by assuming that the hole concentration drops linearly across this region. The highest hole concentration is found at the p-metal interface. Hence the diffusion current is given by;

$$J_{p,max}^{d} = \frac{N_V q D_p}{L p} e^{\frac{\phi_{bp} - E_G}{u_t}},$$

(2.38)

we can also derive the maximum electron current:

$$J_{n,max}^{d} = \frac{N_{C}qD_{n}}{Ln}e^{\frac{\phi_{bn}-E_{G}}{u_{t}}}.$$

(2.39)

We like to note that the expression for the carrier concentration at the n-metal interface increases for large currents. This is demanded by the boundary conditions for Schottky interfaces given in [22], as explained earlier. Therefore this diffusion current will not be constant in reality but will slightly increase for increasing forward voltage. There can also be other reasons for the current to be limited. For example the speed of the carriers in the intrinsic region cannot exceed the carrier saturation velocity. The carriers also have to cross the Schottky barriers between the metal and silicon.

#### Reverse

When a negative bias is applied at the p-gate compared to the n-gate we say that the device is in reverse. A band diagram of this situation is shown in figure 2.9 (b). In this situation equation 2.35 is still valid at the boundaries of the intrinsic region. Hence the minority carrier concentrations here are known. The hole concentration reaches its minimum level under the n-gate. Now the hole current is given by diffusion from the n-metal interface to the boundary of the intrinsic region. At the interface the hole concentration is given by 2.34. The hole concentration at the boundary is lowered by a factor  $exp(V_A/u_t)$ . Now the currents again are given by the same equation as the forward currents.

## 2.3.4 Carrier Generation and Recombination

Like in the PIN-device 2.2.3 a SRH-current may be important in the CP diode. Again the length of the intrinsic region is given by Li. Therefore we will use equation 2.15 again to define the SRH-current. For reverse and small forward biases the SRH-current can be modeled parallel to the diffusion currents because it draws a current only of the majority carriers.

#### 2.3.5 The proposed current model

We showed how to derive both electron and hole current for different bias conditions. In reverse and forward the results are almost equal to the Shockley equation [11]. Although in our devices it is not the diffusion length but it is the length of the diffusion regions which determines the current. For high forward bias the currents becomes limited by diffusion of majority carriers under the gates. Also there exists Schottky contacts between the metal and the silicon, these may limit the current as well. Let us incorporate equation 2.20 and 2.21 as derived in the previous section to limit the current by thermionic emission and to account for the resistance of the intrinsic intrinsic region in forward. These don't incorporate the added contact lengths *Lon* and *Lop*, however due to current crowding the area where the current flows will not easily become bigger then tsi. For the electron and hole current we find:

$$J_p^{d,-1} = J_{dp}^{d,-1} + J_{dp,max}^{d,-1} + J_{pt}^{th,-1},$$

(2.40)

and:

$$J_n^{d,-1} = J_{dn}^{d,-1} + J_{dn,max}^{d,-1} + J_{nt}^{th,-1}.$$

(2.41)

The SRH, hole and electron current are all parallel to each other, hence we can simply add them to find the total current density:

$$J_t^d = J_n^d + J_p^d + J_{srh}^d. (2.42)$$

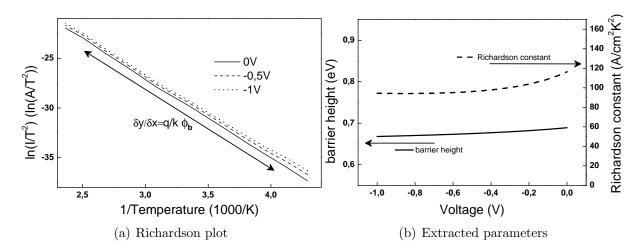

# Chapter 3 Calibration

# **3.1** Barrier Height Extraction Techniques

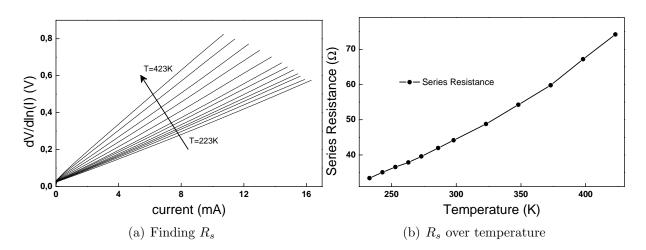

In this section we will illustrate how the IV characteristics of an electron Schottky barrier for different temperatures can be used to derive the Schottky diode parameters as described in section 2.1. The extraction of the parameters for a hole Schottky barrier is similar. The silicon has to be either n- of p-type which allows to analyze either the hole or electron transport mechanism. The parameters which we will extract include the ideality factor n, which characterizes the deviation of the forward current from the ideal thermionic emission model. The series resistance in the measurement structure times unit area is denoted by  $\rho_s$ , the electron emission barrier height by  $\phi_{bp}$  and the Richardson constant  $A_n^*$ . Let us include the series resistance into equation 2.2, then the forward and reverse electron current components of a Schottky barrier are given by;

$$J_{nR}^{th} = A_n^* T^2 e^{-\frac{\phi_{bp}}{u_t}},$$

(3.1)

and;

$$J_{nF}^{th} = A_n^* T^2 e^{-\frac{\phi_{bp}}{u_t}} e^{\frac{(V_A - J_{nF}^{th} \rho_s)}{nu_t}},$$

(3.2)

where  $\rho_s$  is the series resistivity <sup>1</sup>.

### 3.1.1 Reverse

Let us start with the reverse characteristics of the Schottky diode. Ideally this current should have no slope and be constant for reverse biases greater then a few  $u_t$ . In reality it has, this can be caused by SRH recombination which we described in section 2.2.3. For  $V_A = 0$  the SRH-current is zero. Hence if we extrapolate the current to the Y-axis crossing we can find the reverse current independent of the SRH-current. We start to fit a linear regression to the curve with the coefficients  $\alpha$  (the value for  $V_A = 0$ ) and  $\beta$ (the slope). Then we recreate the reverse IV characteristic using  $\alpha + \beta V = Jth_{nR,reg}$ . Another advantage, besides removing the SRH-current component, of this technique is to eliminate noise. In equation 3.1 we can replace  $J_{nR}^{th}$  with our current found by linear regression  $J_{nR,reg}^{th}$ .

<sup>&</sup>lt;sup>1</sup>since the modeling is in 1D the resistivity is expressed in  $\Omega cm^2$ . In real life however this is of course in  $\Omega$

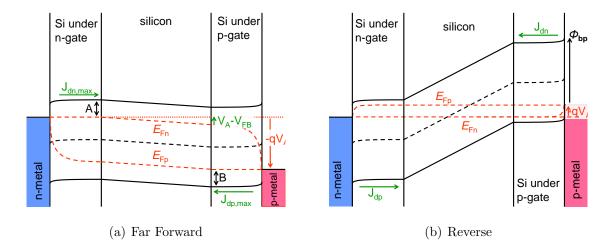

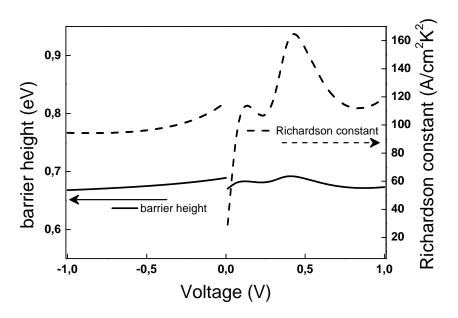

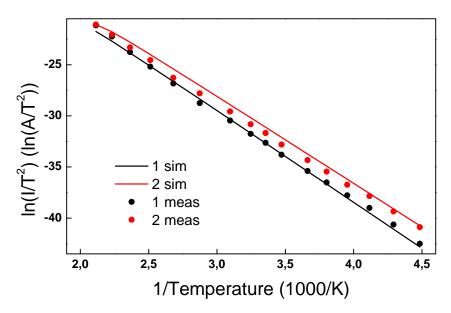

Let us follow Schroder [24] to extract the barrier height and Richardson constant from this equation:

$$\ln \frac{J_{nR,reg}^{th}}{T^2} = \ln A_n^* - \phi_{bp} q/kT$$

(3.3)

When we plot  $\ln(J_{reg}^{th}/T^2)$  versus 1/T the graph will have a slope equal to  $q/k\phi_{bp}$  and Y-axis crossing  $\ln(A_n^*)$ . Such a graph is usually called a Richardson plot. We illustrate this by an example, the Cobalt on n-type silicon junction, in figure 3.1(a). The plot is shown for three different reverse biases. Ideally these three should be equal. In reality they are not because of secondary effects. For zero bias the SRH-current component should be zero and hence for zero bias the Richardson plot is ought to be correct.

In figure 3.1 we show the extracted parameters. The extracted barrier height varies by a few percent. The Richardson constant is found by extrapolation of the Richardson graph. We have measurement data till 2,5 (1000/K), hence we have to extrapolate on the Y-axis from 2.5 to 0 (1000/K). Therefore a small error in the slope might result in a serious error in the extracted Richardson constant. So we can conclude that although the Richardson constant can be extracted it will be very prone to error.

Figure 3.1: (a) The Richardson graph of a Cobalt on n-type Silicon Schottky barrier, the slope gives φ<sub>bp</sub> and extrapolation to the y-axis A<sub>n</sub><sup>\*</sup>.

(b) The extracted parameters. Their variation for different biases is caused by non-ideal behavior of the Schottky contact. For example SRH-current is a good candidate to improve our model.

### 3.1.2 Forward

For forward biases greater then a few  $u_t$  the reverse current  $J_{nR}^{th}$  can be neglected. To characterize the series resistance we will follow the Cheung method [25]. Let us manipulate equation 3.2 to find the relation between the applied voltage and the series resistivity.

$$V_A = n \cdot u_t \ln J_{nF}^{th} A_n^* T^2 + nq\phi_{bp} + J_{nF}^{th} \rho_s, \qquad (3.4)$$

secondly we take the derivative to  $\ln J_{nF}^{th}$ :

$$\frac{\delta V_A}{\delta \ln J_{nF}^{th}} = nu_t + J_{nF}^{th} \rho_s. \tag{3.5}$$

In figure 3.2 (a) we show an example for different temperatures. The slope gives the resistivity. The intercept with the y-axis should give the ideality factor. Unfortunately the curves show a slight curvature close to the y-axis intercept due to non-ideal behaviour. This results in quite a lot of spread in the ideality factors and therefore we should use another method to extract the ideality factor. In figure 3.2 (b) we show the extracted series resistance for different temperatures. Note that the resistance increases with temperature indicating the semiconductor as a plausible cause.

Figure 3.2: These graphs illustrate the extraction of the series resistance of a Cobalt on n-type silicon Schottky barrier. (a) An  $\delta V/\delta \ln(I)$ versus I plot as proposed by Cheung [25], the series resistance  $R_s$ is extracted from the slope. (b) The extracted series resistance increases with temperature, the silicon is a plausible source of the resistance.

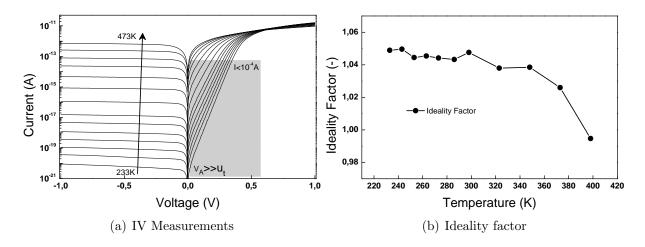

In figure 3.3 (a) we show the IV characteristics for different temperatures. For forward biases greater then a few  $u_t$  and currents below 0.1 mA both the reverse current and the series resistance can be neglected. This is indicated by the grey area in the graph. In this region the ideality factor is given by:

$$\frac{\delta \ln(J/T^2)}{\delta V_A} = 1/(n \cdot u_t). \tag{3.6}$$

If the current in the junction is mainly determined by thermionic emission we will find an n close 1. If other effects are playing a dominant role we will find a much larger n. In graph 3.3 we show the extracted ideality factor. For temperatures above 360 K the series resistance starts to play an important role and hence this technique becomes less accurate.

Now we have found the series resistance and the ideality factor it should be possible to find both the barrier height and the Richardson constant for forward biases. Let us manipulate equation 3.2, we find:

$$\ln(J_{nF}^{th}/T^2) + J_{nF}^{th}\rho_s/u_t = \ln A_n^* + V_A q/nkT - \phi_{bp}q/kT.$$

(3.7)

The result is similar to equation 3.3 except it incorporates the influence of the series resistivity and applied voltage divided by the ideality factor. Again a Richardson plot can be made and the parameters can be extracted. The method is dependent on the

Figure 3.3: (a) the measured IV characteristics. The grey area illustrates where both series resistance and reverse current can be neglected. (b) The extracted ideality factors.

previously extracted parameters  $R_s$  and n, therefore the extracted parameters are prone to errors.

In figure 3.4 we show the extracted parameters for both forward and reverse biasing. The barrier height shows a variation of 0.02 eV. Because the extrapolated reverse current shouldn't incorporate SRH and other non-ideal effects, we believe that the barrier height just on the negative side of zero bias is the most correct one. We find 0.69 eV for the barrier height. The Richardson constant shows a variation of 40  $\text{Acm}^{-2}K^{-2}$  and the extracted Richardson constant is 120  $\text{Acm}^{-2}K^{-2}$ .

Figure 3.4: Extracted forward  $V_A > 0$  V and reverse  $V_A < 0$  V Richardson constant and Schottky barrier height. We believe that the values for very small reverse bias suffer the least from influence of secondary effects.

# **3.2** Test Devices

We studied current voltage characteristics [26] for different metal contacts on lowly doped silicon fabricated in the MESA+ cleanroom <sup>2</sup>. As starting material 4 inch bulk Si(100)wafers were used having a specific resistance of 5 $\Omega$  cm for the p-type and 10 $\Omega$  cm for the n-type substrates. First a 100 nm thick thermal oxide layer is grown. After the definition of the contact holes the silicon contact area was cleaned using 100% HNO<sub>3</sub> to remove organic contaminants, 69% HNO<sub>3</sub> at 95 ° C to remove metal contaminants and finally they receive an 1% HF dip to remove native oxide. Following this cleaning procedure, the metal was sputtered and patterned using standard photolithography and wet chemical etching. After this the backside of the wafer was covered with the back metal to form an ohmic contact.

The mask contained a range of contact sizes form  $10 \cdot 10 \ \mu m^2$  to  $1000 \cdot 1000 \ \mu m^2$  to check for possible area dependency of the extracted barrier heights. All results presented here are from contact areas of  $200 \cdot 200 \ \mu m^2$ .

The following metals were chosen based on their general availability in IC processing facilities and the availability of a wet etch selective to Si and SiO<sub>2</sub>; aluminum (Al), cobalt (Co), molybdenum (Mo), palladium (Pd), erbium (Er), titanium (Ti) and titanium tungsten (TiW, alloy contains 10% Ti). Since the adhesion of pure Pd on SiO<sub>2</sub> was very bad we have co-sputtered a small amount of titanium, resulting in a film containing 0.5 atomic % of Ti, as determined with X-ray fluorescence(XRF). This small amount of Ti is assumed not to change the electrical properties so this mixture is abbreviated as Pd in this paper. Additionally we have tried a sputter target containing 7 % titanium (form Rutherford Backscattering spectroscopy, RBS). This film is believed to have electrical characteristics in between that of Ti and Pd.

For all metals we have used available sputter recipes in our microfabrication facilities for films between 100 and 500 nm. The electrical characterisation was done using a Keithley 4200 Semiconductor Parameter Analyser, a Cascade probe station equipped with a thermochuck. The IV characteristics were recorded between -60 °C and +200°C. After the highest temperature measurement a control measurement was done at room temperature to check the stability of the contact.

# **3.3** Characterisation Results

From the IV characteristics we derived the different Schottky barrier parameters using the techniques described in section 3.1. The results are shown in table 3.1. Each metal except Erbium was deposited both on n-type and p-type silicon. Hence all parameters have been extracted for both cases. If both barriers do not suffer from secondary effects, like image force barrier lowering, interface states, Fermi level pinning and tunneling, then  $\phi_{bn} + \phi_{bp}$  should equal to the bandgap of silicon which is  $E_G \approx 1.12$  eV. For both *Co* and *Mo* the sum of the barriers is 1.07 eV hence only 0.05 eV of the bandgap is consumed by secondary effects. Ti showed a surprisingly bad result with 0.65 eV.

Our final goal is to create a charge plasma diode. For good results we require the barrier to be as far from the center of the bandgap (>> 0.56 eV <<) as possible. To induce a plasma of electrons we will use the Er barrier because it has a high  $\phi_{bn}$ , an high  $A_n^*$  and n close to 1, indicating close to ideal behavior. To create a plasma of holes we

<sup>&</sup>lt;sup>2</sup>By courtesy of B. Rajasekharan

| Material             | $\phi_{bp}$ | $\phi_{bn}$ | $A_n^*$       | $A_p^*$             | $n_n$      | $n_p$       |

|----------------------|-------------|-------------|---------------|---------------------|------------|-------------|

|                      | (eV)        | (eV)        | $(A/cm^2K^2)$ | $(\dot{A}/cm^2K^2)$ |            |             |

| Ideal                | > 0.56 <    | > 0.56 <    | 240           | 80                  | 1          | 1           |

| Er                   | -           | 0.72        | —             | 140                 | 1          | 1.17        |

| Ti                   | 0.23        | 0.42        | ?             | 55                  | 1.4 - 1.13 | 1.16 - 1.48 |

| TiW                  | 0.42        | 0.50        | 4             | 80                  | 1.15       | 1.3         |

| PdTi <sub>0.5%</sub> | 0.76 - 0.82 | 0.12        | 4395          | 2                   | 1.05       | 1.97        |

| PdTi <sub>7%</sub>   | 0.69        | 0.29        | 20            | 12                  | 1.07       | 1.69        |

| Co                   | 0.69        | 0.38        | 115           | 12                  | 1.04       | 1.5         |

| Mo                   | 0.69        | 0.38        | 190           | 2                   | 1.04       | 2.06        |

| Al                   | 0.66        | 0.19        | ?             | 0.32                | 1.4 - 1.0  | 1.3         |

Table 3.1: Measurement Results on different metal silicon Schottky barriers.

will use  $PdTi_{7\%}$  because it shows both a low barrier to p-type silicon and  $\phi_{bn} + \phi_{bp} = 0.98$  eV which is quite large compared to Al were we find 0.85 eV.  $PdTi_{0.5\%}$  could be a better option, unfortunately it suffers from silicidation which we will discuss in section 3.4.

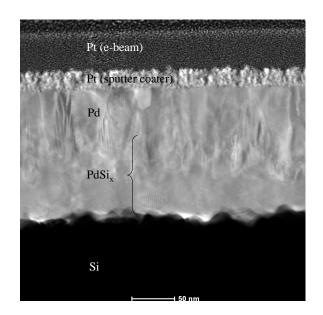

# **3.4** Silicidation of $PdTi_{0.5\%}$

During the first characterization of  $PdTi_{0.5\%}$  the barrier height  $\phi_{bp}$  showed a strong dependency on the temperature. Depending on which temperature data was used a barrier height between 0.75 eV and 0.82 eV could be extracted. During a second measurement this dependency was gone. This deviation during the first measurement can be explained by silicidation. At temperatures as low as 100 °C paladium-silicon (PdSi) is formed. Each IV recording takes at least 10 minutes time hence the sample has plenty of time to form a 50 nm thick layer silicide layer during the measurements cycles. A change in the metal resulted in a change of the barrier height.

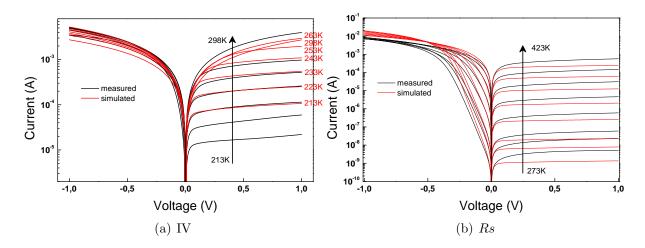

In figure 3.5 we show a TEM recording of the  $PdTi_{0.5\%}$  on n-type silicon junction. The Pd has reacted with the Si and formed a silicide. To evaluate our finding we performed a second series of measurements. The Richardson plots of the first and second series are shown in figure 3.6. Using the low temperature data only we extracted a barrier height of 0.76 eV for the first and 0.72 eV for the second series. These barrier heights were used as an input parameter for a device simulator [22]. From the output we extracted Richardson plots which are also shown in the graph. These clearly confirm the reduction of the barrier height, resulting from silicidation at temperatures above 100 °C.

# **3.5** Verification and Simulation

In the rest of this work we will show simulation results on the aMSM- and CP-diode. The extracted barrier height of Er and  $PdTi_{7\%}$  will be used as an input parameter to a device simulator. For the CP-diode both the Richardson constant and ideality factor do not play an important role. Hence we will not use these as input parameters in the simulator. To verify the simulator results we can compare the measured and simulated IV characteristics of a Schottky diode.

In figure 3.7 (a) we show the IV curves for the Erbium on n-type Schottky barrier. The temperature dependence of the simulations and measurements is comparable, there-

Figure 3.5: A TEM cross section of the PdTi on silicon junction. The lower part of the PdTi has reacted with the silicon and formed PdSi. This resulted in a reduced Schottky barrier height. (recorded by MiPlaza, Eindhoven)

Figure 3.6: The Richardson plot for the  $PdTi_{0.5\%}$  on n-type silicon devices. The barrier height  $\phi_{bp}$  can be extracted from the slope of the graphs. The second measurement shows a lower barrier height which is caused by silicidation during the first measurement. Both extracted barrier heights have also been used as an input parameter in a device simulator. The simulated Richardson graph confirms that the change in the Richardson graph is a result of a change in the barrier height.

fore the barrier height is modeled correctly. Under reverse bias  $V_A > 0V$  both show a comparable voltage dependence. Therefore the SRH-model of the simulator matches to the measurement data. Therefore we conclude that the Schottky barrier height is a valid parameter to model the characteristics of a Schottky barrier, and therefore the simulator is a valid tool to model the characteristics of the CP- and aMSM-diode.

In figure 3.7 (b) we show the measured and simulated IV characteristics for the  $PdTi_{7\%}$  p-type silicon junction. Again the temperature dependence is comparable hence the barrier height is modeled correctly. The measurements show a strong voltage dependence for negative voltages. A probable reason for this is SRH generated current. The extracted n of 1.69 also indicates that not only the thermionic emission current plays a role.

Figure 3.7: Simulated and measured IV curves. (a) for the Er on p-type Si barrier and (b) the  $PdTi_{7\%}$  on p-type Si barrier. Both show relatively good matching temperature dependence and hence barrier height. Therefore the simulator with the barrier height as an input parameter is valid tool to model the characteristics of the CP and aMSM-diode.

# Chapter 4 Simulation

### 4.1 The aMSM-diode

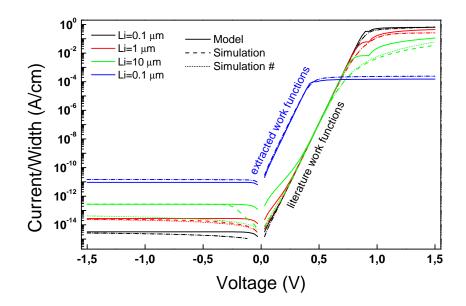

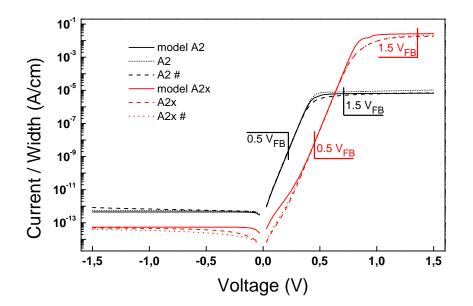

In this section we will use two-dimensional simulation results to show that the model proposed in section 2.2 gives a good estimate for the current in aMSM-diodes. More details on the exact parameters of the structure and models in the simulator can be found in section B.3. In the simulations the voltage on the p-metal gate was swept from 1 to -1 volt with the substrate and the n-gate biased at zero volt. Followed by a sweep of the n-gate from -1 to 1 Volts while both the p-gate and substrate were biased at zero Volts. In figure 4.1 we show the IV characteristics for an aMSM-diode with Li = 0.1 were work functions were employed extracted from our experiments or from the literature, see table B.2 for their exact values.

The modeled and simulated characteristics are very comparable. The most important deviations can be observed in the far forward regime. Here the voltage is bigger than the flatband voltage. In our theory we used either the drift or the diffusion equations to find the current. In reality both of them have to be solved simultaneously to find a good model for the current in for high forward voltages. In figure 4.1 we present the results for a diode with workfunctions according to literature, ( $\phi_{mn} = 4.20 \text{ eV}$ ,  $\phi_{mp} = 5.10 \text{ eV}$ ) as discussed in section B.2), and varying length Li. The SRH-current is heavily dependent on Li and shows up for reverse ( $V_A > 0$ ) and small forward biases. For the small forward biases the SRH-current in the simulation is much lower then in our model. The discrepancy of the latter is not clear yet. In far forward the current in the intrinsic region becomes limited by drift, which scales inversely with Li.

The length of the intrinsic gate Li is the only parameter of the aMSM-diode which can be scaled. By increasing the length both SRH-current (and off current) will increase and the far forward might decrease. Hence one would prefer a short Li although there is a situation where a long Li is preferable. The field across the silicon increases with reverse bias. When this field becomes high enough an avalanching current will start to flow. This field can be reduced by increasing the length Li of the silicon. Hence the aMSM-diode with ideal work functions can either be optimalized by scaling Li for a high reverse breakdown voltage and low far forward current, long Li, or a low reverse current high high far forward current, short Li.

Figure 4.1: (a) The simulated and modeled IV characteristics of an aMSMdiode with either literature or extracted metal work functions and geometries as in appendix B.2, in the simulations we swept either the voltage on the p-gate (indicated by dashed lines), or the n-gate (dotted lines) For the literature work functions we show the current dependence on the length of the intrinsic region Li. In reverse the currents increases with Li due an increased SRHcurrent. In forward the current decreases with Li

### 4.2 The Charge Plasma Diode

In this section we will discuss some simulation and modeling results on the CP-diode. Here the substrate is always biased at zero Volts, unless states otherwise. Often we will use device A2x from the tabels B.4 and B.5. The most important parameters are  $tsi = 20nm, Ln = Li = Lp = 2 \ \mu m, \phi_{mn} = 4.20 \ eV, \phi_{mp} = 5.10 \ eV$  and  $tbox = 1 \ \mu m$ .

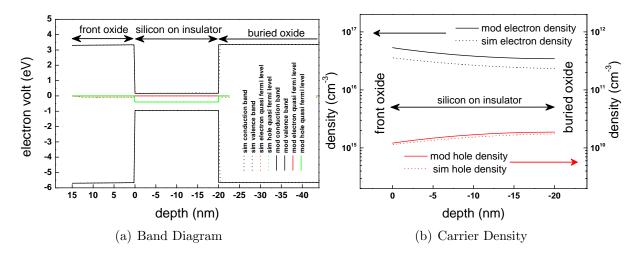

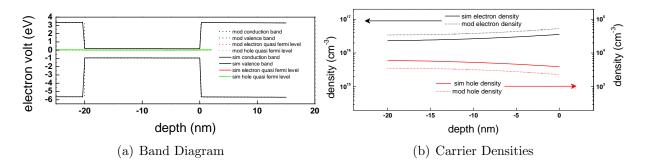

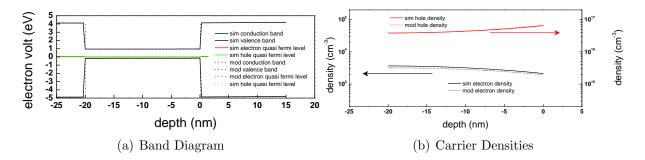

### 4.2.1 Charged Plasma

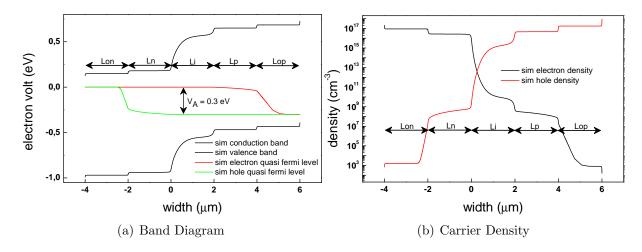

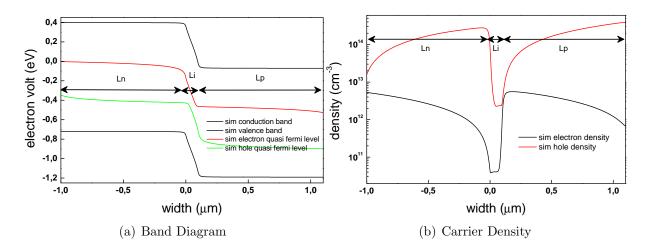

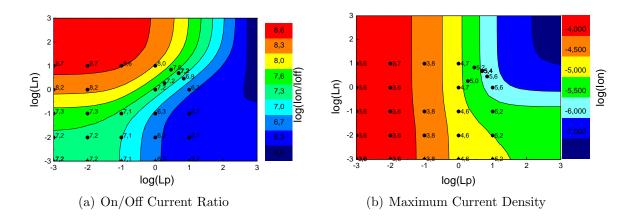

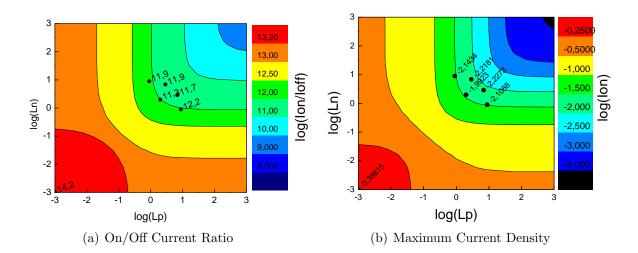

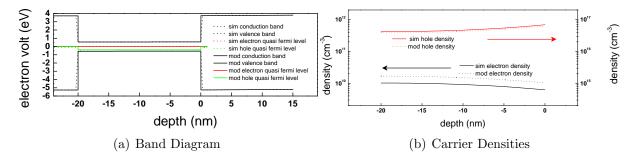

In section 2.3.2 we derived a formula in which electrostatics under the gates have been incorporated, see equation 2.42. In figure 4.2 (a) we show the simulated and modeled conduction band, valence band, hole and electron quasi Fermi level under small forward bias. For a comparison both oxide conduction bands energy level at the oxide metal interface have been used as a reference. The forward voltage results in a distance  $V_A$ between both quasi Fermi levels in the silicon. In this example the work function of the metal gate is 4.2 eV, the silicon electron affinity is 4.07 eV. Therefore the metal pulls down the surface potential in the silicon. This results in a low field in the front oxide and silicon.