### UNIVERSITY OF TWENTE.

MASTER THESIS

### Handfish - Tunable heterogenous multi-core simulators on multi-core hosts

| Author:                | Supervisors:                          |

|------------------------|---------------------------------------|

| Donker, J.H (s0088412) | Smit, prof.dr.ir. G.J.M. (UT-CAES)    |

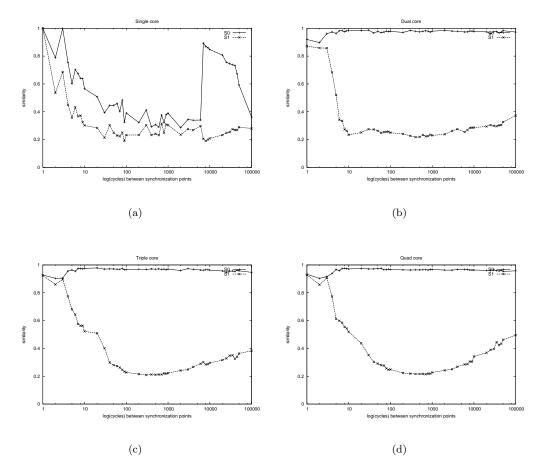

|                        | Kokkeler, dr.ir. A.B.J (UT-CAES)      |

|                        | ter Braak, ir. T.D. (UT-CAES)         |

|                        | Sunesen, dr. K. (Recore Systems B.V.) |

|                        |                                       |

July 17, 2012

"In the authors opinion, entirely too much programmers' time has been spent in writing such [machine language] simulators and entirely too much computer time has been wasted in using them"

Donald Knuth, renowned computer scientist and Professor Emeritus at Stanford University

"Handfish are small fish, growing up to 15 centimeters (5.9 in) long, have skin covered with denticles (tooth-like scales), giving them the alternate name warty anglers. They are slow-moving fishes that prefer to 'walk' rather than swim, using their modified pectoral fins to move about on the sea floor."

Wikipedia on Handfish

ii

## Abstract

In recent years we have seen the rise of the heterogeneous System on Chip. It is no longer uncommon to include multiple divergent cores in a single chip. These cores might be from very different vendors who each ship simulators for their core. This makes creating a simulator of the whole chip difficult since these simulators can not be efficiently combined. Most current approaches do not allow the user to take advantage of the multi-threaded capability of such systems or they do not allow the user to make a trade off between simulation accuracy and performance.

The goal of the Handfish framework is to facilitate the creation of heterogeneous multi-core System on Chip simulators. The focus lies on developing techniques to combine simulators and to allow them to take advantage of the multi-threaded nature of today's host computers. Since not all simulations need the highest level of accuracy, the framework allows the strictness to be decreased in exchange for more performance. This is achieved by changing and/or tuning the synchronization strategy of the constituent simulators.

A simulation algorithm has been developed that uses networking patterns to communicate between the components and that allows different instruction set simulators to be combined into a single simulator with a tunable level of accuracy. The implementation of this algorithm is combined with a simple instruction set simulator to get a better overview of the effects of changing the simulation strictness and the performance of the framework.

The simulator framework has also been used to combine two different instruction set simulators to create a heterogeneous simulator of a systems with two digital signal processors and one general purpose processor besides various homogenous simulators. iv

## Acknowledgments

What you see here is the end of a long journey at the University of Twente, longer than I care to mention (2004). While I started out as an Applied Physics major, now I am finishing as a master of computer science. And for that I want to thank my parents for always supporting me unconditionally throughout the years in whatever crazy thing I did. Without your unconditional support I would have never gotten here.

Secondly I would like to thank my supervisors André, Timon, Kim and Gerard for letting me have a free reign over my thesis subject and for reading some of my long and terrible drafts yet still having meaningful comments and the discussions about the work. I would also like to thank my employer Recore Systems for allowing me to work there part time after my internship and allowing me to use/abuse the Xentium simulator in some of my experiments.

I am also indebted to my friends. I would like to thank Nico Vermeulen for taking the time to read this thesis from time to time. Which was probably a very confusing thing to do with a background in philosophy and industrial design. I am also thankful to Arnoud Mulder for the technical discussions about some aspects of the work. Of the friends that did not help out in a technical or writing sense I would like to thank Fred Kaggwa, Recep Altun, Teo Willink, Jennifer Naumann and Robin Peters for their moral support during this period. To rest of you that I did not mention, I am also grateful that all of you where there, and listened to my stories and frustrations. (Probably more than a few of you thought that was going mad or at least losing my mind)

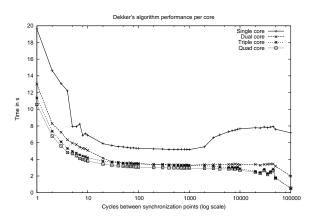

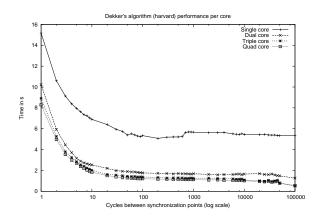

In terms of work, I can honestly say working on Handfish was in general fun, there were times when I thought I had seriously gone into a very deep swamp. The problem with creating such a piece of software yourself is that you can only blame yourself when you screw up. And of course I did a couple of times (The "nicest" one was the inverted inner loop condition with Dekkers algorithm which made it unfair under lax synchronizations...). In the end I was often surprised by the behavior of Handfish , so it only seems appropriate to name it after a somewhat strange fish that walks with its hands instead of swims.

João Henrique Donker, Enschede

vi

# Contents

| 1 | Intr                           | Introduction                        |    |

|---|--------------------------------|-------------------------------------|----|

|   | 1.1                            | Types of SoC's                      | 2  |

|   | 1.2                            | Development of SoC's                | 4  |

|   | 1.3                            | Simulation in general               | 6  |

|   | 1.4                            | Handfish                            | 8  |

|   | 1.5                            | Conclusion                          | 9  |

| 2 | Related work 1                 |                                     | 11 |

|   | 2.1                            | Multi-core simulation               | 12 |

|   | 2.2                            | Interoperability                    | 18 |

|   | 2.3                            | Conclusion                          | 20 |

| 3 | $\operatorname{Res}$           | Research questions 2                |    |

| 4 | Models of multi-core execution |                                     | 23 |

|   | 4.1                            | Properties of trace graphs          | 26 |

|   | 4.2                            | Trace to trace graph transformation | 28 |

|   | 4.3                            | Conclusion                          | 30 |

| 5 | Arc                            | hitecture and implementation        | 31 |

|   | 5.1                            | Architectural component breakdown   | 33 |

|   | 5.2                            | Algorithms                          | 34 |

#### CONTENTS

|   | 5.3     | Scheduling algorithm          | 36 |

|---|---------|-------------------------------|----|

|   | 5.4     | Sub-simulator modification    | 38 |

|   | 5.5     | Implementation                | 41 |

|   | 5.6     | Conclusion                    | 43 |

| 6 | Exp     | perimental case studies       | 45 |

|   | 6.1     | Expectations                  | 45 |

|   | 6.2     | Methodology                   | 45 |

|   | 6.3     | Functional                    | 47 |

|   | 6.4     | Performance                   | 49 |

|   | 6.5     | Conclusion                    | 53 |

|   |         |                               |    |

| 7 | Inte    | egrating other sub-simulators | 57 |

|   | 7.1     | Xentium multi-core simulator  | 58 |

|   | 7.2     | Heterogeneous simulator       | 58 |

|   | 7.3     | Homogenous Xentium simulator  | 60 |

|   | 7.4     | Other sub-simulators          | 60 |

|   | 7.5     | Conclusion                    | 62 |

| 8 | Con     | Conclusion                    |    |

|   | 8.1     | Tunable                       | 65 |

|   | 8.2     | Heterogeneous                 | 66 |

|   | 8.3     | Multithreaded                 | 66 |

|   | 8.4     | Other requirements            | 67 |

|   | 8.5     | Conclusion                    | 67 |

|   | 8.6     | Discussion                    | 67 |

| 0 | <b></b> |                               | 00 |

| 9 |         | ure work                      | 69 |

|   | 9.1     | Functional analysis           | 69 |

|   | 9.2     | Synchronization strategies    | 70 |

#### CONTENTS

|              | 9.3 Optimizations                                   |    |

|--------------|-----------------------------------------------------|----|

|              | 9.4 Expansion                                       |    |

| A            | Detailed requirements                               | 71 |

| в            | B Memory consistency models                         |    |

| С            | 2 Simplium simulator 7                              |    |

| D            | Dekkers algorithm                                   |    |

| $\mathbf{E}$ | E Observed trace graph                              |    |

| $\mathbf{F}$ | Explorations of quantitative functional performance |    |

|              | F.1 Graph similarity                                | 87 |

|              | F.2 What does similarity mean?                      | 89 |

|              | F.3 Experiments                                     | 90 |

|              | F.4 Conclusion                                      |    |

| G            | Heterogenous simulator                              | 95 |

ix

CONTENTS

# Abbreviations

| ABI<br>ADC<br>ASIC | Application Binary Interface.<br>Analog-to-Digital Converter.<br>Application Specific Integrated Circuit. |

|--------------------|-----------------------------------------------------------------------------------------------------------|

| CRISP              | Cutting edge Reconfigurable ICs for Stream Processing.                                                    |

| DSP                | Digital Signal Processor.                                                                                 |

| IP<br>ISA<br>ISS   | Intellectual Property.<br>Instruction Set Architecture.<br>Instruction Set Simulator.                     |

| NoC                | Network on Chip.                                                                                          |

| RISC<br>RTL        | Reduced Instruction Set Computing.<br>Register Transfer Level.                                            |

| SoC                | System on Chip.                                                                                           |

| TLM                | Transaction Level Modeling.                                                                               |

| UART               | Universal synchronous receiver/transmitter.                                                               |

| VLIW               | Very Large Instruction Word.                                                                              |

|                    |                                                                                                           |

Glossary

xii

### Chapter 1

## Introduction

Process miniaturization and the decoupling of Intellectual Property (IP) design from manufacturing of Application Specific Integrated Circuit (ASIC)'s has given rise to the System on Chip (SoC). Increasingly a whole system is composed from multiple IP blocks to create a bespoke chip. This is possible since digital design languages like VHDL and Verilog have made it easy to share designs and it is now possible to build a complete computer in a single chip package. Consider a company that wants to make a chip for a GPS receiver. The company takes several off the shelf IP blocks (designs) and then uses these to create a dedicated GPS receiver chip. The used IP blocks might be a general purpose processor IP from one vendor, a Network on Chip (NoC) interconnect from another vendor and some custom ASIC to accelerate specialized operations. But without software the SoC is just a piece of silicon of which the potential is left untapped. So like most modern systems a SoC contains hardware and software that are designed together.

Sourcing IP blocks from multiple vendors has the the advantage that a vendor does not have to design everything from scratch. Yet it also means that the integrator has to try and integrate different pieces of work scrambled together from various sources. Firstly all the hardware components have to communicate with each other. Secondly many IP blocks come with software to simulate and/or debug them. But often these pieces of software do not communicate well with each other. (For example the provided Instruction Set Simulator (ISS) is written in an esoteric language and the sources are not available) So it is hard to create a whole system simulation in which all aspects are simulated. Software that is written for a SoC with multiple architectures might also need to take into account that the endianness differs among architectures and that they might have different behavior with regard to simultaneous memory accesses. All these factors must be taken into account when creating a designing and simulating a modern SoC.

First we will have a look at the types of SoC's and look at how they are developed. We also take into account how the software and the hardware are designed together. But in this report we will mainly focus on how pieces of software are developed in the absence of real hardware.

#### 1.1 Types of SoC's

A SoC is a chip that contains multiple diverse IP blocks that together form a system. Such a system can take on multiple forms. A simple SoC might just include a simple processor, some memory and a number of peripherals. While the most advanced SoC's include a large number of heterogenous IP blocks connected via a NoC. This does not mean other interconnects do not exist, but they are far less common.

There are three mainstream types of SoC's

- Single-core

- Homogenous multi-core

- Heterogenous multi-core

A single-core SoC will in general only have a processing core with some memory and some peripherals like a Universal synchronous receiver/transmitter (UART) and an Analog-to-Digital Converter (ADC). A multi-core SoC that is homogenous will normally have multiple processors but they will all be of the same architecture. An example of such a multi-core SoC would be a quad core ARM SoC that is used in a tablet PC. Heterogeneous multi-core SoC's can contain many different types of processors that do not even have to share the same instruction set architecture. Because certain architectures or different implementations of a architecture might have properties that are desirable in different situations. An example of a SoC that uses different architectures is the TI OMAP chip [4], which contains an ARM core and a proprietary Very Large Instruction Word (VLIW) Digital Signal Processor (DSP) core. The ARM core handles general purpose computing tasks while the VLIW DSP handles the computational intensive tasks like video decoding.

One of the challenges within the domain of SoC design is interconnecting all of these components in a way that each individual component gets the resources they need to function optimally. Resources might be memory or even bandwidth to access memory. The components can be interconnected in the following ways.

- Hierarchy of buses

- Network on Chip

- Combination of a hierarchy of buses and a network on chip

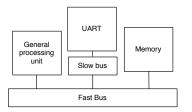

Using a hierarchy of buses is a traditional technique for creating computing systems. A bus means that there is a shared medium to which the devices

are connected an example can be seen in figure 1.1 This interconnect can even be something as simple like a wire with multiple connections. Because not all component are equally fast often a hierarchy of buses is created. A hierarchy of buses compensates for speed differences between components. It gives each device the bandwidth it needs without interfering with devices operating at different speeds.

Figure 1.1: Example of a simple SoC with a bus

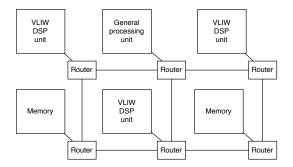

The NoC paradigm is newer and is used more often in embedded systems. [22] [12] [30]. The principle behind a NoC is that the interconnection between the different devices is seen as a switched network. In this switched network all components are connected to a router which contains the connection the the neighbors. An example can be seen in figure 1.2. The main difference between a bus and a NoC is that the NoC is fully connected to its neighbors but can only reach farther away components by traversing multiple routers. This allows a system to have more parallel transactions since communication does not happen in the same shared medium like with a bus.

Parallel transactions occur when the processors are doing simultaneous work and are reading and writing the data to each other like for example in a streaming application. Examples of NoC s include the work of Pascal Wolkotte and Nikolai Kavaldjiev at the university of Twente [57], the Cutting edge Reconfigurable ICs for Stream Processing (CRISP) consortium General Stream Processor (GSP) [12] and the Intel's polaris chipset [30]. The GSP RFD (Reconfigurable Fabric Device) chip contains 9 Xentium cores connected via a NoC , while the Polaris chip contains 80 simple cores connected via a NoC . The big advantage that a NoC brings is that traffic that travels nearby does not affect the rest of the system. The smaller distances that the wires have to cover also have the advantage that the latencies for nearby communication are shorter. The disadvantage that a NoC has is that in larger systems the data has to travel through many steps, which makes long distance communication slower. Since the signal has to pass trough multiple wires and multiple pieces of combinatorial logic to reach the final destination.

In a combination of a Network of Chip and a bus system one can imagine that the high performance components are connected to a NoC while slower components are joined together on a bus connected to the NoC.

Often a SoC contains two distinct parts, namely the control part and the data processing part. The control part deals with IO and the monitoring of the application and normally runs on a general purpose processor. While the data processing part does the numerical processing and is normally done by an ASIC,

Figure 1.2: Example of a SoC with a NoC

DSP or a reconfigurable part. Often the control part and the data processing part use different architectures with incompatible Instruction Set Architectures (ISA). An example of such a heterogeneous platform is the CRISP consortiums GSP platform. The control part is handled by an ARM processor while the actual data processing happens on the 5 RFD chips, which together house 45 Xentium cores.

#### 1.2 Development of SoC's

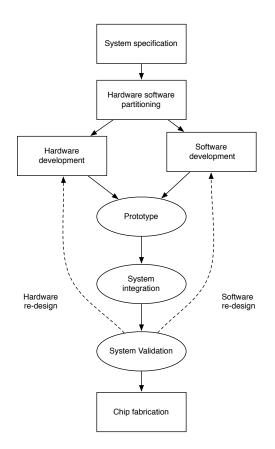

In SoC development software and hardware are designed together. The design often begins with a specification of the desired goals for the SoC.

The development of a new System on Chip for a given application goes through a number of phases. These phases are described in the book by Ghenassia [20].

First the specifications of the SoC are determined based on the commercial or scientific requirements. These specifications and requirements dictate the performance and the feature set of the SoC. In the second stage the design space is explored by running theoretical simulations of the workload. During this stage it is also determined which part of the application will be implemented on which kind of hardware (ASIC, DSP, Reconfigurable tile) or if it will be implemented in software.

From this stage onwards the design teams are split into separate hardware teams and software teams. The hardware teams set out to integrate the IP blocks and to create the new blocks needed. While software teams set out to create the algorithms needed for the data processing part, the control part of the application and the software glue to tie it all together. In an ideal world there is plenty of communication between both teams to ensure that the integration between hardware and software is seamless.

It is at this stage the first challenges begin. Since hardware without any type of software is not going to do anything, new software has to be written for the new chip or old software has to be ported. Since the chip is still in development

Figure 1.3: Soc design flow

it does not exist yet so the obvious solution is to simulate the hardware at different levels of detail. The hardware team run very accurate simulations that simulate everything the chip is doing with so-called gate level simulations. The software team uses less accurate simulators namely instruction set simulators which just simulate the programmer visible details but in exchange are faster.

Since often the data processing and the control part of the software running on the SoC are of different architectures, the complete software stack is often simulated in an RTL simulator. This has the major disadvantage that these simulations contain too much detail for software development. To get some feeling of how the actual hardware will function the hardware is prototyped with the help of FPGA's. The integration of the hardware and the software often leads to redesigns of the software and hardware. Since the software might have become dependent on the timings of the simulation and has unexpected behavior when operating on the real hardware, while the hardware might have subtle bugs that are triggered by the software.

One of the bigger problems with simulating new and advanced SoC's is that the number of cores often exceeds the number of cores in the system hosting the simulation. Currently most simulation environments do not take advantage of multiple cores, since it is harder to get repeatable results and the overhead of keeping all the cores in synchronization can become large when the workloads are interconnected.

#### **1.3** Simulation in general

While simulation is currently a mature subject in computer science, this does not mean that no research is being done into improving simulation. One area of research is to achieve a better balance between speed and cycle accuracy. There are many types of simulation possible depending on the level of detail required. These approaches span from low level (simulating all the gates) to high level (functional simulation of the program).

At the moment there are a number of techniques available for simulating processors

- Gate level

- Register transfer level

- Instruction set simulators

Gate level simulation is the most detailed and most true to actual hardware. In a gate level simulation all the details are simulated ranging from the delays in the gates to the exact timing of a system. In even more elaborate simulations power consumption can also be taken into account to get a realistic overview of how the future chip will perform. This is often done in the later stages of development of a chip since running such simulations is very time consuming due to the level of detail.

The Register Transfer Level (RTL) approach simulates the whole chip down to the the digital logic, but physical elements like propagation times are not simulated. This allows a design to be tested quite extensively for logic design errors but unlike gate level simulation, it abstracts from the realities of a real chip. However the level of detail is still too high to do effective simulation of software running on such a platform. On a real system not all the state is visible for a programmer so these kinds of simulations often provide too much information for software development.

An example of an RTL simulation is ModelSim [37]. ModelSim simulates a whole digital design down to the actual register level. Since it can be used to simulate a whole processor and is often used to get a precise indication of how a new processor will perform in real life. This technique produces the closest result to real life, with the the disadvantage of being slow due to the amount of detail provided by the simulation.

Most RTL and gate level transfer vendors provide an integrated suite which contains tools to do both kinds of simulations. But both kinds of simulation suffer from the same set of drawbacks, since running real workloads on them is often too slow to do software development on real life designs.

#### 1.3.1 Instruction Set Simulators

Interpretation and compilation can usually be grouped together as instruction set simulators. An ISS is a computer program that simulates enough of an instruction set and the surrounding programmer visible detail to run programs designed for that computer. In some simulators just a subset of the architecture is simulated while other simulators simulate enough of a system to run an operating system with applications on them.

First it is important to know that there are three types of instruction set simulators, namely:

- Source interpreters

- Binary interpreters

- Compiled simulation

The first type of simulation takes in the assembly files. The assembly instructions are interpreted from their textual form that might include some high level constructs like labels, register names and maybe some extra debug statements. The interpreter maintains a model that includes the registers and the memory of the system. This allows the whole state of the system to viewed at each step, which allows the user of the interpreter to get an understanding what the program does. The main usage of these kinds of simulators is to debug the initial programs of the project. This approach is quite slow since each instruction has to be parsed and interpreted. But it these kinds of interpreters have the advantage of being more user friendly for programmers since they give a more familiar perspective on the programs that are running. This perspective is more familiar since the developer sees the program interact on the level at which they are programming. An example of such a simulator is the MIPS assembly simulator MIPSim [39].

Binary interpreters accept binary instruction images as their input. The instructions are decoded and interpreted one by one in such a fashion that the the simulated results are identical to results achieved on real hardware. This technique is often used in cases where the architecture simulated is very dissimilar from the target architecture or when trying to simulate a large number of processors. This technique allows for precise simulations because all details can be simulated in software. In general, binary interpreters are faster than source interpreters since binary execution images are simpler to decode than a textual representation. But in general they are more complicated to use since high-level details are stripped, making it more difficult to see what is happening. This can be overcome by using a debugger that has some knowledge about the source and how the application was mapped to it. An example of a binary simulator is the Xentium simulator made by Recore Systems[50].

Compiled simulation is a technique that can be used to increase performance. What happens is that the assembly file is translated to the native execution format of the underlying host. This allows for a speed up since the conversion only has to happen once. Some simulators and virtual machines will compile the most often used parts of the simulated environment while allowing less used or more complicated parts to be interpreted. This results in a speed up because code normally sticks to well defined code paths and will only occasionally sway from them. Examples of virtual machines that use binary compilation are the Java HotSpot virtual machine[46], VMKit [19] and Qemu [2]. Another example of binary compilation is Recore's libMontiumC which compiles montiumC to native x86 executables. This gives the user a fast functional simulation of the application [52].

The trend of SoC's had lead to many solutions being proposed since there is a need to simulate early on in the design process. Popovici et all. [48] take a look at the simulators that are commercially available for the development of SoC's. They show that the major tooling suppliers provide pieces of the solution, some provide tools to join different building blocks together via user friendly tools while others just claim support for interoperability via Transaction Level Modeling (TLM). They also show that the directions for future research could be: increasing performance, automatic generation of simulation models from off the shelf building blocks and simulators that allow a tunable level of detail. Directions for increasing performance include looking at improved just in time compilation techniques and looking at different levels of abstraction in the simulation.

#### 1.4 Handfish

In this report we will describe the Handfish framework, which is a simulation framework that allows a heterogeneous multi-processor SoC to be simulated by composing a simulator from different instruction set simulators. The framework is build on the concept of cooperating processes that communicate with each other via network patterns. Another feature of the Handfish framework is that it allows the strictness of the simulator to be changed, meaning that the points when the simulator synchronizes are a configurable property of the system. If more advanced synchronization is needed the Handfish framework also allows for the scheduling strategy itself to be changed. These features give the user of the framework the choice to decide between more accurate simulations or more performant simulations while taking advantage of the underlying multi-threaded nature of the host system.

In this report we will show the architecture of Handfish, how it performs and that it can be used to create varying types of simulators ranging from dual core homogenous simulators to many core heterogeneous simulators.

8

#### 1.5 Conclusion

In this chapter we looked at the basics of SoC development and at the basics of simulating a processor. In the following chapters we will use the concepts first described in this chapter and extend on them via existing literature and own research.

In chapter 2 we show what is the state of the art in simulation techniques. This includes a look into multi-core simulation frameworks and configurability. Chapter 3 presents the requirements for the to a proof-of-concept simulator that should address some of the shortcomings of current approaches. In that chapter each of the requirements will be matched with a verifiable goal to verify the proposed and implemented solution at the end. Chapter 4 describes the principles of multi-core execution in depth to form a basis for the next chapters.

Chapter 5 describes the basic design of a multi-core simulator that satisfies the demands presented in chapter 3. In chapter 6 we take a look at the how the Handfish framework performs with the Simplium simulator and in chapter 7 the framework is tested with a real of the shelf simulator. Afterwards we look at results as a whole in the conclusion in chapter 8 and in the discussion in chapter 9 we take a look at questions raised by this research.

### Chapter 2

## **Related work**

Simulation has been around in multiple forms for about 40 years in practice and even longer in theory. Turing equivalence states that any Turing complete architecture can simulate another Turing complete architecture. This means that given enough memory and computation time any computation that can be done on a complicated computer can be done on a simpler computer or the other way round. The earliest use of an ISS was to provide backwards compatibility with older machines. An example of this is the simulation of the IBM 1401 mainframe on the IBM S/360 in the seventies. Later on the concept was applied to software development for new hardware, architectural research, hardware partitioning and to ease hardware architecture transitions.

Simulation and virtualization are two related concepts and often techniques can be shared. Virtualization is simulating the same architecture as the host architecture. While simulation can also be simulating a different architecture from the host architecture. The big difference is that a simulator is slower because an actual translation step between the guest and the host is needed. A virtualizer can get away with some carefully intercepted instructions or even using special hardware support if the architecture supports the Popek Goldberg virutalization requirements [47], but an in depth discussion of these requirements is outside of the scope of this thesis. Current desktop and server processor have dedicated hardware support for virtualization that allows virtualized hosts to reach nearly the speeds of direct execution. Examples of this include Intel's VT-X [44], AMD AMD-V [6] and SPARC's hyperprivileged mode [56].

While a simulated guest can be a completely foreign architecture like a simulator for VLIW running on a Reduced Instruction Set Computing (RISC) host. Depending on the difference between the architectures and the level of detail of the simulation the speed can be quite different. For example a high level simulator for an ancient architecture can be many times faster than the real hardware while a very detailed simulator for a new processor can be many orders of magnitude slower than the real hardware.

#### 2.1 Multi-core simulation

Most instruction set simulators start out by simulating a single instance of a processor and often multi-core support is an afterthought. But recently a number of simulation frameworks have started to appear that take in to account the fact that multi-cores are becoming increasingly common. A few examples of multi-core simulators are SlackSim [11], Graphite [38], GEMS[35] and the work at National Tsing Hua University [58] [59].

In some cases, the detail of the simulation is limited to allow a larger work set to work on the simulator. In such cases often the workload of the simulator is described statistically. These kinds of simulations are most often used to explore the architecture initially since they give some insight into the theoretical performance.

The first simulator described in depth is Slacksim. It is presented first since it provides concepts that can be used to explain what strictness means in terms of simulation.

#### 2.1.1 Slacksim

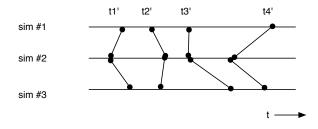

Slacksim implements an 8 core system that is simulated with 8 threads[11]. They begin their analysis by defining the concept of time in their simulator. In a multi-core simulator there are multiple "times". First there is the global time which describes the state of the whole system, there are the local times of the individual processors. And there is always the time on the clock. Slacksim simulates a maximum of 8 SimpleScalar PISA processors.

To describe these concepts they use so called time diagrams. In figure 2.1 an example of time diagram is given. In the time diagram the time on the clock is displayed along the X - axis. The horizontal lines represent simulated cores, and they are named sim #1 until sim #3. The points and vertical lines represent a single point in simulated time. In the picture they are named t1' to t4'. The figure shows that this simulation is initially synchronized. But later on the simulators start to go astray. For example simulator 2 t4' occurs earlier than simulator 3 t3'. This situation could lead to unexpected behavior if the applications executing on the simulator depend on the ordering in which read and writes occurs.

In their paper they sketch the violations that are possible in a simulated environment. They sketch out the following violations:

- Simulation state violations

- Simulated system state violations

- Simulated workload state violations

Figure 2.1: A simple time diagram

Simulation state violation are violations where events happen inside the simulator in a way that would be impossible in real life. An example of this is that two processor that are temporally in synchronization write to the same bus at the same time. These kinds of violations usually result in a different access order than on a cycle accurate simulator. Such violations are not observable from the code directly.

Simulated system state violations are not visible to the software running inside. Meaning that the software running inside the simulator can not detect that it is not running on real hardware. These might include violations where things like caches are in a different but not observable state than in a real system. Thus the hardware state of the simulator does not match with what would happen in real hardware.

Simulated workload state violations are violations that are visible from inside the software running on the simulator. An example of this would be that a thread sees a write that happened in the future according to its local time perspective. These are the most serious violations. These violations cause programmer visible errors in the simulation. Often these errors can be detected fairly easily by comparing the results against the result obtained from real hardware.

Violations like simulated workload state violations can be potentially hazardous since wrongly synchronized software might get into situations that are not possible on real hardware. An even more treacherous variant is that the software functions correctly on the simulator but fails on hardware. Well synchronized software will continue to function but will have slightly different behavior. An example is that a shared locking algorithm has to spin for more cycles to enter a critical section while running in a simulator. The effects on badly synchronized software are far more unpredictable, since the hidden data ordering dependencies might cause problems. They might cause the synchronization to break, which can lead to problems like non deterministic data corruption.

In their paper they mention a few techniques available to synchronize the simulation threads:

- Cycle by cycle

- Quantum based

- Bounded slack

• Unbounded slack

They describe slack as the difference between local time on the slowest simulator instance versus the local time on the fastest simulator.

In the cycle by cycle technique (also know as lockstep), the threads are synchronized with a barrier at the end of every cycle. This will result in accurate results but has the disadvantage that if the workload over the threads is asymmetric that certain threads will have to wait longer until they can continue because the other threads have to finish their processing.

The quantum based technique synchronizes the instances after a given number of cycles. This technique has the disadvantage that it allows simulation violations but has the advantage that less time is spend waiting for the threads to synchronize. The accuracy can be set by changing the length of the quantum.

Bounded slack is similar to quantum-based in the sense that that the slack of a single simulator instance will not be bigger than a set maximum. They define a window of how far ahead any instance may be from the global time, whereby the global time is defined as the lowest local simulator time. If some threads are too much ahead of the global time these instances have to wait. When the slowest instance advances, the window also advances so the other instances can continue. This is different from quantum based since in quantum based techniques the synchronization point is fixed, and the threads will wait until they all reach that point while in bounded slack only the fastest threads wait for the slowest.

Unbounded slack is the technique of not using any synchronization in the simulator itself and letting the code running in the simulator handle the synchronization. This scheme does give the maximum performance but it has the disadvantage that it will create a large number of violations since the simulator does not synchronize itself.

#### 2.1.2 Simulating a 1000 cores

An example of a simulation framework designed to simulate a massive multicore computer is given by HP's Moncheiro. [41]. In their paper they sketch out a simulator that can simulate one thousand cores. They are able to do this by separating the functional behavior from the timing behavior. But they lack the ability to simulate IO behavior like for example a UART. Their focus is to see how certain pieces of code would scale when they would run on systems with around a 1000 cores. In their simulator they simulate up to a thousand x86-64 cores using a modified version of AMD Cotson [8]. This allows the simulation to run real life workloads like operating systems and benchmarks.

Their simulator consists of a functional timing model and separate processor model. In their simulation the functional timing models feeds the separate processor model instructions. The processor model executes in parallel, the functional model adds instructions to the processor model. This approach has the advantage that it is quite simple to get synchronization to function correctly, since they can simply halt cores until everyone is at the right point in time.

Synchronization constructs are handled by annotating the instruction stream and waiting until every simulator reaches the synchronization point. But the system is not able to execute polling loops, so in the benchmarks these loops are removed to get a fairer overview of the performance.

This approach has the advantage that synchronization constructs can be detected and executed correctly. Because this approach also handles the timing information correctly, it allows the simulator to be used to get an idea how much faster an application will perform when running on a large scale multicore system.

#### 2.1.3 GEMS

GEMS (General Execution-driven Multiprocessor Simulator) [35] is a modular simulation framework where the system is divided in two parts. A memory interconnect simulation and a processor simulator. In their simulations they simulate any number of SPARC V9 cores.

The processor simulator is split up in two parts namely a highly accurate simulator for the most common instructions and a functional simulator for rare instructions. This allows the GEMS to to run real code that uses uncommon and hard to implement instructions while still being able to run cycle accurate most of the time. This allows it to run full operating systems and application benchmarks.

The memory subsystem of the simulator was designed so that it can be replaced with compatible components that can be used to simulate everything from a NoC interconnect to a bus system with caches.

#### 2.1.4 Graphite

Another example of a simulator designed for multi-core simulation is Graphite from MIT [38]. What makes graphite an interesting system is that the system was designed to simulate very large multi-core machines, in the order of thousands of cores. What makes Graphite different from the previously described system is that the goal of Graphite is to simulate a large multi-core system with an interconnect, while the goal of the previous project was to see the effect of large multi-core systems via simulations on applications. Graphite uses an innovative approach that in the sense that it does not use a full interpreter. It uses PIN [1] to modify the running binary so that all instructions and operations that are affected by multi-core execution are intercepted and interpreted in software. This means that all memory accesses instructions are intercepted while operating systems operations like thread creation are emulated by the system. The underlying simulation only simulates how the cores are interconnected. Graphite does not have inherent limitation to the number of cores that can be simulated since the simulation can even be split over multiple machines.

What makes the Graphite approach interesting is that it allows unmodified x86 binaries to be executed on simulated large multi-core computer. Thus the results provided by the simulator are achieved with real workloads. But they can only handle applications and can not simulate a whole operating system due to the reliance on PIN. Another even bigger disadvantage of this technique is that it can not be used to simulate a different architecture.

Graphite has also been used as a platform to explore various synchronization techniques for multi-core on multi-core simulators. The following techniques have been explored:

- Lax synchronization

- Lax synchronization with barrier synchronization

- Lax synchronization with point-to-point synchronization

The first two techniques are also present in SlackSim but they use different names. Lax synchronization is equivalent to SlackSim's unbounded slack and Lax synchronization with barrier synchronization is a tunable variant of quantum based synchronization. The real contribution they make is the introduction of point-to-point synchronization. In point to point synchronization the simulation continuously checks random simulation threads and compares the time between them. Pairs of simulations instances are randomly matched against each other. They use random sampling because it is a cheap heuristic. If one thread is too far ahead of the other it will pause the thread that is running to far ahead of the others.

In their research pure lax synchronization resulted in a very scalable and performant simulator but it has the problem that it will not faithfully represent interactions between cores. So in some cases violations will not appear and in other cases they will appear more pronounced than in real life. With barrier synchronization the performance and scalability are diminished while the accuracy improves. Point to point synchronization has the advantage that it is more accurate than plain lax synchronization while only having a small impact on the performance compared to using Lax Synchronization (10 percent slower).

#### 2.1.5 Distributed synchronization

Most of the current literature on instruction set simulator focuses on accelerating single core simulators, and multi-core simulators are often ignored. The work that has the most in common with this work is the work of Meng-Huan Wu et al [58] [59] at National Tsing Hua University. In their papers they show a distributed temporal synchronization scheme. Their approach approach consists of two different ideas. First they use static analysis of the binaries to get the information about the synchronization points in the software and they use distributed scheduling to keep the cores in synchronization.

Via static analysis of the executables before the simulation starts they precompute the points in time where each simulator needs to be synchronized with another simulator. With static analysis they first create a control flow graph of the executable which they then use to generate the earliest synchronization point for each simulator at runtime. Each simulator then monitors the other simulators if they are reaching a common synchronization point, and waits for the other simulator to reach this point if necessary.

The authors claim that this approach can increase the performance of multicure simulations because it allows all cores to remain busy which they claim is not possible in a model with a centralized scheduler. Their approach has been tested on dual and quad core simulators.

#### 2.1.6 Other simulators

Recore Systems[49] has a multi-core simulator for simulating the CRISP GSP platform <sup>1</sup>. This simulator is currently not available publicly but it uses lax synchronization in combination with blocking memory to synchronize the simulation. Thus the simulation can not completely go out of control since many synchronization actions happen with the help of blocking memory constructs. The CRISP GSP[12] platform allows the memory system to block a Xentium until the request has been handled. This simulator has been used to debug and extend a large multi-core application that used 39 cores. One of the features inside this simulator is that it can be down scaled up or down easily with the help of a configuration file. This allowed pieces of the software to be debugged in isolation. The system has been used to show that some pieces of software written for the platform had some synchronization problems.

Wieferink et al. [55] present a simulator that can use multiple ISA's at the same time. It was tested by having a MIPS processor and an accelerator interacting with each other. Their main contribution is the automatic generation of suitable instructions set simulators that can be combined with a NoC. They do not mention if the simulation can take advantage of multiple host processors. They use their simulator to build an accelerated JPEG decoder that takes advantage of the MIPS and the accelerator chip.

Other simulators exist that can simulate multiple processors such as Simics [54], Qemu [2], SimpleScalar[51]. But they all rely on sequential execution. This has a few advantages for example that each run is exactly reproducible and in the case of Simics the execution can even go backwards in time. (which can be useful in debugging some situations) The disadvantage of these simulators is that they can not use more than one thread. Which prevents a simulator from fully taking advantage of modern multi-core hosts. Another disadvantage is that because they always provide the same deterministic run they will not be able to simulate all situations that might occur in real life.

<sup>&</sup>lt;sup>1</sup>The author is intimately familiar with this piece of software.

A good example of a virtual machine tuned to debugging is Valgrind [45]. Valgrind translates real life x86 binaries to a RISC like format. This allows the program execution to be monitored in great detail. The main use of Valgrind is to determine if memory allocations are correctly deallocated.

But Valgrind also includes a tool to designed to find data races and deadlocks, which they call the Helgrind tool [42]. It does this by using the Eraser algorithm. The Eraser algorithm checks the memory accesses at runtime to see if they cause races. It does this by checking if each operation to memory happens while the operations are locked. If this is not the case, the algorithm will report a data race. In Helgrind, the algorithm is extended with some knowledge about the code running on top to prevent false positives and the lock mechanism is also extended to model the bus of the system. If the operations happen while that piece of memory is unlocked it will alert the user that there is a race condition. But a race condition does not imply that a piece of code is flawed. Since for example locking algorithms depend on race conditions to function, but in general most data races in software are unintentional.

#### 2.2 Interoperability

Another development of the recent years is that SoCs are getting more heterogeneous. Often it is the case that a simulator has support for only a single Instruction Set Architecture (ISA). This often leads to trouble when trying to write software for a heterogeneous SoC since each ISA uses a slightly different tool-chain that can be hard to integrate with other tool-chains.

In principle all blocks of IP can communicate with each other in a RTL or gate simulation. Since if something can work together in the real world it can work in the RTL simulation. This kind of simulation is usually done since the results will be identical to the actual hardware. It is however not very practical for software development since these two types of simulations will be too slow for iterative development. What is often done is to make RTL compatible models that are functionally equivalent but that can be simulated quicker.

One example of a system used to describe high level IP blocks together is SystemC. SystemC [27] is strictly speaking a set of C++ classes that provides a discrete event simulation that can be used to simulate a digital design but it is often seen as a language on its own. SystemC is nowadays often used as a sort of glue for linking many IP blocks together in a simulation. Where the glue is needed to create a workable system. SystemC ships in multiple variants as shown by Popovici [48] but most of those solutions are based on the reference implementation of the SystemC runtime.

To facilitate creating higher level models than just using RTL simulations, with the TLM library for SystemC has been developed [53]. SystemC in conjunction with this library provides a framework in which different components of different vendors can be coupled together by using standardized interfaces. The latest version of TLM 2.0 has been specifically designed to link up different

#### 2.2. INTEROPERABILITY

pieces of IP together.

TLM 2.0 allows the user to run the simulation at different levels of detail. TLM 2.0 defines two broad categories of timing detail namely:

- Loosely-timed

- Approximately-timed

Loosely-timed implies that the transactions are un-timed with the access protocols (like bus protocols) modeled with not so much detail. This allows parts of the simulation to run ahead of the general simulation but this time remains bounded. This prevents the simulation from becoming too loose but it also allows the simulation to perform faster. In this timing mode the events do not need to happen in order as long as it does not run too far ahead.

Approximately-timed is defined as a stricter approach but it is not cycle accurate. In an approximately timed simulation the protocols are modeled in more detail. In this timing mode all events are handled in order, meaning that the simulation occurs sequentially.

The default SystemC discrete event kernel can only run on a single core but there has been some research on making a more concurrent variant of SystemC in conjunction with TLM 2.0. An example of this is SystemC SMP in conjunction with TLM DT (Distributed time) [36]. In such a system the timing is more relaxed compared to loosely-timed but the simulation can run in parallel. This allows the SystemC simulation to take advantage of having a host computer with multiple cores, which in some cases can increase the speed of the simulation at the expense of detail.

#### 2.2.1 TRAP

TRAP (TRansaction level Automatic Processor generator) is a simulator generator designed by Luca Fossati at the Politenico di Milano. It is used for example by ESA to generate a SystemC model for the Leon2/3 processor [16]. The TRAP framework is designed to automatically generate different variants of an instructions set simulator for a specific architecture based on a high level specification written in python with some C++ for the parts of the simulator that need to be customized like interrupt handling.

TRAP only requires some architectural details (like is this architecture big endian, how many bits go into a byte and how many bytes form a word), a declaration of the registers, alias bank declarations (how are the register mapped in memory), a declaration of how interrupts are handled, a description of the pipeline and the Application Binary Interface (ABI). The ABI information is used to allow an OS to be emulated by the simulator to allow things like loading in files.

Currently TRAP can generate instruction set simulators for ARM7 and Leon processors that can operate as a separate ISS or can operate inside of loosely

timed and approximated timed SystemC simulations. Since these simulators use SystemC they can be used to create heterogeneous simulations. By default they can not take advantage of a underlying host parallelism since that requires modification of the SystemC scheduling mechanisms. The framework can at the moment only generate simulators for RISC like processors.

#### 2.3 Conclusion

In terms of multi-core simulators most effort has been focused on simulating homogenous platforms. The area of simulating heterogeneous platforms has been largely left aside. Due to the increasing number of heterogeneous SoC's it could prove useful to integrate simulators together to simulate a whole SoC at a higher level than currently available to allow software to be tested earlier. Also none of the simulators discussed in this section have tried to see what are the effects of changing the simulation accuracy, which might be able to improve the speed of the simulation. And only some of the simulators discussed try to take advantage of the multi-core nature of today's host computers.

## Chapter 3

## **Research** questions

Looking at the related work we can see a number of trends in current research. One trend is that the focus has been on improving on the performance of single core simulators and on simulating homogenous multicore architectures.

The open areas in the field that we want to tackle with Handfish are the following:

- 1. How can a simulator be built with a tunable level of simulation strictness? (Tunable)

- 2. What is required to combine multiple instruction set simulators together to create a simulator of a heterogenous System on Chip? (Heterogeneous)

- 3. How can such a simulator be built such that it takes advantage of the multithreaded capability of the host? (Multithreaded)

These three question summarize the requirements of the framework. In appendix A the precise requirements of the system are formulated. It also specifies some secondary requirements for the framework. In that appendix the reason for each requirement is given and the means how the requirement can be verified.

CHAPTER 3. RESEARCH QUESTIONS

22

### Chapter 4

# Models of multi-core execution

Before we have a look at the architecture of the multi-core simulator we first need to have a look at a more formal model of multi-core execution. We do this by defining a number of concepts based on the execution of a program.

Most computational cores have an instruction set that consists of three types of instructions:

- Control flow instructions

- Instructions with external side effects

- Instructions with internal side effects

Control flow instructions are instructions that control the flow of a program, designating if a program should branch or repeat a number of instructions. Examples in high level programming languages are the 'if' and 'while' statements and in low level instructions go and branch. The handling of interrupts can also be considered a type of control flow instruction, except that in that case the control flow is changed from the outside. Interrupts outside of timed interrupts are also unpredictable since they can happen at any time while the processor is executing.

Instructions with external side effects change the computing environment outside the processor. Examples of such operations are loads  $^1$  and stores to memory or in older processors I/O instructions.

Instructions with internal side effects change the state of the processor but do not change the state of the surrounding computing environment. Examples of these kinds of instructions are mathematical operations on registers.

<sup>&</sup>lt;sup>1</sup>Technically load instructions do not change but environment but to execute a load, the environment has to be queried. This may or may not have side effects.

There are processors that mix and merge these types of instructions into a single instruction (namely CISC like processors) for the rest of this chapter we will not consider these types instructions since they are rarely used nowadays and these instructions can be rewritten into combinations of smaller instructions that would result in equivalent behavior. An example would be instruction that increments a value and writes it to memory. This can be rewritten as an add instruction followed by a store instruction.

When we have multiple processing elements there will be multiple streams of instructions. As we have previously seen these instructions can have side effects that are visible to the outside or not. For example a stream of stores is visible while continually incrementing an internal register will have no side effects from the outside.

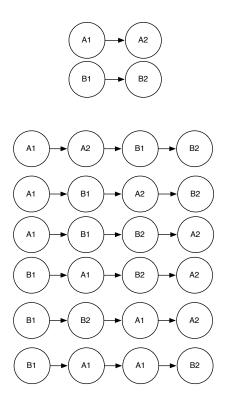

Take for example two instruction streams consisting of two instructions. If we execute these concurrently there are six possible inter-leavings as seen in figure 4.1. This abstraction is valid because with multiple execution cores, the side effects of a computation can only be observed in a shared resource. This is usually a shared memory and due to all accesses being atomic, all operations appear serialized <sup>2</sup>.

Figure 4.1: Possible inter-leavings of two instruction streams

Each of these traces is a valid execution but each can result in a different

24

$<sup>^{2}</sup>$ This assumes normal DRAM instead of specialized dual-ported DRAM like that used in graphic adapters and even those do not allow two simultaneous writes.

output. The effect is amplified on larger programs. It is also possible for two different runs of a program to produce the same output, these traces are called output equivalent. Meaning that from the perspective of an outside observer the two executions are identical.

The discussion is further complicated by the fact that instruction can have side effects on which instructions in the future depend. Data dependencies between instruction streams are especially complicated when knowledge from multiple instructions streams is required to analyze them. For example a read instruction might expect that another instruction from another core has written a value out. If this write did not happen the following control flow might change and the program might get into a state the developer did not anticipate.

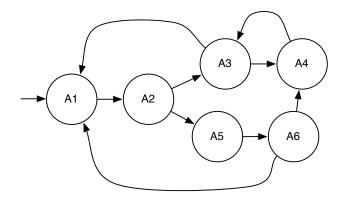

Introducing control flow makes the discussion more complicated because the instruction flow can branch and jump. An example can be seen in figure 4.2 This type of graph is called a control flow diagram since it shows the control flow of a program. A control flow graph does not show an execution but it shows all the branches that a program can take. Thus is can also show dead code paths since it is a direct transformation of the program code<sup>3</sup>.

Figure 4.2: Example of a control flow graph with branches and loops

Control flow graphs as we have currently described them do not describe an execution of a program, concurrent or not. If we take a program that runs concurrently over two cores we will have two control flow graphs that execute at the same time. If we assume the worst case scenario the resulting graph would include nodes that are combinations of every possible combination between the nodes of the two control flow graphs and the resulting edges that connect these nodes to each other. This leads to very large graphs since the number of nodes is the multiplication of all the nodes and the number of edges is even more. Any run of the concurrent application can be seen as a walk through this graph where an edge can be passed multiple times.

This does mean that the graph contains nodes and edges that never occur during execution in hardware and some of these nodes and edges are only traversed during execution in a non strict simulator. Later on in this chapter we

<sup>&</sup>lt;sup>3</sup>This could be the binary image or the assembly source code.

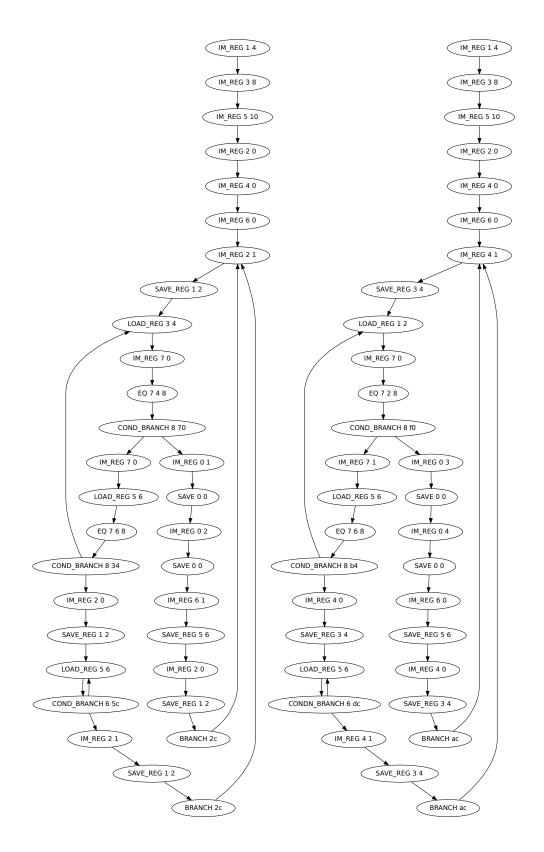

will formalize these graphs. The number of taken states is limited by such things as data dependencies, conditional branching and start up effects to name but a few. For example a program writes out a fixed sequence of values to memory will have less interactions in a given run than a program that loops continuously. Shared memory synchronization algorithms are a good example of such programs since they will forbid interactions of critical sections. This removes a large number of nodes and edges from the graph. In appendix D the control flow diagram of a implementation of Dekker's algorithm on the Simplium<sup>4</sup> architecture can be found. It shows that the control flow is more or less the same for both processes, save for a slightly different conditional in the branches. It is unfortunately not possible to generate a sensible control flow graph of all the possible interleaved states since this graph would become to large to display and generating such a graph is non trivial as is shown by model checkers like spin [26] and java pathfinder [31].

## 4.1 Properties of trace graphs

In our analysis we use trace graphs. A trace graph is a graph generated from the simultaneous trace of a multi-core simulator and is conceptually similar to a state space but it is not the same. We will explain the differences in depth after we have described the trace graphs.

Trace graphs are created from the simultaneous memory access traces. Since the simulators have to fetch their instruction memory this can be used as a indication what the programs are executing<sup>5</sup> at a point in time.

A trace graph consists of nodes and edges. Formally G = (N, E), where G represents the graph and N represents the nodes and E represents the edges in the graph. Each node in the graph is consists of a tuple that describes the current executing instruction of each process at that point in the execution. So when one process fetches another instruction this leads to a different node. An edge represents that there was a transition from one node to another, implying that one core is executing a different instruction at that point. The edge can optionally contain a number that represents how many times this transition was made during the trace. We call an graph without such numbers on the edges a structural trace graph and with these numbers an ordinary trace graph.

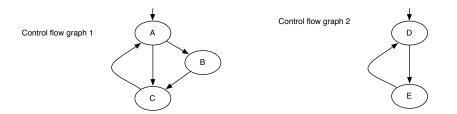

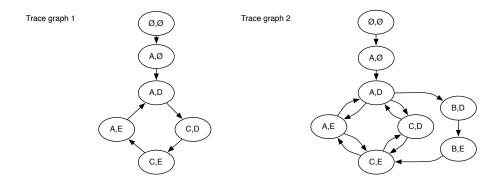

To illustrate such a graph we have included two structural trace graphs of two cores executing. We also include the control flow diagrams to show the functioning of each program separately.

In figure 4.3 we see the two control flow graphs. Control flow graph 1 contains a choice at instruction A while control flow graph 2 does not contain any data dependent logic. In figure 4.4 we see the two possible trace graphs for a concurrent execution of the two programs.

$<sup>^4\</sup>mathrm{The}$  Simplium architecture is described in appendix C and is used extensively in the following chapters.

$<sup>{}^{5}</sup>$ This assumes an architecture without any instruction caches The Simplium architecture is an architecture without any caches.

Figure 4.3: Control flow graphs of two programs

Figure 4.4: Two possible trace graphs

As we can see the trace graphs can be different depending on a number of things, the strictness of the simulation, the length of the simulation and other external factors like host system load.

Structural trace graphs have certain mathematical properties, namely their maximum number of nodes and edges, based on the underlying control flow graphs.

$$|N| = (n_1 + 1) \prod_{P - \{p_1\}} n_p$$

$|E| = 2|N||P|$

In this formula |N| represents the maximum size of the trace graph in terms of nodes and P stands for the set of all processes present in the execution. To include the initial node we increment the first process node count with 1, which represents the starting node of the trace graph.  $n_p$  represents the number of instructions in the control graph of process p. So the maximum size of the trace space is the product of the number of instruction of each process.

|E| represents the number of edges for the whole graph which is equal to the number of nodes times the number of processes in the simulation which is denoted with |P|. This is because in the worst case the next instruction fetched can be any instruction from any process. There are at most 2|P| edges coming from each node because from each node in the graph another process can execute. The number of edges is limited since we can only advance one process at a time because the memory can only be accessed by one core at a time. Since a branch can jump to two location the number of edges is also multiplied by 2 since any process can be executing a branch at any time. Trace graphs also allow self edges, like a branch instruction going back to itself.

The only thing that changes for ordinary trace graph is that the edges contain a traversal count property, but this does not change the number edges nor the number nodes in the graph. This can be used to determine hot code paths in the graph.

There are a number of trace graph types. First there is the maximum trace graph, of which the properties have been described before. This graph does contain combination of nodes and edges that can never be reached. This structural graph can be mechanically generated from the control flow graphs. An interesting subset of this graph is the reachable graph which takes maximum trace graph and then strips of all the nodes that are impossible due to control flow and their dependencies. This is similar to the notion of reachability in Petri Nets where finding out which states are actually reachable is a proven hard problem [32]. With a trace from a run we can create an observed trace graph (both structural and ordinary). This graph can in theory be as big as the reachable graph but this would require a program that would run for a long time and repeats itself in its entirety.

Trace graphs are related to Petri Nets [43] and state spaces but they are not the same. The main difference lie in how they are used, Petri Nets and state spaces are used mainly to determine a priori if an algorithm can have bad states while a trace graph is used to examine the same program under different conditions with the same input. Because trace graphs do not contain information about the state of variables they can be smaller at the cost of making it impossible to do a reversible operation from a trace graph to a trace (since the transformation loses information).

Trace graphs also have the advantage that they feature some compression in the sense that repeated transitions between edges will only increment the number at the edge and not actual size of the graph, since no edges or nodes are added. This makes trace graphs efficient for comparing different runs since when comparing the two different graphs we can compare the structure of the graph and easily determine which parts of the execution are different. This is how they are used in appendix F.

## 4.2 Trace to trace graph transformation

Our definition of a trace is a list of structures which lists an identifier of a core and a disassembled instruction and whereby the order in which these structures are present in the list represents the order of execution of a program. In practice a trace can contain more information but this the minimum we need to create an observed trace graph.

The algorithm described in algorithm 1 shows how a trace graph can be created from a trace.

```

oldNode = array[|P|]

newNode = array[|P|]

for all traceLine \in trace do

newNode[traceLine.id] \leftarrow traceLine.content

if containsNode(graph, newNode) then

addNode(graph, newNode)

end if

if containsEdge(graph, oldNode, newNode) then

incrementEdgeCount(graph, oldNode, newNode)

else

addEdge(graph, oldNode, newNode)

end if

oldNode \leftarrow newNode

end for

```

return G Algorithm 1: Trace graph from a given trace

The function *addNode* adds a node to the graph and the function *addEdge* adds an edge to the graph. The function *incrementEdgeCount* increments the edge count if the node already exists.

The algorithm described in algorithm works as follows. Before starting the algorithm creates two arrays with as their size the number of processes. These are called *oldNode* and *newNode* and represent the node being created and the previously created node while passing through the trace. When passing through the trace we create a new node for every new combination of disassembled instructions per process we encounter. If the edge that connects *oldNode* and *newNode* has not yet been added to the graph we add this edge. If it has already been added, we increment the count of this edge.

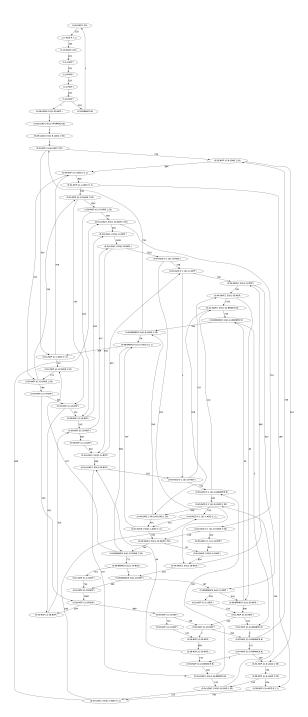

In appendix E we show an observed trace graph of the 'example' program that is discussed in chapter 6 and that graph is generated with the algorithm described in algorithm 1.

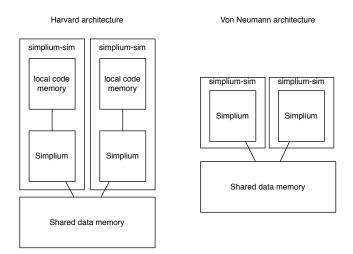

This technique has one disadvantage to create a trace graph in this fashion we need to access to simultaneous code fetches from the sub simulators, which limits this technique to certain architectures. This technique is mainly suitable for Von Neumann uniform memory architectures and would be unsuited for NUMA and Harvard architecture machines because it depends on viewing the whole system state in a single point.

## 4.3 Conclusion

In this chapter we looked at the properties of trace graphs. In the next chapter we will discuss the architecture of Handfish the proposed simulator framework based on some of the ideas presented in this chapter.

## Chapter 5

# Architecture and implementation

In the previous chapters we looked at what is currently available in terms of simulators, what are the requirements for a heterogenous multi-core on multi-core simulator and a theoretical model behind multi-core execution. In this chapter these are combined into a basic design of a simulation system composed of the simulation framework called Handfish and several off-the-shelf instruction set simulators.

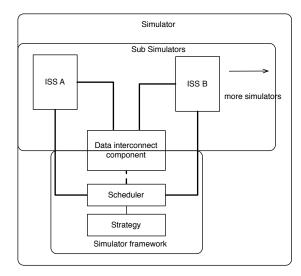

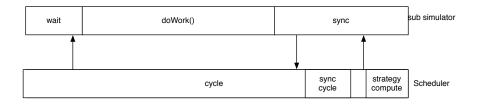

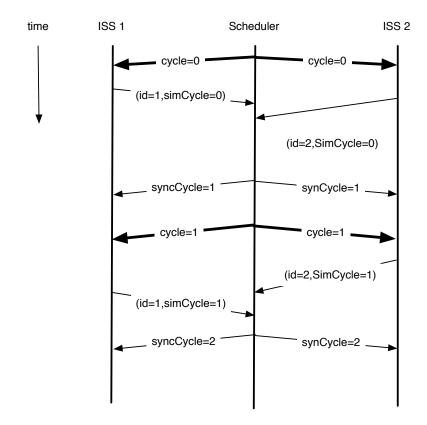

The goal of this project is to create a software system that can simulate a heterogenous or homogenous multi-core system with the help of multiple off-the-shelf instruction set simulators. These are joined together to create a simulator of the whole system in such a way that the underlying multithreading capability of the host system is used. A sub-simulator can be an instruction set simulator or a device simulator. The "glue" to tie these simulators together is called the simulation framework. This includes mechanisms for the sub-simulators to communicate data amongst themselves and for them to remain synchronized with each other. In the text the resulting simulator is also sometimes called the sub-simulator are called sub simulations. In figure 5.1 the general architecture is shown together with the concepts. The way the simulator is split up in components resembles how it is done in GEMS [35], in the sense that the processing and the storage are kept in separate subsystems.

The simulation framework itself consists of the data interconnect component, scheduler and strategy. The data interconnect component is the simulation of a bus but it can also be the simulation of a NoC. Part of the data interconnect can also belong to the sub-simulators since some kinds of simulators can benefit from having a timed interactions, an example would be the simulation of a NoC, so it is partially drawn with the sub-simulators. The scheduler and the strategy together implement the sub-simulator synchronization on the side of the scheduler while the distributed waiting component implements it on the side of the sub-simulators. The data interconnect component is also the most plat-

Figure 5.1: Component overview

form specific part of Handfish. To simulate a platform the memory map of the platform also has to be simulated. This part is handled by data interconnection component. For example is a system has a memory and a frame buffer these devices would be simulated in the shared data interconnection component.

The scheduler interrupts the main loop of the sub-simulators to ensure that they do not run too far ahead from the policy defined by the strategy. The strategy defines the synchronization point for each simulator registered with the scheduler. The scheduler allows multiple strategies to be implemented by the framework without changing the sub-simulators or the scheduler. The possible strategies range from simple strategies like synchronizing every fixed number of cycles to context dependent strategies.

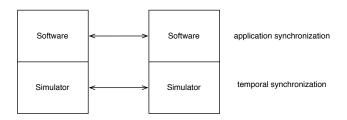

The term synchronization is used often this text and can have slightly different but related meanings, so in the rest of this text we will distinguish between two types of synchronization. Namely the synchronization on the cycle level of the simulators and the synchronization of the software running inside the simulator.

Figure 5.2: Types of synchronization

The first concept that needs clarification is that synchronization happens on multiple levels in a simulated system. This is shown in figure 5.2 Software runs on top of the simulators. We call this application synchronization. The simulators are running on a host with multiple cores, which means that they also need to be synchronized amongst themselves. This type of synchronization is called temporal synchronization and is different in nature. The goal of temporal synchronization is to keep the simulators around the same point in simulated time, while the goal of application synchronization is to prevent the simultaneous access of data which can cause data corruption. In the next chapter we will look at the interplay of these two types of synchronization with an implementation of the design.

#### 5.1 Architectural component breakdown

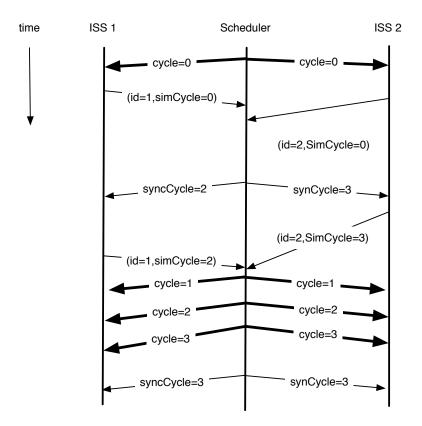

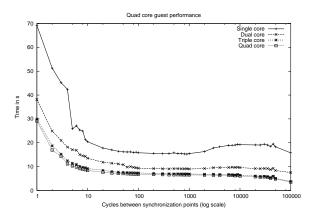

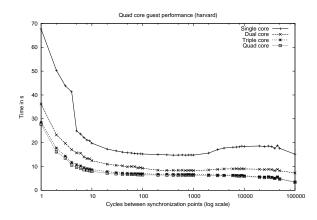

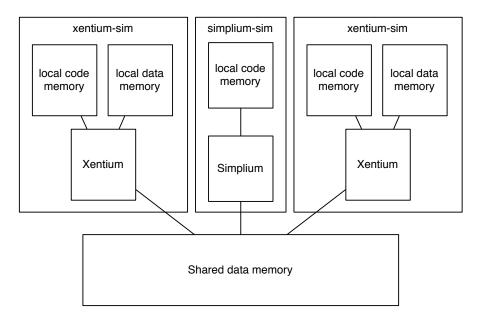

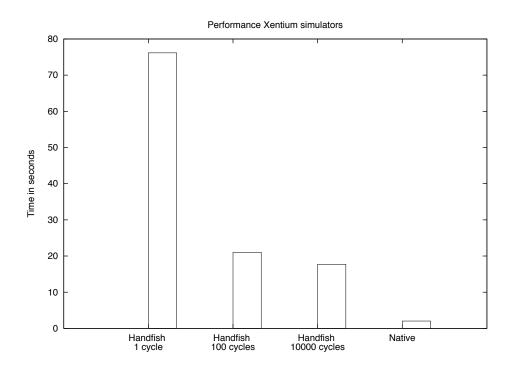

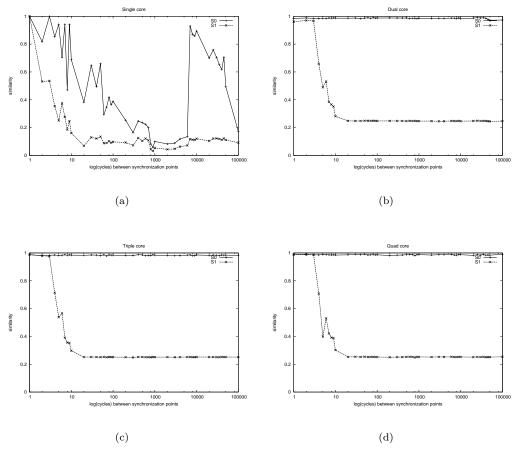

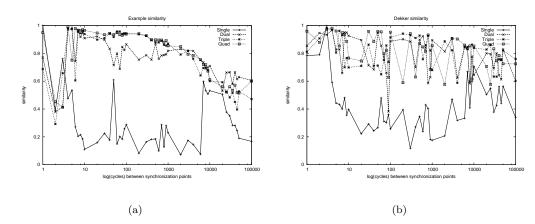

The framework consists of a number of components. The design of the framework is such that major components are isolated in separate processes and they do not share any state. The components only communicate with each other via messages over channels that resemble FIFO's. This is done since one of the goals of Handfish is to make a simulator out of off the shelf simulators. Because of this the number of modifications to the sub-simulators have to be kept limited, it is best to treat them as processes that communicate with each other via messages instead of having direct access to the state of each sub-simulator. This design has been well discussed in theory by Hoare [25] and has more recently been reintroduced by the ZeroMQ framework [24]. We chose this approach to simplify the design and implementation of the system.