## GUARANTEED-THROUGHPUT IMPROVEMENT TECHNIQUES FOR CONNECTIONLESS RING NETWORKS

Guus Kuiper

DEPARTMENT OF ELECTRICAL ENGINEERING, MATHEMATHICS AND COMPUTER SCIENCE COMPUTER ARCHITECTURES FOR EMBEDDED SYSTEMS

EXAMINATION COMMITTEE Prof. dr. ir. M.J.G. Bekooij Prof. dr. ir. G.J.M. Smit Dr. ir. J.F. Broenink B.H.J. Dekens, M.Sc.

**UNIVERSITY OF TWENTE.**

21-10-2013

### Guaranteed-Throughput Improvement Techniques for Connectionless Ring Networks

Master's Thesis by

Guus Kuiper Student number: s0142530

Committee:

Prof. dr. ir. M.J.G. Bekooij (CAES)Prof. dr. ir. G.J.M. Smit (CAES)Dr. ir. J.F. Broenink (RaM)B.H.J. Dekens, M.Sc. (CAES)

Research Group Computer Architecture for Embedded Systems, Department of EEMCS University of Twente, Enschede, The Netherlands October 24, 2013

## Abstract

Increasing the computational power of future System-on-Chips (SoCs) is not possible by increasing the frequency of a processor, because power consumption will become a major issue. Energy efficient systems increase the number of cores to reach higher performance levels to form a multi-core embedded system: a Multi-Processor System-on-Chip (MPSoC). This flexible type of system can be customized for specific applications by changing the software running on it.

At the University of Twente, a prototype MPSoC has been developed specifically for real-time applications, like Software-Defined Radios (SDRs). This class of applications place strict requirements: of a guaranteed minimum bandwidth and a maximum bound on the latency of communication between tasks running on different cores. Communication within the platform is performed over a connectionless Network-on-Chip (NoC), which should allow a small implementation. However, strict guarantees are harder to accomplish in a connectionless network compared to a connection-oriented network.

The original implementation of the ring network can only provide a very low guaranteed bandwidth, because its guarantees are not based on any knowledge of the traffic on the ring. In this work, two types of traffic have been identified on the ring for the software First In, First Out (FIFO) buffers connecting the tasks running on the platform: data and credit traffic. Data traffic requires a high throughput over a short distance and a low latency, whereas credit traffic requires a low throughput over a long distance and is less dependent on latency. A potential issue arises, because the same communication guarantees are offered to both traffic types, which requires an over-allocation of bandwidth, leading to a low Guaranteed Service (GS) bandwidth.

The objective of this research is to define techniques to prevent this over-allocation. Simultaneously, the strengths of a connectionless ring network should be maintained; a small hardware implementation scaling (almost) linear to the number of ring nodes, and a predictable behavior which can be analyzed using data-flow models.

We implemented a separation of these two types of traffic within the connectionless ring network. By doing so, different guarantees can be offered by the ring for data and credit traffic to match their requirements. The separation allows an increase in guaranteed data bandwidth by utilizing knowledge of a mapped task graph and the communication channels between these tasks for a small increase in hardware costs. Furthermore it is shown that an abstraction can be made of the ring network improvement techniques in a compact Synchronous Data Flow (SDF) graph.

An overall increase in GS throughput of the software FIFOs is obtained by using two techniques; one for credit and one for data traffic. The bandwidth of the credit traffic is limited by defining a credit period during which only a single credit may be inserted onto the ring, resembling a Polling Server from (real-time system) literature. This leaves a minimum bound on the available bandwidth for data traffic. Based on the mapping of tasks onto processor tile, data bandwidth is divided on a slot basis and is set in a "slot mask" in every Network Interface (NI). Ring slots can then be re-used by multiple producers to effectively increase the GS throughput.

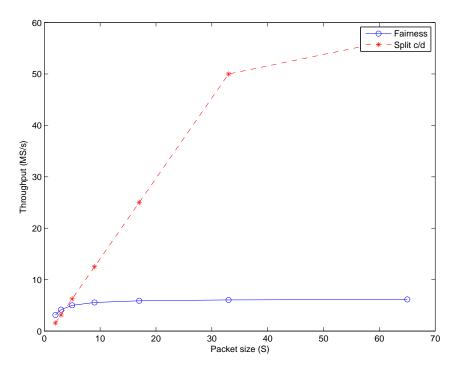

When comparing this solution to the previous fairness protocol, a large increase in GS throughput of a best-case of 6 MS/s to 50 MS/s can be reached when a large FIFO token size is used for the communication between tasks. A small token size effectively means that the data and credit bandwidth will be close to each other, resulting in a low overall throughput when the credit bandwidth is limited. The implemented improvement techniques result in an increase of about 70% in hardware cost, which is less than adding a second dedicated ring specifically for credit traffic. A significant increase in GS throughput is obtained by only a small increase in hardware costs.

## Acknowledgements

First of all I would like to thank Marco, head of my supervising committee, for all the feedback I received, especially late at night when a notification on my phone showed a new e-mail from Marco. I also like the discussions we had about data-flow models and his critical view on my ideas encouraged me to go a step further.

My daily supervisor, Berend, should not be forgotten for providing a basis for my work by designing a predictable ring, of which a paper recently got accepted at a conference. I had a pleasant time with Berend as a roommate for the largest part of my assignment, where I was 'forced' to enjoy his music taste.

Jochem originally developed the Starburst platform and should be credited for creating a platform on which I could easily integrate a ring network design. I could always ask him to help me debug the system when I introduced errors into it.

I would also like to thank Gerald for helping me getting started with this complicated platform and its tooling. He might also have inspired me to start with this assignment during one of our conversation after a floorball practice.

Last but not least I like to thank Nienke, my girlfriend, who spent a lot of time proofreading and thereby correcting most spelling mistakes. Without her help my thesis would have been unreadable.

Guus Kuiper Enschede, October 2013

## Table of Contents

| $\mathbf{A}$  | bstra  | let                                    | i            |

|---------------|--------|----------------------------------------|--------------|

| A             | ckno   | wledgements                            | iii          |

| Ta            | able o | of Contents                            | $\mathbf{v}$ |

| $\mathbf{Li}$ | st of  | Figures                                | vii          |

| $\mathbf{Li}$ | st of  | Tables                                 | ix           |

| A             | crony  | /ms                                    | xi           |

| 1             | Intr   | roduction                              | 1            |

|               | 1.1    | Context                                | 1            |

|               | 1.2    | Embedded Communication Infrastructures | 2            |

|               | 1.3    | Real-time requirements                 | 5            |

|               | 1.4    | Connectionless interconnect            | 7            |

|               | 1.5    | Problem Description                    | 9            |

|               | 1.6    | Contributions                          | 11           |

|               | 1.7    | Thesis Outline                         | 12           |

| <b>2</b>      | Rel    | ated work                              | 13           |

|               | 2.1    | Network-on-Chips                       | 13           |

|               |        | 2.1.1 Ring NoCs                        | 14           |

|               |        | 2.1.2 Guaranteed service NoCs          | 16           |

|               |        | 2.1.3 NoC evaluation $\ldots$          | 17           |

|               |        | 2.1.4 Industry $\ldots$                | 17           |

|               | 2.2    | Accelerator sharing                    | 19           |

|               | 2.3    | Real-time analysis models              | 20           |

|               | 2.4    | Summary                                | 21           |

| 3             | Sta    | rburst platform                        | 23           |

|               | 3.1    | Hardware platform                      | 23           |

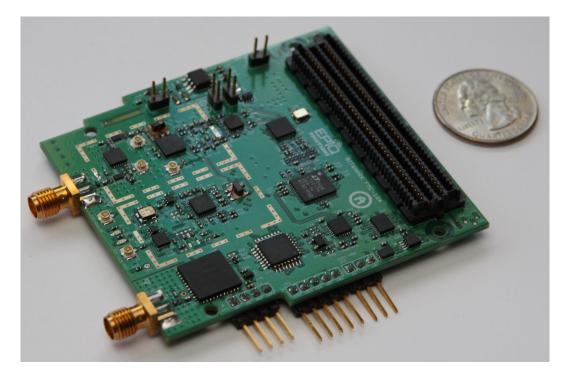

|               |        | 3.1.1 Bitshark                         | 25           |

|               |        | 3.1.2 Multichannel ADC                 | 26           |

|               | 3.2    | Starburst                              | 26           |

|               |        | 3.2.1 Processor tile                   | 27           |

|               |        | 3.2.2 Linux tile                       | 28           |

|               |        | 3.2.3 Arbitration tree                 | 29           |

|               |        | 3.2.4 Nebula ring                      | 29           |

|               |        | 3.2.5 Flow controlled Nebula ring      | 31           |

|               | 3.3    | Software layer                         | 33           |

|               |        | 3.3.1 Helix kernel                     | - 33         |

|              |       | 3.3.2 C-HEAP                      | 33        |  |  |  |

|--------------|-------|-----------------------------------|-----------|--|--|--|

|              |       | 3.3.3 CFIFO                       | 34        |  |  |  |

|              |       |                                   |           |  |  |  |

| 4            | Inte  | er-core communication             | 35        |  |  |  |

|              | 4.1   | Task mapping                      | 35        |  |  |  |

|              | 4.2   | Data flow analysis                | 37        |  |  |  |

|              | 4.3   | FIFO data flow                    | 40        |  |  |  |

|              |       | 4.3.1 Acyclic data flow           | 41        |  |  |  |

|              |       | 4.3.2 Cyclic data flow            | 43        |  |  |  |

|              | 4.4   | Credit burst                      | 44        |  |  |  |

|              | 4.5   | Problem statement                 | 45        |  |  |  |

| 5            | Imp   | Dementation                       | 47        |  |  |  |

|              | 5.1   | Credit                            | 47        |  |  |  |

|              |       | 5.1.1 Limit credit bandwidth      | 48        |  |  |  |

|              |       | 5.1.2 Implementation              | 49        |  |  |  |

|              |       | 5.1.3 Data flow model             | 52        |  |  |  |

|              | 5.2   | Data                              | 53        |  |  |  |

|              | 0     | 5.2.1 Distributing data bandwidth | 53        |  |  |  |

|              |       | 5.2.2 Implementation              | 56        |  |  |  |

|              |       | 5.2.3 Data flow model             | 57        |  |  |  |

|              | 5.3   | Data and credit combined          | 59        |  |  |  |

| 0            | Б     | 1                                 | <u> </u>  |  |  |  |

| 6            |       | luation                           | <b>63</b> |  |  |  |

|              | 6.1   | Hardware costs                    | 63        |  |  |  |

|              | 6.2   | Credit and data split vs Fairness | 66        |  |  |  |

|              | 6.3   | Case study: PAL-demo              | 71        |  |  |  |

| 7            | Con   | clusion and Future Work           | 77        |  |  |  |

|              | 7.1   | Conclusion                        | 77        |  |  |  |

|              | 7.2   | Future Work                       | 81        |  |  |  |

| $\mathbf{A}$ | HSI   | DF graph reduction                | 85        |  |  |  |

| в            | VH    | DL Source Code                    | 89        |  |  |  |

|              | B.1   | Ring link                         | 89        |  |  |  |

|              | B.2   | NI buffer                         | 93        |  |  |  |

| Bi           | bliog | graphy                            | 97        |  |  |  |

|              |       |                                   |           |  |  |  |

## List of Figures

| 1.1  | Example of a (decoupled) bus interconnect                                                                                                        | 3 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 1.2  | Example of a (decoupled) crossbar interconnect                                                                                                   | 4 |

| 1.3  | *                                                                                                                                                | 4 |

| 1.4  | Example of a ring interconnect                                                                                                                   | 5 |

| 1.5  | Communication pattern between 5 task in a connectionless network $\therefore$                                                                    | 8 |

| 1.6  | Tasks shown in Figure 1.5 mapped onto a ring interconnect to show the                                                                            |   |

|      | communication channels and usage of the ring links                                                                                               | 8 |

| 1.7  | Experimental real-time multiprocessor compiler                                                                                                   | 0 |

| 3.1  | Overview of the Xilinx Virtex-6 FPGA ML605 development board [57]. 24                                                                            | 4 |

| 3.2  | The Bitshark FMC-1RX daughter board                                                                                                              | 5 |

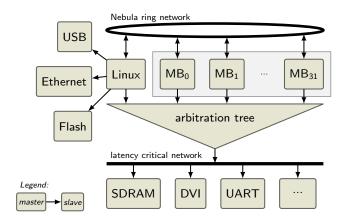

| 3.3  | High level hardware architecture of the Starburst platform                                                                                       | 6 |

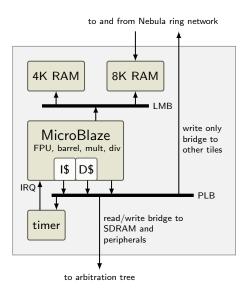

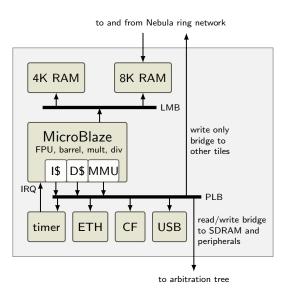

| 3.4  | Processor tile containing a MicroBlaze processor, caches, memories and                                                                           |   |

|      | a timer                                                                                                                                          | 7 |

| 3.5  | Linux tile                                                                                                                                       | 8 |

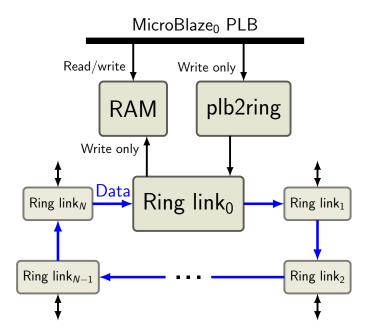

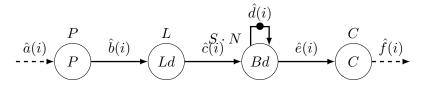

| 3.6  | Block diagram of the Nebula ring connected to the PLB of a MicroBlaze. 30                                                                        |   |

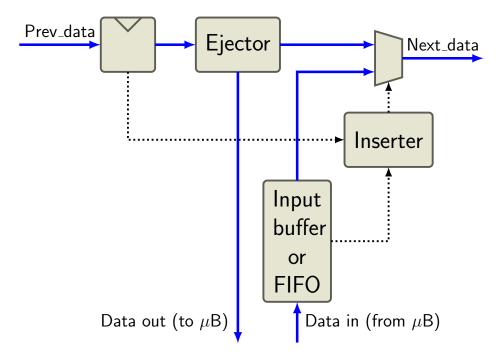

| 3.7  | Schematic overview of a single ring link                                                                                                         | 0 |

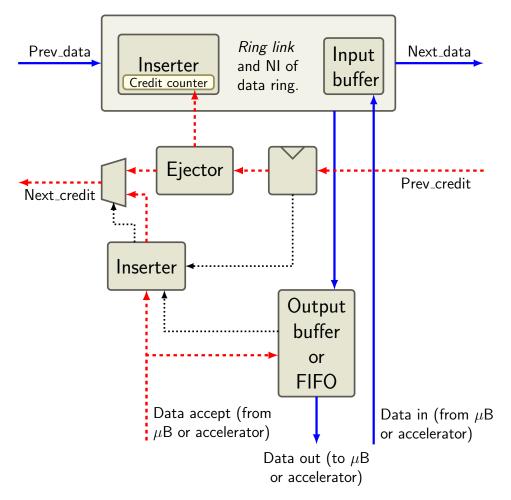

| 3.8  | Schematic overview of a single ring link of the flow controlled version of                                                                       |   |

|      | the Nebula ring                                                                                                                                  |   |

| 3.9  | CFIFO memory and administration structure                                                                                                        | 4 |

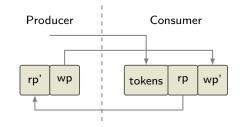

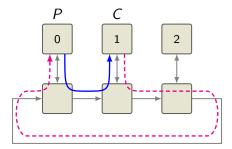

| 4.1  | FIFO ring traffic where the consumer is mapped on processor tile 2 30                                                                            | 6 |

| 4.2  | FIFO ring traffic where the consumer mapped on processor tile 1 30                                                                               | 6 |

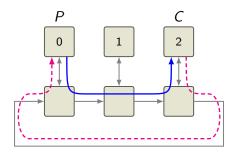

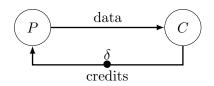

| 4.3  | Task graph of a producer that is connected to a consumer via a FIFO-                                                                             |   |

|      | buffer which is explicitly shown between them                                                                                                    |   |

| 4.4  | Data flow model of the task graph in Figure 4.3                                                                                                  |   |

| 4.5  | SDF graph 39                                                                                                                                     |   |

| 4.6  | Converted to HDSF graph of Figure 4.5                                                                                                            |   |

| 4.7  | Reduced HDSF graph of Figure 4.6                                                                                                                 |   |

| 4.8  | SDF model of the FIFO                                                                                                                            |   |

| 4.9  | Acyclic task graph                                                                                                                               |   |

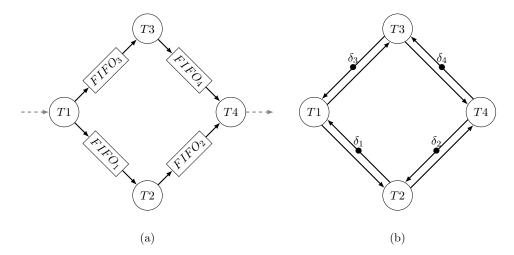

| 4.10 |                                                                                                                                                  | 2 |

| 4.11 | Acyclic task graph containing 2 different paths (a), and the SDF model of it in (b)                                                              | 2 |

| 4.12 | Acyclic task graph containing 2 equal paths (a), and the SDF model of                                                                            | - |

| 1.12 | it in (b) $\ldots \ldots \ldots$ | 3 |

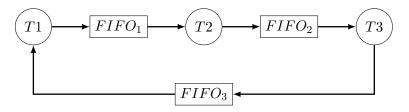

| 4.13 | Cyclic task graph                                                                                                                                |   |

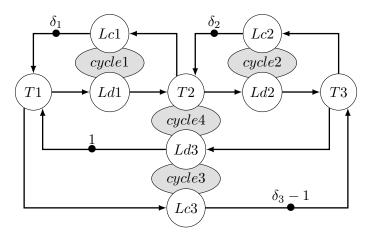

|      | SDF model of task graph of Figure 4.13                                                                                                           |   |

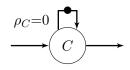

|      | Best-case execution time of the consuming task 'C' of 0 cycles 44                                                                                |   |

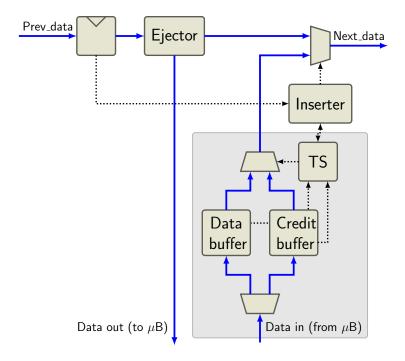

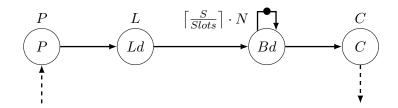

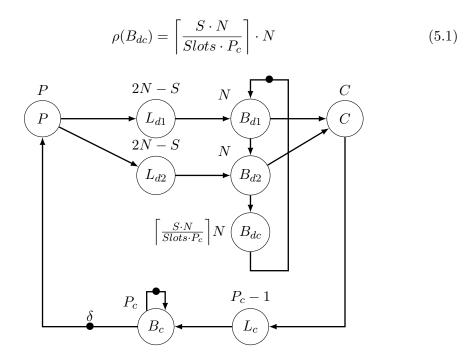

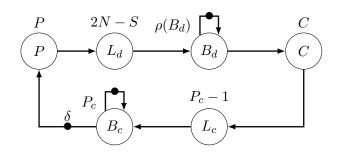

| 5.1  | Overview of the ring architecture where the additional components are shaded                                                                     | 0 |

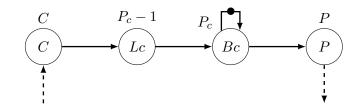

| 5.2 | HSDF graph of credit mechanism                                                                                       | 53 |

|-----|----------------------------------------------------------------------------------------------------------------------|----|

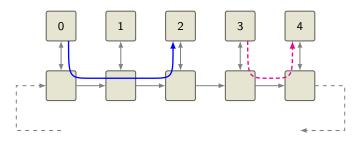

| 5.3 | A ring network onto which two non-overlapping data streams are mapped,                                               |    |

|     | one between node 0 and 2, and one between node 3 and 4                                                               | 54 |

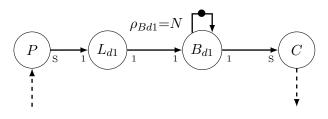

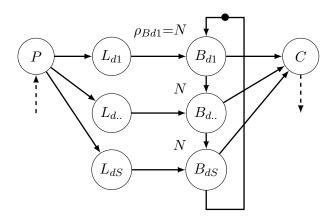

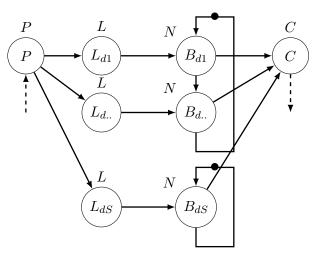

| 5.4 | HSDF graph of a distributed data bandwidth mechanism                                                                 | 58 |

| 5.5 | Reduced HDSF graph of Figure 5.4                                                                                     | 59 |

| 5.6 | HSDF graph of the complete CFIFO communication chain over the Ne-                                                    |    |

|     | bula ring                                                                                                            | 60 |

| 5.7 | Reduced HDSF graph of Figure 5.6                                                                                     | 61 |

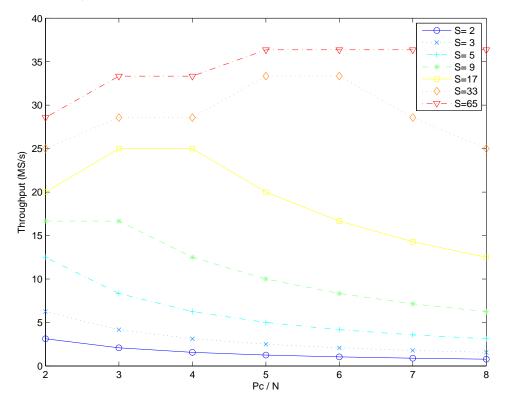

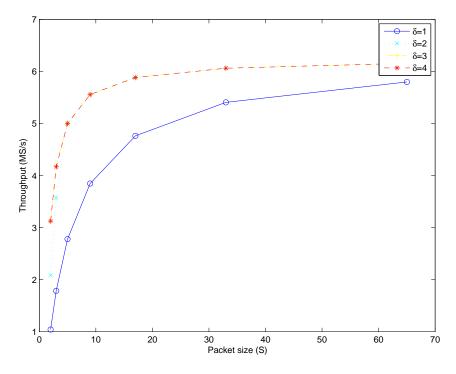

| 6.1 | Throughput dependency on the credit period $(P_c)$ , $\rho(P) = 1$ , $\rho(C) = 1$ ,                                 |    |

|     | $N = 16, slots = 8, \delta = 3$                                                                                      | 67 |

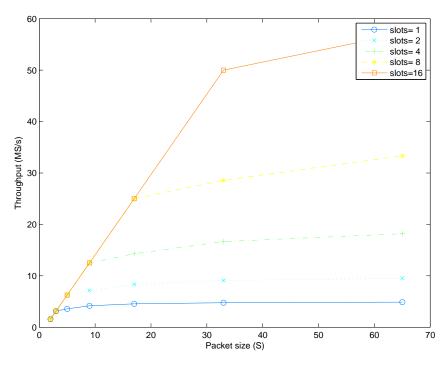

| 6.2 | Throughput effected by the packet size and number of slots; $\rho(P) = 1$ ,                                          |    |

|     | $\rho(C) = 1, N = 16, slots = 16, \delta = 3, P_c = 4 \cdot N \dots \dots \dots \dots \dots$                         | 68 |

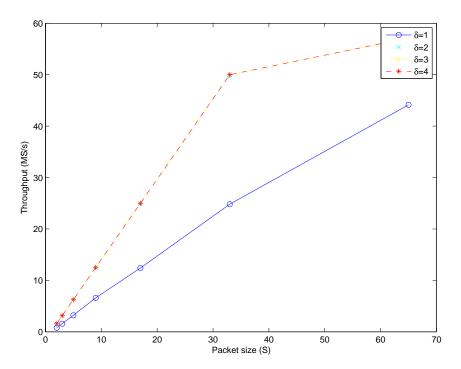

| 6.3 | Best-case throughput with a credit and data split; $\rho(P) = 1$ , $\rho(C) = 1$ ,                                   |    |

|     | $N = 16,  \delta = 3,  slots = 16,  P_c = 4 \cdot N  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ | 69 |

| 6.4 | Best case throughput with fairness; $\rho(P) = 1$ , $\rho(C) = 1$ , $N = 16$                                         | 70 |

| 6.5 | Throughput comparison between fairness and the credit and data split;                                                |    |

|     | $\rho(P) = 1, \ \rho(C) = 1, \ N = 16, \ slots = 16, \ \delta = 3, \ P_c = 4 \cdot N  \dots  \dots$                  | 70 |

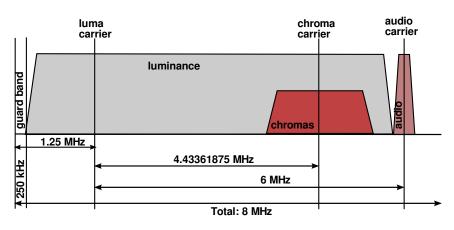

| 6.6 | The spectrum of a PAL signal                                                                                         | 71 |

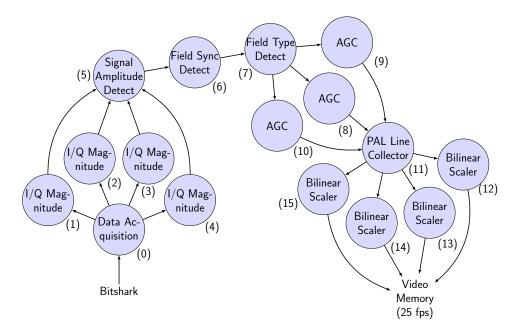

| 6.7 | PAL-demo task graph                                                                                                  | 72 |

| 7.1 | Accelerator ring idea                                                                                                | 83 |

| A.1 | Task graph of a producer-consumer pair with a communication channel                                                  |    |

|     | in between                                                                                                           | 85 |

| A.2 | HSDF model of data traffic on the ring as presented in Figure 4.6, but                                               |    |

|     | with labeled edges                                                                                                   | 85 |

| A.3 | Reduced HSDF graph of the one presented in Figure A.2 with labeled                                                   |    |

|     | edges                                                                                                                | 85 |

## List of Tables

| 3.1                 | Ruleset of a <i>ring link</i> in the Nebula ring                                                                                                         | 31             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| $5.1 \\ 5.2 \\ 5.3$ | Nebula ring address map                                                                                                                                  | 51<br>52<br>57 |

| 6.1                 | Hardware usage of reference components: Starburst MicroBlaze (i.e. all non-Linux MicroBlazes), Linux MicroBlaze and Multi-Port Memory Controller (MPMC). | 64             |

| 6.2                 | Hardware usage of the averaged <i>plb2ring</i> with a FIFO of four places deep.                                                                          | 64             |

| 6.3                 | Hardware usage of the averaged <i>ring link</i>                                                                                                          | 65             |

| 6.4                 | Hardware usage the <i>ring shell</i> for different ring entities                                                                                         | 65             |

| 6.5                 | Total hardware usage of the average ring node                                                                                                            | 66             |

| 6.6                 | Total hardware usage of a 16 core Starburst MPSoC                                                                                                        | 66             |

| 6.7                 | Ring traffic specification for the tasks part of the PAL-demo, for a 10 MS/s input.                                                                      | 73             |

| 6.8                 | Benchmark results of the PAL-demo for different configurations of the                                                                                    |                |

|                     | Nebula ring                                                                                                                                              | 73             |

| 6.9                 | Results of a synthetic benchmark for different configurations of the Ne-                                                                                 |                |

|                     | bula ring.                                                                                                                                               | 74             |

## Acronyms

$\mu B\,$  MicroBlaze.

**ADC** Analog to Digital Converter. **AHB** Advanced High-performance Bus. **AMBA** Advanced Microcontroller Bus Architecture. **APB** Advanced Peripheral Bus. **ASIC** Application-Specific Integrated Circuit. **AXI** Advanced eXtensible Interface. **BE** Best Effort. **BRAM** Block RAM, dedicated RAM in Virtex-6. CPU Central Processing Unit. **DAC** Digital to Analog Converter. **DDR3** Double Data Rate type 3 SDRAM. **DMA-C** Direct Memory Access-Controller. **DSP** Digital Signal Processor. DSP48E1 Digital Signal Processing element, special Virtex-6 slice. **DVB-T** Digital Video Broadcasting — Terrestrial. FIFO First In, First Out. FMC FPGA Mezzanine Connectors. FPGA Field-Programmable Gate-Array. FSL Fast Simplex Link Bus, uni-directional point-to-point hardware FIFO communication link.

GALS Globally Asynchronous Locally Synchronous.

GPS Global Positioning System.

**GS** Guaranteed Service.

**HD** High Definition.

${\bf HSDF}\,$  Homogeneous Synchronous Data Flow.

**ITRS** International Technology Roadmap for Semiconductors.

${\bf KPN}\,$  Kahn Process Network.

LAN Local Area Network.LMB Local Memory Bus.LUT Look-Up Table.LUTRAM LUT RAM, LUTs used as RAM.

MCM Maximum Cycle Mean.

### ACRONYMS

MMU Memory Management Unit.MPMC Multi-Port Memory Controller.MPSoC Multi-Processor System-on-Chip.

**NI** Network Interface. **NoC** Network-on-Chip.

PAL Phase Alternating Line.PLB Processor Local Bus.

**RAM** Random Access Memory.**RF** Radio Frequency.

SDF Synchronous Data Flow.SDR Software-Defined Radio.SoC System-on-Chip.SPM Scratchpad Memory.

**TDM** Time Division Multiplexing.

**VHDL** VHSIC Hardware Description Language.

# CHAPTER

## Introduction

### 1.1 Context

Traditionally the computational power demands would increase every year, just like you would expect the number of transistors to double approximately every two years as Moore's law dictates. The International Technology Roadmap for Semiconductors (ITRS) expects, for the near future, there will come no end to this growth of processing power [27]. In the year 2026, the system processing performance metric will have grown by a factor of 1000 as compared to 2009.

The need for such an increase becomes obvious when looking at consumer electronics; take for example the color television market. Starting (in Europe) with the Phase Alternating Line (PAL) standard, the image quality keeps increasing and evolved towards High Definition (HD) video (720p or 1080p) to reach a major improvement in quality. Bandwidth requirements double when using 3-dimensional technology to supply a different image to both eyes. Improvements do not end there, as more processing power becomes available; standards that use even more pixels are introduced like 4K Ultra HD (four time more pixels than 1080p HDD). More advanced technologies are on its way, such as 8K Ultra HD, again increase the number of pixels by four times<sup>1</sup>. Processing becomes even more demanding when such videos need to be analyzed for surveillance purposes, preferably in real-time. Thus, an increase in computational power can always be used by applications to improve the user experience.

The increase in processing power could in the past be accomplished by scaling in frequency. This was sufficient until the thermal limits were reached quickly, as power requirements scaled faster than frequency. The only way forward was to increase the number of processing cores, despite of the (even currently unsolved) problem of how to program such multi-core designs. This trend of adding more cores will continue according to the predictions of the ITRS; "The number of cores increases by a factor of 1.4 per year" [27].

Again looking at video context, recent developments in video codecs have picked up this trend towards multi-core systems. The current most commonly used compression standard H.264 (Advanced Video Coding) is hardly supporting parallel

<sup>&</sup>lt;sup>1</sup>Recently, this technology has been premiered. On the 17th of may Sky-Skan Inc. in association with The Franklin showed "Institute To Space And Back"; an 8K x 8K, 60FPS, 3D film running approximately 25 minutes [3]

### CHAPTER 1. INTRODUCTION

processing of the same operation within a single frame. The proposed successor, H.265 (also called "High Efficiency Video Coding"), however, has clever tricks that make it (more) suitable to run on multi-core systems. "The option to partition a picture into rectangular regions called tiles has been specified. (...) Tiles are independently decodable regions of a picture that are encoded with some shared header information" [46]. These tiles can inherently be processed on different cores, allowing decoders to be better mapped to future many-core hardware architectures.

These applications need to be integrated into embedded systems, like mobile phones, to -for example- record and encode HD video. Already, most functionality is integrated into a single chip: a SoC. The next logic step is to move towards multiple processors to fulfill the unique requirements of embedded applications; so the Multi-Processor System-on-Chip (MPSoC) [52] was introduced. These MPSoCs are ideal platforms for semiconductor manufacturers, because they can be specialized into a number of products, mainly by customizing the software that runs on them.

Two types of MPSoCs exist, each with their own (dis)advantages: homogeneous and heterogeneous MPSoCs. Homogeneous ones are easier to program and more flexible, whereas heterogeneous MPSoCs contain specific hardware accelerators which improve power efficiency for certain applications and are also used to meet the performance of more demanding applications, like processing modern wireless standards. The goal of previous work was to integrate accelerators into a homogeneous MPSoC [26] to create a heterogeneous MPSoC, which is capable of accelerating DSP algorithms like PAL video to perform at commercial speeds, while retaining the same system clock speed.

Moving from single to multiple processors in a system imposes some new architectural challenges. It is not possible in such a system to obtain a low main memory latency in combination with many processors using the same shared memory. All kinds of issues relating to caches (coherency) [40], synchronization (locking) [38] and communication (inter-core or core-to memory) [39] arise in MPSoCs. A research platform is developed at the University of Twente to address these kinds of topics.

Communication is crucial for the overall performance of an MPSoC and will be further introduced in Section 1.2. The real-time requirements of embedded applications running on SoC / MPSoCs will be the topic of Section 1.3. A special feature of the research platform, a connectionless interconnect and the (dis)advantages of this connectionless approach are discussed in Section 1.4. After the introductions to (connectionless) embedded communication infrastructures and real-time requirements, the problem statement of this thesis will be described in Section 1.5.

### 1.2 Embedded Communication Infrastructures

Since communication within a SoC is an important aspect of a chips performance, a short history will be presented in this section. In the past, every system used a bus as interconnect, then crossbars followed, and currently research is focusing on Network-on-Chips (NoCs). The reasons for the shift from buses to more advanced architecture will be described here.

When systems only consisted of a single processor and a very few peripherals buses were used to connect them. A bus is a shared interconnect which originated from outside chips. Only one entity, a master, can transport data at a time. When multiple masters are present, they need to be granted access to the bus from a central arbiter. An example of such a bus is given in Figure 1.1, where a decoupled view is given, which separates the architecture of the interconnect (the gray box in the middle) from the masters and slaves. A widely used bus architecture in the industry is the ARM Advanced Microcontroller Bus Architecture (AMBA), consisting of a high speed processor bus, the Advanced High-performance Bus (AHB), and a low speed peripheral bus, the Advanced Peripheral Bus (APB), that can be accessed from the AHB through a bridge.

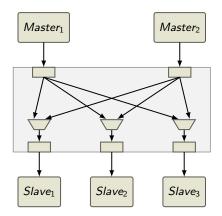

Figure 1.1: Example of a (decoupled) bus interconnect

A bus favors one-to-one communication where one master is active at the time, as the arbitration otherwise stalls bus access requests. Power efficiency is not very high as a master must drive the total length of a bus to be able to reach all peripherals. When moving towards multiprocessor design the bandwidth of a bus is quickly saturated. The advantages of a bus are that it is easy to implement and latencies to peripherals are uniform [8].

Unlike in a bus architecture, where one master broadcasts messages over the interconnect, a crossbar is designed to transmit multiple messages simultaneously. A crossbar, like the ARM Advanced eXtensible Interface (AXI), can connect each of its inputs to any of the outputs. This is implemented as a grid of wires where the inputs cross the outputs and a connection is made by shorting a crosspoint. As can be seen in Figure 1.2, arbitration in a crossbar is only required when multiple masters address the same slave, which has a latency advantage compared to buses. Because multiple inputs are present, this design also scaled better with the number of masters. The scaling, however, comes at a high price penalty, because it results in a large die area.

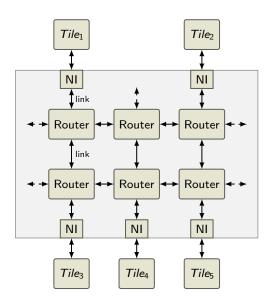

As the trends are to include more and more processing cores inside a SoC, there is a need for an infrastructure that scales well, is power efficient and supports communication between all these cores. A whole network should be integrated into a chip, an NoC. These NoCs consist of Network Interfaces (NIs), routers and links, as can be seen in Figure 1.3. Links are the physical connections (in the form of wires) between routers. The routers forward data from an input to one of their outputs. They contain a crossbar, and also a buffer that is at least the size of a message that can be received during one clock cycle.

The architecture of a NoC is characterized by three attributes: the topology, routing

Figure 1.2: Example of a (decoupled) crossbar interconnect

Figure 1.3: Example of a NoC

algorithm and type of flow control [53]. The topology of a NoC describes how routers are connected to each other and it determines how many (in/output) links a router has, which has a direct influence on how messages can be transported across the network; a part of the routing algorithm. The routing algorithm must ensures a path is formed from source to destination and each data producer receives a share of the total network bandwidth.

The last characteristic, the flow control, specifies when messages are transported between routers. Two types of flow control exist: circuit and packet switched. The main difference between them is the size of the buffers that are required in the routers. A circuit switched network first establishes an end-to-end path from source to destination before data is inserted into the network, which requires only small buffers. As a consequence, those links cannot be used in other paths until the path is deallocated. The latency for such an approach is thus relatively high, because the path needs to be set-up and overlapping paths need to be deallocated first. In packet switched networks, routers can store data for multiple cycles. Flow control is then based on the number of free places in the buffer of the next router along the path of a packet. Reducing latency comes at the price of a much larger hardware

implementation caused by the need for large buffers.

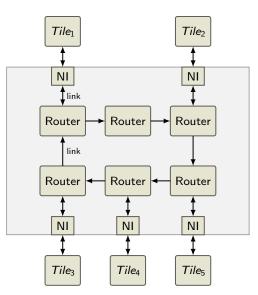

Figure 1.4: Example of a ring interconnect

A special NoC case that deserves additional attention, is a ring topology. A (unidirectional) ring only has a single in- and output, next to the interface with a processing tile. The routing algorithm used in a ring is trivial, since data can only be forwarded in one direction. As a consequence, no large crossbars are required and a minimal amount of buffers is needed (only to store data only for 1 cycle to meet timing constraints of the design). The last NoC characteristic, flow control, is easy to implement at the interface by means of a Time Division Multiplexing (TDM) schedule and using processing tiles that always accept incoming data. It is therefore a very simple and small interconnect.

A lot of research has been performed on all of these three characteristics; topology, routing algorithm and type of flow control. Some implementations, relevant to this thesis, will be discussed in the related work (Section 2.1). Next, the real-time requirements of embedded applications running on processors with such interconnects are covered.

### **1.3** Real-time requirements

Given the above described context, the type of applications that is targeted is introduced in this section. This type has specific requirements, and services that should be provided by the system it runs on. Then, it is discussed how such a system can be analyzed. It finishes with the consequences and requirements for NoCs that where part of the previous section.

Two classes of processing application can be distinguished: data processing dominated, and control dominated [8]. Many signal processing tasks are part of the data processing class, which is characterized as a sequence of operations that are performed on a stream of data with little to no data reuse. Processing can be performed in parallel, requires high throughput and performance, and favors designs with many processing elements. The other class (control dominated applications)

### CHAPTER 1. INTRODUCTION

does have a high data reuse and contains a large amount of states. Examples are (de)compression algorithms, or code with many conditional branches. These tasks are difficult to perform in parallel. A clear separation between the two classes is not always possible. Take for example the H.264 video compression standard. It consists of filtering steps that are clearly data processing tasks, whereas the compression belongs to the control dominated class.

The system which is part of this thesis focuses on signal processing tasks. The input of data originate from an Analog to Digital Converter (ADC) and enters the system at a fixed (sample) rate. At the output of the system a Digital to Analog Converter (DAC) or another digital peripheral is present that requires data to be received at a fixed rate. Constraints are put on the processing chain between the inand output to ensure a finite number of buffers is sufficient, without the chance of losing data, and to provide a correct output. This type of applications fall into the data processing dominated class and will be referred to as "streaming applications" throughout the thesis.

These constraints on the processing chain fall in the category of real-time constraints. The correct behavior of the real-time systems that have to satisfy these constraints, not only depends on the value of the computation, but also on the time at which the results are produced [12]. In the classical view on single-core real-time systems tasks are characterized by a deadline, which is the maximum time in which a task must be completed. Based on the consequences of a real-time task missing a deadline, three task categories can be distinguished. The first one are hard real-time tasks that may have catastrophic consequences when a deadline is exceeded. Firm tasks produce useless results after their deadline; however, this does not damage the realtime system. Finally, for soft tasks, exceeding a deadline causes a performance degradation, but they can still produce some useful results after their deadline.

In a real-time system, software and hardware need to be co-designed to create a overall predictable system. The new view on multi-core real-time systems is not based on deadlines, but on creating a predictable system which should provide guarantees about a maximum latency and a minimum throughput, even under worst-case conditions. Moreover, problems like deadlock and starvation should never occur.

Deadlock is a situation in which two or more users of a shared resource are waiting independently for access to it, which will never occur [12]. It occurs when multiple users have a requirement to use the same two resources in a nested way, but in a different order. At the moment both acquired their first resource at about the same time, deadlock occurs as they cannot acquire their second resource, and thus never finish, locking those resources permanently. The shared resources can, for example, be a number of hardware accelerators. When they are nested, by chaining them together in a signal processing flow, it could cause deadlock to be introduced. It has been shown that deadlock can also be introduced in a deadlock free NoC, by the interaction between a NoC and connected components [22].

Another situation which should be prevented is starvation. It is quite similar to deadlock in a sense that some users never obtain access to a resource and thus do not progress. The difference lies in the fact that other users can get access to this resource. Inside a NoC, starvation can happen when a user is saturating links in the network, preventing others to send or receive data.

By designing a predictable architecture that satisfies these constraints, the system

can be analyzed in such a way that models can be made of it. It is challenging to model execution times of tasks. It is easy to measure upper bounds on the run-time of an operation, however it remains unknown what the actual worst-case execution time is. With these models, it is possible to calculate lower bounds on the performance of the system. The throughput and latency are important characteristics that can be extracted from a model, and can be used to determine if a certain application can run on the platform, or how parameters need to be set in order to guarantee correct behavior. An example of such a parameter is the size of the buffers. By increasing buffer sizes, latencies can be hidden to increase throughput. In the past, many analysis techniques for real-time systems have been developed; an overview of the most important techniques is given as part of the related work (Section 2.3). Moreover, a choice is made there for which one is going to be used throughout this thesis.

When looking at NoCs, a distinction can be made between two type of traffic based on the guarantees that are required for those types [37]. The first one is GS traffic for which the network has to give real-time guarantees: a guaranteed minimum bandwidth and bounded latency. Best Effort (BE) traffic, on the other hand, only requires an average bandwidth instead of a worst-case bandwidth. It is used for nonreal-time applications that are also running on the platform and are used to improve the utilization of the system (of for example hardware accelerators) by exploiting the resources that are left over by the GS traffic. Combining service for both types of traffic in a NoC design however worsens its performance to cost ratio [19]. Therefore this work only focuses on GS traffic for streaming applications.

### **1.4** Connectionless interconnect

The unique feature of the research platform on which this work is performed, is that it has a connectionless interconnect, which is used within an environment that requires the real-time guarantees mentioned in Section 1.3. Usually these kinds of guarantees are only possible in connection-oriented interconnects.

A connection-oriented interconnect is characterized by a connection that needs to be established before data is transmitted. A separate connection needs to be made for every communication channel between all source-destination pairs. The connection ensures a reliable transfer by using flow control and only allowing in-order communication over a fixed route. It allows applications to be analyzed in isolation, where the influence of other applications running on the same platform is bounded. Each channel requires its own buffer to apply flow control; this is quite expensive for large all-to-all communication networks in a MPSoC [39].

Connectionless interconnects on the other hand do not require a separate buffer and setup per connection, making them much more attractive from a hardware point of view. Data units are individually addressed and routed, rather than relying on predetermined connection information. In general this means that no real-time guarantees are possible without a large overhead at an higher layer in the network stack. A connectionless network cannot guarantee no loss of data, error injection, misdelivery, duplication or out-of-order delivery of data.

A high level protocol must be used to support real-time traffic with a guaranteed minimum bandwidth a bounded latency. An example of a protocol that provides

#### CHAPTER 1. INTRODUCTION

additional services to a lower connectionless unreliable layer (IP) is TCP. Realtime services can be obtained by using a software protocol like the one defined in Section 3.3.2, in combination with predictable (hardware) arbiters that allow access to the interconnect. In such an interconnect "...experimental evidence is provided, showing that replacing a connection-oriented NoC by a connectionless one in a distributed shared memory system reduces the hardware costs and improves the performance" [39].

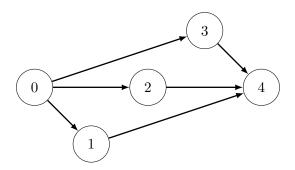

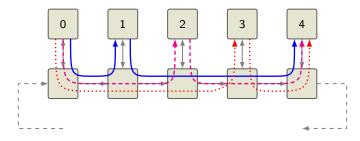

To illustrate the consequences of using a connectionless interconnect, an example is given which should also indicate a disadvantage of not having separate communication channels. Take the task graph shown in Figure 1.5. In this case there are 5 tasks; one producing data (task 0), one receiving data (task 4), and three tasks in the middle that forward data coming from producer to consumer. These tasks are running on processors connected via a unidirectional ring interconnect, where the number of a task also indicates the order in which they are mapped on processors connected to the ring.

Figure 1.5: Communication pattern between one producer task (0), which send data towards three other task (1-3), which each sent their result to a consuming task (4). The guaranteed bandwidth from producer to each of the three intermediate task must be the same in a connectionless network.

Figure 1.6: Tasks shown in Figure 1.5 mapped onto a ring interconnect to show the communication channels and usage of the ring links

With a connection-oriented interconnect, different characteristics can be specified to different communication channels. It is then possible to split the available bandwidth across the three data paths<sup>2</sup> that are visible in the image, which all use the same physical links. These data paths are also visualized by using different line styles in Figure 1.6 where the tasks have been mapped onto processor tiles. In a connectionless interconnect less bandwidth is available as there is no distinction possible between traffic from for example task 0 to 1 and 0 to 3. Bandwidth allocation must be performed for the total outbound traffic of the producer towards the

<sup>&</sup>lt;sup>2</sup>The three paths are:  $(0 \rightarrow 1 \rightarrow 4)$ ,  $(0 \rightarrow 2 \rightarrow 4)$  and  $(0 \rightarrow 3 \rightarrow 4)$

furthest destination (task 3). For example, this means that the bandwidth available at the ring links between task 2 and 3 is not shared by three data streams, but is effectively shared between 5 data streams $(0\rightarrow 1, 0\rightarrow 2, 0\rightarrow 3, 1\rightarrow 4, 2\rightarrow 4)$ , the bandwidth requirement for task 2 is extended to the task with the maximum distance from task 0, which is task 3.

This example shows that in a connectionless interconnect, bandwidth needs to be over allocated when there are multiple data streams using the same links in a ring network. A connectionless interconnect however, is much smaller then a connectionoriented interconnect where a buffer is required per connection.

### 1.5 **Problem Description**

Now the research context is explored in the previous sections, the main problems of this work will be introduced. It starts by giving a brief description of the research platform that was developed at the University of Twente. Then, the main goals of the platform are stated as an additional requirement next to the real-time requirements mentioned in Section 1.3. Problems and improvements that are observed of the platform are stated next, and are used to formulate research questions. The contributions of this work are summarized in Section 1.6. The chapter finishes by providing an outline of the remainder of this thesis in Section 1.7.

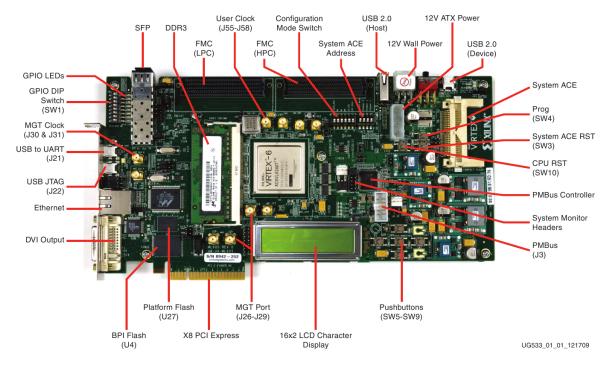

At the University of Twente, a research platform has been developed: Starburst. It is targeted as an experimental next-generation platform for software defined radio purposes and is implemented on a Virtex 6 Field-Programmable Gate-Array (FPGA). An example of an application that is targeted, is a software-based Digital Video Broadcasting — Terrestrial (DVB-T)-decoder; a real-time application with an ADC as periodic source. The goals of the platform are:

- Predictability (firm real-time requirements)

- Composability

- Sufficiently easy programmable

- Low power

- Low hardware costs

Starburst will be described in more details in a chapter that is dedicated to it, Chapter 3. For now, it is sufficient to know that it is a heterogeneous MPSoC, with a distributed shared memory architecture.

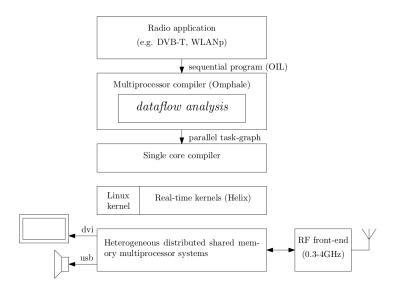

Tools are developed on top of the Starburst platform to assist in programming the multiprocessor environment; OIL and Omphale<sup>3</sup>. How these tools are related is illustrated in Figure 1.7.

Applications are written in a sequential programming language, OIL. It is an abstraction layer that hides the issues, mentioned earlier in the introduction, relating to the concurrency model, the memory model and the underlying hardware layer. The language enables concurrency extraction, handling of memory issues, automated model extraction for optimization and mapping of tasks given temporal constraints.

<sup>&</sup>lt;sup>3</sup>Although Omphale is currently only compatible with an old build of Starburst

### CHAPTER 1. INTRODUCTION

Figure 1.7: Experimental real-time multiprocessor compiler

The sequential program can be compiled with the multiprocessor compiler Omphale [5]. It maps the application to the Starburst platform and analyses if the real-time requirements are met or can be met. This results in a parallel task-graph, which can be used by a regular single core compiler. The tasks can run on one of the processor tiles running a real-time kernel (Helix, see Section 3.3.1) that are described in Section 3.2.1. The last component in the setup of Figure 1.7 is a Linux kernel that is mainly used as an interface to all peripherals.

It is observed that a connectionless interconnect allows a low hardware cost implementation of the Starburst platform. Using the a connection-oriented network Æthereal [19], only 8 soft core MicroBlaze ( $\mu$ B) processors fit into the Virtex-6 FPGA (which not even uses all-to-all communication, but each core is connected to a master core, its two neighbors and the Double Data Rate type 3 SDRAM (DDR3)). A connectionless ring interconnect allows up-to 32  $\mu$ Bs to fit into the same FPGA [39]. When improving the platform it should therefore remain low cost, to have an advantage over connection-oriented interconnects.

The first improvement to the platform is related to the traffic types that are present on the ring NoC. Two distinct types of traffic can be identified on the ring NoC for streaming applications; one type of high throughput short-distance communication, and one low speed over large distances. This property is only true for streaming applications, where consecutive tasks are mapped on processing tiles placed after each other on the unidirectional ring interconnect.

The current communication protocol makes no difference between the two types, such that the same bandwidth and latency guarantees are applicable for both. There, however, is a work-conversing (for a sort of BE traffic) feature build in, which allows bandwidth to be hijacked when certain conditions are satisfied that make sure no negative influence occurs on other data producers. No increase in bandwidth (for GS traffic) is guaranteed and the potential bandwidth increase, decreases with longer communication distances.

Moreover, the communication pattern of streaming data is very regular. Once all processing tasks are mapped onto the platform, the platform is not adjusted to it in any way. By making use of additional task mapping information or by changing the way tasks are mapped onto the platform, the performance of the whole system can potentially increase. The room for improvements is caused by the ring interconnect which provided the same guarantees for all NIs, regardless of the communication requirements of the task(s) running on the processor that is connected to it. It provides a basis to distribute the bandwidth by lowering it for tasks that have little communication to other cores and allocating it to tasks that do require a lot of bandwidth.

Next to these improvement to the performance of the interconnect, another metric is becoming more and more important. Currently, devices containing multiple processors are becoming small, to a scale where they can be worn, like smart watches. This form factor leaves little space for a battery, leading to strict constrains on the power consumption of the SoC inside the device. Identifying major power consuming parts of the Starburst platform and improving them without loss of the predictability of the system is another interesting research topic.

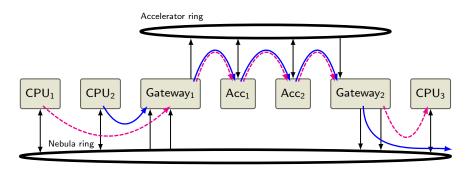

The final observation of the platform is related to the accelerator integration. As is mentioned in the future work of [26], currently hardware accelerators can only predictably be used by one producer. It however, is desirable to share them among multiple producers to improve the utilization of accelerators, reduce hardware costs and allow more computation intensive applications to be run on the heterogeneous MPSoC. There already are some ideas about how this sharing can be implemented, but before that is implemented, it first need to be carefully analyzed and evaluated to see if it doesn't compromise the real-time guarantees.

From these problems the following research questions are formulated:

- What are the benefits of separating different types of ring traffic on an application level (to remain connectionless and low cost) by making use of the mapping of a task graph?

- How can hardware accelerators be shared by multiple producers in a predictable way?

- How can the power of the hardware architecture of Starburst be reduced without sacrificing the predictably of the platform?

### **1.6** Contributions

The main contributions of this work are:

- Implementing a (low cost) separation of different types of traffic on the connectionless ring network, to provide different guarantees which match the requirements of the specific types of ring traffic. The separation is made at an application level in contrast to separation in, for example, the destination in a connection-oriented network (Chapter 5).

- Improving the bandwidth of the data traffic type on the ring by making use of the knowledge of a mapped task graph (Chapter 6).

- Identifying issues related to the estimation of the power consumption of specific parts of the MPSoC.

• A compact data-flow analysis model is obtained as an abstraction of the implemented communication ring.

### 1.7 Thesis Outline

The remainder of this thesis starts by presenting related work in Chapter 2, to place the claimed contribution in the right context. It includes research about NoCs, sharing of accelerators and real-time analysis models. After that the research platform that is used during this work will described in Chapter 3 as it allows a relatively easy prototyping environment for proposed architecture changes.

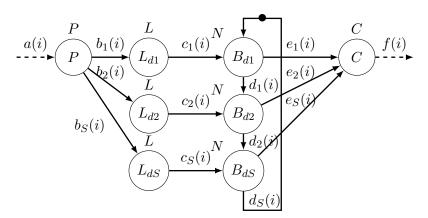

Next, the focus will be on the problems related to inter-core communication. A more detailed view on the context of the problem is presented in Chapter 4. Then solutions are proposed to these problems and a choice, including details about the implementation, for one of them is made in Chapter 5. It also contains an analysis model for the FIFO communication, which is used in Chapter 6 to evaluate the design. The implemented design is also compared to the previous architecture and tested in a case study, a PAL decoder.

After that a brief look is given into how accelerators can be shared within the Starburst platform. It is therefore part of the future work (Section 7.2) which is included in the final chapter, the conclusion (Chapter 7).

# CHAPTER 2

## **Related** work

Now the main topics of this thesis have been introduced in the previous chapter, an overview is given of the research that already has been performed in those research areas. This will show the strengths and weaknesses of the NoC topology, which is used in the Starburst platform and also reveals the current shortcomings, which leaves room for improvements.

We start by addressing the different NoC topologies in Section 2.1, that have gained the attention of many researchers around the world. The differences between these topologies will be explained there. After the introduction to NoCs, the focus will be on different types of ring networks, as a ring is used in the Starburst platform (details about the platform are presented in Chapter 3) and has certain advantages compared to other topologies. An important aspect of a NoC is the real-time guarantees that it provides. NoCs, which provide real-time guarantees are therefore discussed next. The relevance of ring networks is shown in Section 2.1.4 where an overview is given of state-of-the-art chips from the industry, where single or multiple ring networks are used as interconnect between its processing cores.

Within those NoCs, hardware accelerators can be placed to create a heterogeneous MPSoC. Research concerning the integration of accelerators in a NoC is mentioned in Section 2.2.

The last research area that is related to this thesis, is that of real-time analysis models. Section 2.3 gives an overview of different models known from literature. Those models are required to evaluate the performance of a MPSoC consisting of a NoC, and possibly a number of accelerators, and show the limiting factor when running applications on the platform.

Finally, a summary is given in Section 2.4, which indicates the strength of the ring network and from this, it is deduced what the focus of this research should be to make the current architecture even more attractive for integration on certain chips designed for real-time streaming applications.

### 2.1 Network-on-Chips

A lot of research has been performed at NoCs in recent times. These NoCs can be classified using the three characteristics that are mentioned in Section 1.2 (topology, routing algorithm and type of flow control). All will be treated in this section,

### CHAPTER 2. RELATED WORK

however, the topology will be given the most attention as it is the notable part of the NoC that is used within the research platform.

Many different NoC topologies have been proposed in literature, since the one of the ideas of a NoC is to be free in how processing elements are connected. A non exhaustive list of these topologies consists of: mesh, torus, ring, (fat-)tree, butterfly, octagon and irregular interconnections [2]. This is a logical trend, because no optimal topology has been found. "It is worth noting that no single fixed topology categorically outperforms all others" [42].

The most used topology is a mesh and several researchers have suggested that it is the most efficient in terms of latency and power consumption. That suggestion however is application dependent, and targets random traffic. This work on the other hand, looks at a different traffic type by using streaming applications as workload.

Streaming data, which originates from tasks in a task graph without cycles can favor a different topology. When consecutive tasks are mapped on successive processing elements, it forms a sort of chain of tasks. This should map very well to a ring shaped network. A ring can offer a very low latency, in this case, as there are dedicated (short) links from the previous and towards the next task.

A few survey papers have been published that compare many NoCs based on their characteristics [2, 7, 42]. They observed that about 80% of the investigated NoCs uses packet-switched flow control. The most popular routing algorithm is wormhole routing. Most of the routing algorithms are deterministic, while adaptive algorithms have the advantage of being able to recover from or prevent deadlock situation by changing routes. About 60% of all the examined NoCs apply a mesh or torus topology, while only a very few are ring-based topologies.

As the research platform consists of a ring with guaranteed service, focus of the related work will be on NoCs with a ring topology and / or support for GS.

### 2.1.1 Ring NoCs

In the past, ring networks have been very popular and were applied in Local Area Networks (LANs). In these kinds of local networks tokens were passed among users that grant permission to transmit onto the ring. In the current era of NoCs, a few researchers are reintroducing the ring as a viable NoC topology. A ring topology gives good performance for specific traffic types [30, 31]. Research focused on the three NoC characteristics; flow control, routing, topology.

### Topology

A ring already defines a NoC topology, however, it can be subdivided into more advanced designs: uni/bidirectional and hierarchical designs. Bidirectional designs offer a higher bandwidth and lower latency compared to a unidirectional ring as traffic can be scheduled in the direction of the lowest distance to its destination. In hierarchical rings, multiple local rings are connected by mean of global rings to offer better performance for large networks.

It is for example shown that a hierarchical ring network with a single global ring can suffer from congestion at the global ring due to non-ideal traffic loads [10]. A twodimensional "hyper ring", consisting of multiple global rings, is shown to perform better under those loads during simulations. The resource requirements of such a design is still low compared to mesh architectures.

### Flow control

Flow control used to be implemented using a token, or by allocation slots. In such a slotted ring, less bandwidth is wasted [4] as multiple messages can be present on the ring in contrast to a single message in a token ring. Users need to wait until a free slot passes with a least the size of the message they want to send.

Nowadays, flow control is usually implemented by controlling the buffers between the sending and receiving NI. For a ring network, flow control can be implemented by only inserting data when is assured that the target NI can accept the data. Data on the ring can always progress in this way; once data is allowed to enter it, the path and delay to its destination are known. Back-pressure is then applied at higher layer protocol based on the state of the consumer, which is fed back to the data producer. The access policy to the ring manages how the bandwidth of the ring is divided across all its user.

When moving towards more advanced ring topologies, like hierarchical rings, flow control become more important. A single ring can never deadlock as a message continues to move closer to its destination. A situation of livelock, where data continues to move but never reaches is destination, is not possible as the destination can always accept data.

A hierarchical ring, however, requires bridges between the global and local rings. These bridges are very prone to introduce deadlock problems when not carefully designed. The bridge buffer can be full, blocking new messages originating from a source ring, a ejection deadlock. On the other hand, a injection deadlock occurs if the destination ring is already full when data needs to be injected. Flow control algorithms to prevent these two forms of deadlock have been proposed, providing a end-to-end delivery guarantee [16, 17].

### Routing

Routing in a unidirectional non-hierarchical ring NoC is trivial, as messages can only follow a single path to their destination. It gets more interesting when bidirectional routers are used, as then a choice must be made between two paths.

In the bidirectional cast, routing can be based on the shortest path to a destination. This method allows two messages to arrive simultaneously at an NI, one from each direction. A solution is to for example only accept data from the clockwise ring on the even cycles and from the counter-clockwise ring on odd cycles. The producing NI can calculate the appropriate time at which a message needs to be injected into the ring by making use of the known distance to its destination [29].

Routing mechanisms, which are applied to mesh type NoCs are also applied to more advanced hierarchical rings [10]. The routing of packets is determined by: storeand-forward, virtual cut-through or wormhole routing. The methods have been compared on performance (latency and throughput) and hardware costs [33].

### CHAPTER 2. RELATED WORK

### 2.1.2 Guaranteed service NoCs

In this section, NoCs will be discussed that are targeted to offer the real-time requirements mentioned in Section 1.3. As there are hardly any GS ring NoCs, other topologies are also mentioned. The following NoCs are treated: Æthereal, MANGO, NOSTRUM and SoCBUS.

### Æthereal

Æthereal [37] is designed by Philips to separate computation from communication. To accomplish this, GS should be supported by the NoC where resources are reserved for the worst-case behavior. Because this leads to a low utilization for the average traffic, BE support is added to Æthereal.

BE services are provided by packet switching, where the routing information is present in the header of a (self-contained) packet. Real-time traffic is sent across TDM connections over pipelined circuits, a kinds of circuit switching. The routing is performed by specifying the usage of slots inside a table present in all routers. Inside a router, GS traffic is assigned a high priority, whereas BE uses a low priority to maintain guarantees for real-time traffic.

The design of Æthereal is extensively evaluated after 10 years [19]. It was concluded that BE support is expensive. Utilization of a NoC is not relevant, but the performance to cost ratio is; which is worse when BE traffic is included. Later versions of the NoC changed to use virtual-circuits, where packets contain a routing header, to remove the need for large slot tables.

### MANGO

MANGO is a clockless NoC, which is targeted for Globally Asynchronous Locally Synchronous (GALS) SoCs [6]. It supports connectionless BE traffic as well as connection-oriented GS by allocating a sequence of virtual channels across the network. Latency and rate guarantees are not inversely coupled like in TDM-based scheduling schemes, but are managed by a scheme called *Asynchronous Latency Guarantees*.

### NOSTRUM

The NOSTRUM NoC introduces two concepts to provide guaranteed services; *Looped Containers* (LC) and *Temporally Disjoint Networks* (TDN) [32]. TDN are used to separate traffic and making sure packets never collide, and are similar to the principle of slots in Æthereal.

The mesh topology of the NoC already splits the network in two, the *Topology Factor*. A packet can never collide with those of neighboring routers as they can never address the same router. It is only possible with packets that are at a router, which is an even distance away. A second way to separate network is by applying buffers in the router. Each *Buffer Stage* also increases the number of TDN according to the following formula:

$TDN = Topology Factor \times Buffer Stages$

These disjoint networks (Virtual Channels) can be used to provide services to the network.

The idea of LCs is to loop container packets between the source and destination. They can only insert data into an empty container. The LCs thus provide guaranteed access to the network and guarantee bandwidth and latency for all the VCs, which are set up.

### SoCBUS

SoCBUS is a circuit switched NoC designed for hard real-time embedded systems [51], providing hard, short-lived GS connections. Circuit switching in a two-dimensional mesh network allows a low complexity design that avoids deadlock. The concept of Packet Connected Circuit (PCC) is introduced; a packet is switched through the network, locking the circuit as it goes to its final destination. It has shown acceptable performance for local traffic. However, it suffers from random traffic patterns, because the high probability of routes being blocked. As the paths are set up using BE routed packets, SoCBUS can be categorized as soft GS [2].

### 2.1.3 NoC evaluation

A major problem in NoC research, which is indicated in survey papers is that it is hard to make a fair comparison between different NoCs. There are many performance indicators, which cannot be compared. When for example looking at the bandwidth of a NoC, a close relation should be specified at the latency that is experienced. Jitter has been introduced for that purpose [7]. It is defined as the maximum time window wherein the specified bandwidth would always be reached. The same problem is true for the comparison of the cost functions of NoCs. It is hard to make a comparison of the area and power of designs implemented in different technologies (FPGA and ASIC with a range of feature sizes), and layout specific choices concerning the length of / distance between links.

The type of traffic that is used to evaluate the performance of a NoC is also under discussion. Two types of test cases can be distinguished; computation kernels and full applications. The first consists of tasks performing small operations like image processing, filtering or matrix calculations. Unfortunately, this is not a realistic workload for a MPSoC as those tasks represent too fine grained parallelism [42]. Full applications are a better traffic source and include for example video en-/decoding. The best approach would be to run multiple applications on a MPSoC to evaluate if the system is composable and also satisfies the expected usage of NoC-based systems.

Related to this is the issue that there is no common benchmark tool currently, in which NoCs can be evaluated [20]. Although numerous publications target such a tool, a common benchmark tool is not yet available [43].

### 2.1.4 Industry

The industry is also adapting their interconnects to the current trend of adding more and more cores to a SoC. Especially ring networks are becoming popular, which is in contrast to research where meshes are the standard. This might be

### CHAPTER 2. RELATED WORK

caused by different requirements, as the industry is for example more focused on a very high raw bandwidth instead of providing guarantees about maximum latency and minimum throughput.

The semiconductor chip maker with the highest revenue, Intel, is actively involved in interconnect developments. A few of its designs will be treated in this section; the Larrabee GPU and the teraFLOPS research processor, which both led to the release of the many-core Xeon Phi. Its current generation Central Processing Unit (CPU), Haswell, is also covered. The consortium of Sony, IBM and Toshiba developed an interesting interconnect for the Cell microprocessor.

Larrebee is a many-core visual computing architecture that uses multiple x86 CPU cores, supported by a wide vector processor unit. Inter-processor communication is performed over a bi-directional ring network. "When scaling to more than 16 cores, we use multiple short linked rings" [44]. It uses a very wide data-path of 512 bits per direction. Routing decisions are made before a message is injected into the ring. Processor tiles can only accept messages from one direction on even clocks and from the other direction on odd clocks cycles, allowing an efficient router implementation. This results in a high bandwidth interconnect with minimal contention at a very low hardware cost.

The ring is also used for the cache coherency. Each core has access to a subset of the L2-cache, the ring network ensures coherency for shared data. Fixed function logic is also placed around the ring around the ring network and is spread to reduce congestion. Lastly, access from the L2 caches to the memory is provided by the ring. The extra ring latency is typically very small compared to the latency of DRAM access [44].

The more research oriented Intel teraFLOPS makes uses of a different NoC topology to connect its 80 tiles (not consisting of CPUs but floating-point multiply accumulators) [47]. It features a packet switched 2-D mesh NoC designed to run at 4GHz, resulting in a bisection bandwidth of 2 Terabits/s. The NoC uses wormhole routing and flow control that is debit-based, where almost full bit signals are used. The mesh network is not as promising for the industry as researchers believe, since that network is not used in the next many-core architecture Xeon Phi, which makes use of a different network topology.

The Xeon Phi brings many x86 CPU cores to process highly parallel workloads on a single chip [13]. A bidirectional ring is implemented to allow communication to and from all those cores. It consists of a 512-bit wide data ring, a much smaller address ring and the least expensive flow control ring (all for each direction). The last two rings are actually implemented twice as they are small compared to the data ring, but increases its throughput.

Intel introduced a ring network to mainstream CPUs in their Sandy Bridge architecture. Each core has two entry points on the ring to minimize the latency that is experienced when communicating to the System Agent and GPU, which are placed on opposite sites on the chip [21]. Ring links are short enough to run at CPU speed, which covers the latency of traversing multiple hops to a destination on the ring. In Haswell though, the clock is decoupled from the CPU from a power efficiency point of view.

The Cell architecture of Sony, IBM and Toshiba consists of four rings as NoC [30]. Two of these turn in clockwise direction, while the others are rotating counterclockwise. Each data ring is 128-bits wide and is scheduled by a bus arbiter which handles requests. It schedules requests across the two rings with the shortest path to the destination. Each ring supports three concurrent data transfer that don't overlap, providing a total peak bandwidth of 204.8 Gigabytes/s (128 bytes at 1.6 GHz).

### 2.2 Accelerator sharing

Currently, most research concerning hardware accelerators is focused on tightly coupled accelerators that are attached to a processor. These kinds of co-processor(s) cannot be share among different processors, making system consisting of these accelerators very inflexible. One of the possible applications of a heterogeneous MPSoC is a SDR. As an SDR has many uses where multiple streams, potentially of different wireless standards, might need to be processed simultaneously, common Digital Signal Processor (DSP)-blocks (like a Viterbi/Turbo decoder or an FFT) can be shared to reduce SoC area.

Usually accelerator designs are prototyped on, for example, a Xilinx FPGA where a number of MicroBlaze ( $\mu$ B) processors are integrated within the system. These processors contain a Fast Simplex Link Bus, uni-directional point-to-point hardware FIFO communication link (FSL) interface that allows simple addition of custom hardware accelerators to a core.

An example of such a system is presented in [9], however, a few different configurations, regarding the placement of accelerators, are also investigated. Next to the tightly coupled scenario, accelerators are placed between  $\mu$ Bs where one core can write data to it and the other can only read the resulting data (sort of an accelerator ring). The last scenario consists of an accelerator placed on a interconnect, which is shared by four  $\mu$ Bs.

An interesting result is obtained in that work. It is found that better results are obtained when sharing a single accelerator among all processors, rather than connecting a dedicated accelerator to each processor. This can be explained by the fact that the utilization of the accelerator increases when sharing it, without a proportional increase in the load on the share interconnect. Instead processors are waiting until a Synchronization Engine, also connected using an FSL, grants access to the accelerator. As long as the accelerator's utilization does not approaches 100%, processors will become interleaved, increasing the accelerator utilization.

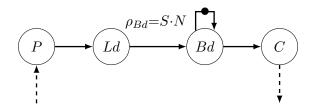

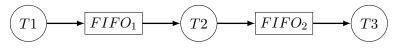

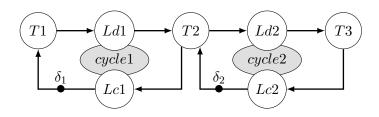

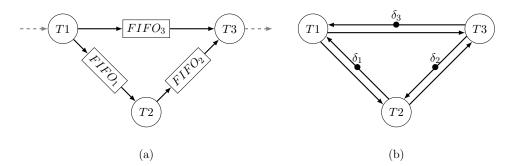

This architecture is not suitable for real-time application. The Synchronization Engine uses locks and barriers, which cannot guarantee a bound on the waiting time of the connected processors. Moreover, interrupts are used to signal the status of the shared accelerator; a troublesome method for real-time systems.