## Connecting Æthereal to the Montium

Master's Thesis by

$\begin{array}{c} {\rm T.M.\ Jongsma}\\ {\rm s0066230} \end{array}$

Committee: prof.dr.ir. G.J.M. Smit dr.ir. A.B.J. Kokkeler J.H. Rutgers M.Sc.

University of Twente, Enschede, The Netherlands Computer Architecture for Embedded Systems Faculty of EEMCS October 27, 2010

## Abstract

## English

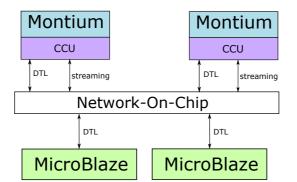

A Communication and Configuration Unit (CCU) is developed to make it possible to connect a Montium Tile Processor (TP) to an Æthereal Network-on-Chip (NoC). The CCU is the interface between the Montium TP and the NoC. A system with MicroBlaze processors connected to Æthereal with a Device Transaction Level (DTL) interface is already available. For better performance for Digital Signal Processing (DSP) the system will be extended with Montium TPs. The Montium TP is a coarse-grained reconfigurable processor. In Æthereal can be chosen from 2 types of Network Interfaces: bus or streaming. The only bus protocol used within this project is DTL. The implemented CCU has two interfaces to the NoC: a streaming interface for the data processing and a Memory-Mapped Input-Output (MMIO) interface for configuration and Direct Memory Access (DMA), which can be streaming or DTL. The choice for streaming or DTL is done at design-time, because it is implemented as an optional adapter which converts DTL to streaming. To be able to test the implemented CCU on an Field Programmable Gate Array (FPGA) evaluation board, a system consisting of 2 MicroBlaze Cores and 2 Montium TPs connected to Æthereal is generated. A small application is successfully executed on a Xilinx ML605 evaluation board, which contains a Virtex-6 FPGA. In this setup the Montium can run on 14.82 MHz. To be able to make a comparison with other CCUs, the design of the CCU, DTL adapter and Montium TP is also synthesized for an Application Specific Integrated Circuit (ASIC). The size of the CCU is  $0.01478 \text{ mm}^2$  without DTL adapter. The DTL adapter is  $0.00149 \text{ mm}^2$ . These results were obtained using a 90 nm low power library and a clock frequency contraint of 400 MHz.

## Nederlands

Een Communication and Configuration Unit (CCU) is ontwikkeld om het mogelijk te maken een Montium Tile Processor (TP) aan een Æthereal Networkon-Chip (NoC) aan te sluiten. Een CCU is de interface tussen de Montium TP en een NoC. Een systeem bestaande uit MicroBlaze processoren verbonden met Æthereal door middel van een Device Transaction Level (DTL) interface is reeds beschikbaar. Voor betere prestaties bij het uitvoeren van digitale signaalverwerkingsalgoritmen wordt dit systeem uitgebreid met Montium TPs. De Montium TP is een grofkorrelig herconfigureerbare processor.

Binnen Æthereal kan uit 2 soorten Netwerk Interfaces gekozen worden: bus of streaming. Het enige bus protocol dat gebruikt is binnen dit project is DTL.

De CCU die ontwikkeld is in dit project heeft 2 interfaces naar het NoC: een streaming interface voor de data verwerking en een Memory-Mapped Input-Output (MMIO) interface voor configuratie en Direct Memory Access (DMA), welke door middel van streaming of door middel van DTL verbonden kan worden aan het NoC. De keuze voor streaming of DTL moet gedaan worden tijdens het systeemontwerp, omdat het geïmplementeerd is als een optionele adapter, welke DTL converteert naar streaming. Om de ontworpen CCU te kunnen testen op een Field Programmable Gate Array (FPGA) evaluatie bord, is een systeem met 2 MicroBlaze processors en 2 Montium TPs verbonden met Æthereal gegenereerd. Een klein programma is successol uitgevoerd op een Xilinx ML605 evaluatie bord, waarop een Virtex-6 FPGA zit. In deze configuratie kan voor de Montium een klok frequentie van 14.82 MHz gebruikt worden. Om een vergelijking met andere CCU's te kunnen maken, is het ontwerp van de CCU, DTL adapter en Montium TP ook gesynthetiseerd voor een Application Specific Integrated Circuit (ASIC). De grootte van de CCU is 0.01478 mm<sup>2</sup> zonder DTL adapter. De DTL adapter heeft een grootte van 0.00149 mm<sup>2</sup>. Deze resultaten werden verkregen met gebruikmaking van een 90 nm laag vermogen bibliotheek en een beperking van de klok frequentie op 400 MHz.

## Preface

This thesis gives an overview of the design and implementation of a CCU which makes it possible to connect the Montium TP to Æthereal NoC.

This report, the VHDL code I wrote, and the intermediate and final presentations are part of my master assignment of the Electrical Engineering Embedded Systems track I followed at the University of Twente. This assignment was carried out in the scope of the NEST project.

For 10 months I have been working on this CCU. I started with research about the subject and related work. Next, I tried to understand the Montium and became familiar with Æthereal.

Almost every fortnight on Tuesday morning, I had a meeting with (a part of) my committee to point out the features to be implemented, to monitor the progress and to discuss the problems I encountered.

These were valuable moments, because it kept up my discipline, gave me new ideas and made me work even harder on my assignment in the days before the meeting.

Of course, I would like to thank everyone who contributed in some way to the final result. Besides the members of the committee, I would like to thank Marcel van de Burgwal for providing tooling and information about the Montium, as well as his assistance during debugging my CCU, which I greatly appreciate.

# Contents

| A        | bstra       | $\operatorname{ct}$                  | i            |  |  |  |

|----------|-------------|--------------------------------------|--------------|--|--|--|

| Pı       | Preface iii |                                      |              |  |  |  |

| C        | onter       | ıts                                  | $\mathbf{v}$ |  |  |  |

| Li       | st of       | Acronyms                             | vii          |  |  |  |

| 1        | Intr        | roduction                            | 1            |  |  |  |

|          | 1.1         | Multi-core trend                     | 1            |  |  |  |

|          | 1.2         | Montium Tile Processor               | 2            |  |  |  |

|          |             | 1.2.1 Montium interface              | 2            |  |  |  |

|          | 1.3         | Beamforming demonstrator             | 3            |  |  |  |

|          | 1.4         | Æthereal NoC                         | 4            |  |  |  |

|          | 1.5         | Assignment description               | 5            |  |  |  |

|          | 1.6         | Related work                         | 5            |  |  |  |

|          | 1.7         | Document structure                   | 6            |  |  |  |

| <b>2</b> | Req         | uirements                            | 7            |  |  |  |

|          | 2.1         | View at system level                 | 7            |  |  |  |

|          |             | 2.1.1 Tasks of the CCU               | 7            |  |  |  |

|          |             | 2.1.2 Communication with other cores | 8            |  |  |  |

|          | 2.2         | Area                                 | 8            |  |  |  |

|          | 2.3         | Clock frequency                      | 8            |  |  |  |

|          |             | 2.3.1 Latency                        | 8            |  |  |  |

|          | 2.4         | Verification                         | 9            |  |  |  |

|          | 2.5         | Debugging                            | 9            |  |  |  |

|          | 2.6         | Montium                              | 9            |  |  |  |

|          |             | 2.6.1 Memory map                     | 9            |  |  |  |

|          |             | 2.6.2 Montium interface              | 10           |  |  |  |

|          |             | 2.6.3 NoC interface                  | 12           |  |  |  |

|          | 2.7         | List of requirements                 | 13           |  |  |  |

| 3        | Stru        | ıctural design                       | 15           |  |  |  |

|          | 3.1         | MMIO interface                       | 16           |  |  |  |

|          |             | 3.1.1 Connection to NoC              | 16           |  |  |  |

|          |             | 3.1.2 MMIO registers                 | 18           |  |  |  |

|          | 3.2         | Streaming interface                  | 22           |  |  |  |

|          |             | 3.2.1 Connection to NoC              | 22           |  |  |  |

## CONTENTS

|             |                                                                              | - I · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22                                                                                                                                     |

|-------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                              | ~ 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 27                                                                                                                                     |

|             | 3.3                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 27                                                                                                                                     |

|             |                                                                              | 3.3.1 ML605 Evaluation Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 28                                                                                                                                     |

|             |                                                                              | 3.3.2 Xilinx MicroBlaze Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28                                                                                                                                     |

|             |                                                                              | 3.3.3 Starburst S-Record Loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28                                                                                                                                     |

| 4           | Dop                                                                          | lization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>29</b>                                                                                                                              |

| 4           | 4.1                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>29</b><br>29                                                                                                                        |

|             | 4.1<br>4.2                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29<br>29                                                                                                                               |

|             | $\frac{4.2}{4.3}$                                                            | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 29<br>30                                                                                                                               |

|             | 4.0                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 30<br>30                                                                                                                               |

|             | 4 4                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|             | 4.4                                                                          | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                                                                                                     |

|             | 4.5                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32                                                                                                                                     |

|             | 4.6                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                                                                     |

|             |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 32                                                                                                                                     |

|             |                                                                              | 4.6.2 Streaming interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                                                                                     |

| 5           | Apr                                                                          | lication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>35</b>                                                                                                                              |

|             | 5.1                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                                     |

|             | -                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 35                                                                                                                                     |

|             | 5.2                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36                                                                                                                                     |

|             | 0.2                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 36                                                                                                                                     |

|             | 5.3                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 37                                                                                                                                     |

|             |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

|             |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                        |

| 6           |                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39                                                                                                                                     |

| 6           | 6.1                                                                          | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39                                                                                                                                     |

| 6           | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$                                    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>40                                                                                                                               |

| 6           | 6.1                                                                          | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>40<br>41                                                                                                                         |

| 6           | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$                                    | Conclusion       Requirement evaluation         Recommendations       Recommendations         6.3.1       Streaming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39<br>40<br>41<br>41                                                                                                                   |

| 6           | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$                                    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>40<br>41                                                                                                                         |

| 6           | $\begin{array}{c} 6.1 \\ 6.2 \end{array}$                                    | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39<br>40<br>41<br>41                                                                                                                   |

|             | $     \begin{array}{r}       6.1 \\       6.2 \\       6.3     \end{array} $ | ConclusionRequirement evaluationRecommendationsRecommendations6.3.1Streaming6.3.2DTL adapter6.3.3Parameterizability6.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 39<br>40<br>41<br>41<br>42<br>42                                                                                                       |

|             | 6.1<br>6.2<br>6.3                                                            | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <ul> <li>39</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>42</li> <li>43</li> </ul>                             |

|             | 6.1<br>6.2<br>6.3                                                            | Conclusion       Requirement evaluation       Recommendations         Recommendations       Recommendations       Recommendations         6.3.1       Streaming       Streaming         6.3.2       DTL adapter       Streaming         6.3.3       Parameterizability       Streaming         J       design specification       Streaming         Æthereal Network Interfaces       Streaming       Streaming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <ul> <li>39</li> <li>40</li> <li>41</li> <li>41</li> <li>42</li> <li>42</li> <li>42</li> <li>43</li> <li>43</li> </ul>                 |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1                                               | Conclusion       Requirement evaluation         Recommendations       Recommendations         6.3.1       Streaming         6.3.2       DTL adapter         6.3.3       Parameterizability         6.3.4       Specification         Æthereal Network Interfaces       A.1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39<br>40<br>41<br>41<br>42<br>42<br>42<br><b>43</b><br>43<br>43                                                                        |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1                                               | Conclusion       Requirement evaluation         Recommendations       Recommendations         6.3.1       Streaming         6.3.2       DTL adapter         6.3.3       Parameterizability         6.3.4       Streaming         6.3.5       Parameterizability         6.3.6       Parameterizability         7       Streaming         8       Parameterizability         9       Streaming         9       Str | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>44                                                                         |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1                                               | Conclusion       Requirement evaluation         Recommendations       Recommendations         6.3.1       Streaming         6.3.2       DTL adapter         6.3.3       Parameterizability         6.3.4       Streaming         6.3.5       Parameterizability         6.3.6       Parameterizability         7       Streaming         9       Design specification         7       A.1.1         Number of network lanes       A.1.1         7       Pinterface         A.2.1       System signals                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44                                                             |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1                                               | Conclusion       Requirement evaluation         Recommendations       6.3.1         Streaming       6.3.2         DTL adapter       6.3.3         Parameterizability       6.3.3         V design specification       6.3.4         Æthereal Network Interfaces       6.3.4         TP interface       6.3.4         A.1.1       Number of network lanes         A.2.1       System signals         A.2.2       Sequencer interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>44<br>44<br>44                                                             |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1                                               | ConclusionRequirement evaluationRecommendations6.3.1Streaming6.3.2DTL adapter6.3.3Parameterizability6.3.4D design specificationÆthereal Network InterfacesA.1.1Number of network lanesTP interfaceA.2.1System signalsA.2.2Sequencer interfaceA.2.3Configuration interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>44                                                 |

|             | 6.1<br>6.2<br>6.3<br><b>CC</b><br>A.1<br>A.2                                 | Conclusion       Requirement evaluation         Recommendations       6.3.1         Streaming       6.3.2         DTL adapter       6.3.3         Parameterizability       6.3.3         Parameterizability       6.3.4         J design specification       6.3.4         Æthereal Network Interfaces       6.3.4         TP interface       6.3.4         A.2.1       System signals         A.2.2       Sequencer interface         A.2.3       Configuration interface         A.2.4       DMA interface                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>44<br>45                                           |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1                                               | Conclusion       Requirement evaluation         Recommendations       Recommendations         6.3.1       Streaming         6.3.2       DTL adapter         6.3.3       Parameterizability         6.3.3       Parameterizability         J       design specification         Æthereal Network Interfaces       A.1.1         Number of network lanes       A.2.1         System signals       A.2.2         A.2.3       Configuration interface         A.2.4       DMA interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>44                                                 |

| A           | 6.1<br>6.2<br>6.3<br>CC<br>A.1<br>A.2<br>A.3<br>A.4                          | Conclusion       Requirement evaluation         Recommendations       6.3.1         Streaming       6.3.2         DTL adapter       6.3.3         Parameterizability       6.3.3         Parameterizability       6.3.4         J design specification       6.3.4         Æthereal Network Interfaces       6.3.4         A.1.1       Number of network lanes         TP interface       6.3.4         A.2.1       System signals         A.2.2       Sequencer interface         A.2.3       Configuration interface         A.2.4       DMA interface         Sequencer       6.3.4         Direct Memory Access       6.3.5                                                                                                                                                                                                                                                                                                                           | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>44<br>45<br>45<br>47                               |

|             | 6.1<br>6.2<br>6.3<br>CC<br>A.1<br>A.2<br>A.3<br>A.4                          | ConclusionRequirement evaluationRecommendations6.3.1Streaming6.3.2DTL adapter6.3.3ParameterizabilityJ design specificationÆthereal Network InterfacesA.1.1Number of network lanesTP interfaceA.2.1System signalsA.2.2Sequencer interfaceA.2.4DMA interfaceSequencerDirect Memory Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39         40         41         41         42         42         43         43         43         44         44         45         45 |

| АВ          | 6.1<br>6.2<br>6.3<br>CC<br>A.1<br>A.2<br>A.3<br>A.4<br>Men                   | Conclusion       Requirement evaluation         Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39<br>40<br>41<br>41<br>42<br>42<br>42<br>43<br>43<br>43<br>44<br>44<br>44<br>44<br>45<br>45<br>47                                     |

| A<br>B<br>C | 6.1<br>6.2<br>6.3<br>CC<br>A.1<br>A.2<br>A.3<br>A.4<br>Men<br>Sou            | Conclusion       Requirement evaluation         Recommendations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39<br>40<br>41<br>41<br>42<br>42<br>43<br>43<br>43<br>43<br>44<br>44<br>44<br>45<br>45<br>47<br>51                                     |

vi

# List of Acronyms

**ADC** Analog to Digital Converter AGU Address Generation Unit **ALU** Arithmetic and Logic Unit  ${\bf ASIC}\,$  Application Specific Integrated Circuit **BE** Best Effort  ${\bf BRAM}$ Block Random Access Memory **CCM** Central Configuration Manager CCU Communication and Configuration Unit **DAC** Digital to Analog Converter DMA Direct Memory Access **DSP** Digital Signal Processing **DTL** Device Transaction Level **FFT** Fast Fourier Transform FIFO First In First Out **FIR** Finite Impulse Response FPGA Field Programmable Gate Array **GPI** General Purpose Input GPO General Purpose Output **GPP** General Purpose Processor **GS** Guaranteed Service **IP** Intellectual Property JTAG Joint Test Action Group LUT Lookup Table MAC Multiply-Accumulate

- viii

- **MMIO** Memory-Mapped Input-Output

- $\mathbf{MP}\text{-}\mathbf{SoC}$  Multiple Processor System-on-Chip

- ${\bf MSB}\,$  Most Significant Bit

- ${\bf NI}\,$  Network Interface

- $\mathbf{NoC}$  Network-on-Chip

- ${\bf PLB}~{\rm Processor}~{\rm Local}~{\rm Bus}$

- ${\bf PPA}~{\rm Processing}~{\rm Part}~{\rm Array}$

- ${\bf RISC}\,$  Reduced Instruction Set Computing

- ${\bf ROM}\,$  Read-Only Memory

- ${\bf RTOS}\,$  Real-Time Operating System

- ${\bf SIO}\,$  Streaming Input-Output

- ${\bf SoC}$ System-on-Chip

- $\mathbf{Tcl} \ \ \mathbf{Tool} \ \ \mathbf{command} \ \ \mathbf{language}$

- ${\bf TP}~$  Tile Processor

- ${\bf UART}\,$  Universal Asynchronous Receiver-Transmitter

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- XMD Xilinx MicroBlaze Debugger

- XML Extensible Markup Language

## Chapter 1

## Introduction

## 1.1 Multi-core trend

For years, new generation CPUs which came to market, had their performance gain mainly due to higher clock frequencies. When this became more difficult, other ways to increase the performance were used. One of those ways to maintain delivering increasing performance, a trend to include more cores into a single die started. Today's mainstream computers are equipped with dual- and quadcore CPUs.

This multi-core trend is also visible in other computer architecture markets where energy efficiency is of more importance, for instance in the mobile phone market [9]. General Purpose Processors (GPPs) are very flexible and can perform many different tasks. Due to this flexibility, the power consumption when a computation is performed on a GPP, is often higher than the same computation on an Application Specific Integrated Circuit (ASIC) or Digital Signal Processor specialized for those computations. There is a trade-off between performance and flexibility. A way to keep or extend processing power, using less energy, can be achieved by adding different cores, each with its own specialism, in a single system. When algorithms are mapped in a clever way on the right cores, the same processing can be performed with decreased energy consumption [15].

"Many-core architectures" is an active research subject. A toolchain to generate a Multiple Processor System-on-Chip (MP-SoC) with an arbitrary number of MicroBlazes was available, this toolchain is called 'Starburst'. It can generate an Æthereal Network-on-Chip (NoC) (see Section 1.4) with an arbitrary number of MicroBlaze Soft-Core Processors. The MicroBlaze Soft-Core processor is a processor from Xilinx based on a 32-bits RISC architecture. Also a DDR memory controller and peripherals like LEDs and UARTs are accessible via the NoC.

A MicroBlaze takes multiple clock cycles for a Multiply-Accumulate (MAC) operation. In many Digital Signal Processing (DSP) algorithms the MAC operation is often used. Therefore the MicroBlaze is not well suited to do energy efficient streaming DSP. Specialized DSP cores can perform a MAC operation in a single clock cycle, consuming less energy than the MicroBlaze for the same computation. Streaming is processing of data sample by sample, in contrast to block-based processing, which processes blocks of samples. A useful addition

to the Starburst System-on-Chip (SoC) Generator is another processing core which is more suited to do energy efficient streaming signal processing than a MicroBlaze processor.

## 1.2 Montium Tile Processor

In 2004, a coarse-grained reconfigurable processor, called Montium TP, was developed by Paul Heysters. The Montium is specialized in DSP operations like Finite Impulse Response (FIR)-filtering and Fast Fourier Transforms (FFTs). In most DSP algorithms the MAC operation is frequently used. The Montium can do 5 MAC operations within one clock cycle, which makes the Montium powerful in DSP applications.

Another property of the Montium is that on beforehand is known how long processing steps take and on every clock cycle it is known which instruction is executed on the Montium. The Montium processing structure is straightforward and the Montium is not disturbed by for instance interrupts where GPPs may suffer from. The Æthereal NoC is also capable of giving bandwidth and latency guarantees. This combination of Æthereal and the Montium makes it possible to give latency guarantees, which are required in some applications.

The properties of the Montium mentioned before make the Montium a useful addition to a many-core system currently only consisting of MicroBlazes.

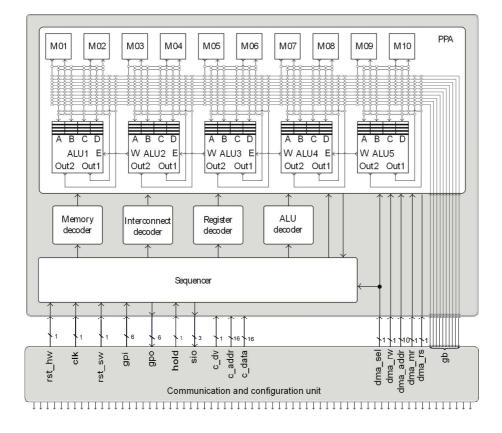

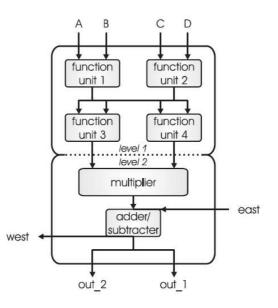

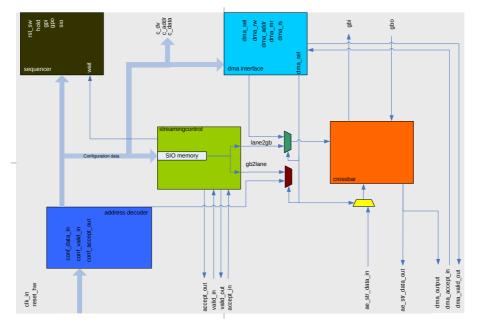

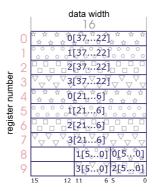

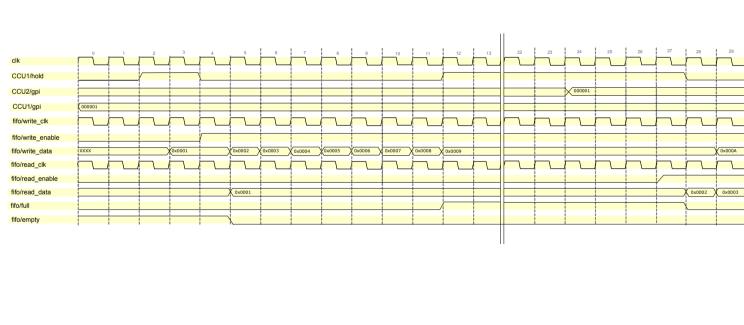

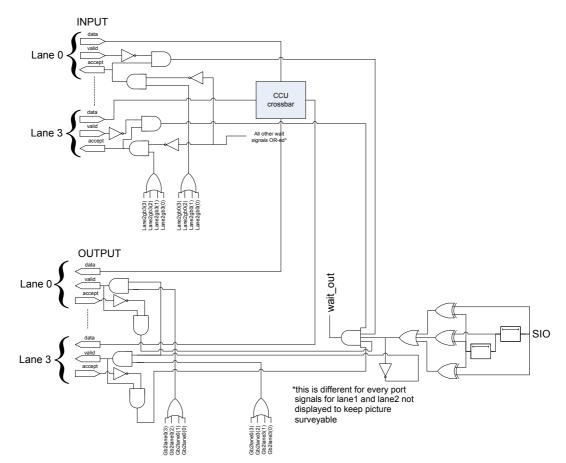

The structure of the Montium is shown in Figure 1.1. The Montium has 10 global busses, which are mainly used for internal communication in the Montium Tile Processor (TP), for example to transfer data between Arithmetic and Logic Units (ALUs). On the right side can be seen that the 10 global busses of the Montium are directly connected to the Communication and Configuration Unit (CCU). The Montium processor has 5 ALUs. Every ALU has two local memories, a left local memory and a right local memory. Those memories are numbered M01...M10 in Figure 1.1. The size of those local memories is parameterizable, because memories are area-hungry and it depends on the application which sizes of local memories are necessary. In the configuration used during this project, the local memories have a depth of 1024 words and a data width of 16 bits. Due to the locality of reference principle, the local memories contribute to the energy-efficiency of the Montium [4]. Every ALU has 4 input register banks, often referred to as register A, B, C or D. A more detailed schematic drawing of an ALU is shown in Figure 1.2. The ALU is split up in 2 levels: level1 and level2. Level1 is for reconfigurable bitwise functions, (saturated) additions, (saturated) subtractions, logic shift left (only function unit 1 and 2) or logic shift right (only function unit 1 and 2) and determine maximum or minimum of two values (only function unit 3 and 4). Level2 is for the MAC operation [7].

#### 1.2.1 Montium interface

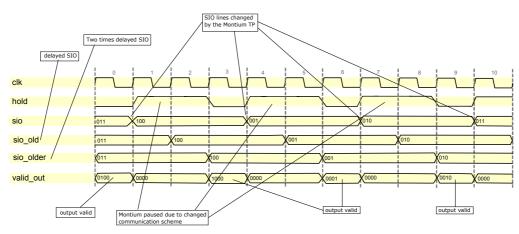

The interface of the Montium is not compatible with the Æthereal Network Interfaces (NIs). To make it possible to connect the Montium to a NoC, a CCU is necessary. The CCU takes care of the communication with the NoC: it routes the output of the Montium busses to the right output connection and routes the input to the right Montium bus. The Montium can be paused by the CCU. The

Figure 1.1: Montium structure and interface to CCU

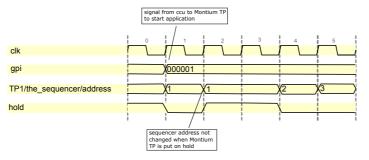

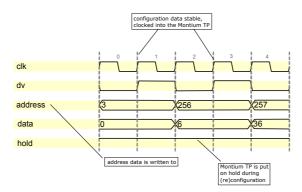

interface of the Montium is shown in Figure 1.1. The interface as shown in the figure is the interface as used in this project. The number of streaming IO pins and the number of synchronization pins (called General Purpose Input (GPI) and General Purpose Output (GPO)) are parameterizable. On the left side the sequencer interface is visible, which controls the program execution. The CLK and RST\_HW are connected to the clock network and the system wide reset. Near the Streaming Input-Output (SIO) lines, the configuration interface is shown. When a data and address pair is available on C\_ADDR and C\_DATA the C\_DV line is driven high to clock in the configuration data (shown in Figure 2.2). Using the Direct Memory Access (DMA) interface, data from local memories or register files can be read by a GPP in the NoC. During a DMA transfer, the Montium is paused.

### **1.3** Beamforming demonstrator

A possible application of the multi-core SoC consisting of MicroBlaze cores and Montium TPs is beamforming. Beamforming is a technique which can make a receiver more sensitive for signals from a certain direction, using multiple

Figure 1.2: Montium ALU structure

antennas. This technique has its origin in radar applications, where it is known as phased array. After the signal from the antenna is digitized, digital signal processing techniques can be used. Using digital signal processing, the signal can be combined such that the array is more sensitive in a certain direction. Due to the multiple antennas involved with beamforming, a lot of DSP is needed. Also the power consumption of this processing is important, because devices, which can be usefully extended with beamforming features, are often mobile devices using wireless communication, like mobile phones, notebooks, netbooks and bluetooth peripherals. Nowadays those devices receive from all directions and transmit to all directions. Making those devices directional, the same Signal-to-Noise Ratio can be achieved, using less power. In these mobile devices, power consumption is an important design aspect, because it influences the battery rundown time.

## 1.4 Æthereal NoC

The NoC used in the Starburst SoC Generator is Æthereal. Æthereal is a composable and predictable on-chip interconnect developed at NXP [3]. In a composable platform, one application cannot change the behaviour of another application. This allows design and verification of applications in isolation. Æthereal can be used in a real-time environment, because it is able to guarantee minimum throughput and maximum latency [3]. Æthereal offers two types of connections:

- Guaranteed Service (GS) guaranteed throughput and bounded latency

- Best Effort (BE) to exploit NoC capacity unused by GS traffic for noncritical communication

#### 1.5. ASSIGNMENT DESCRIPTION

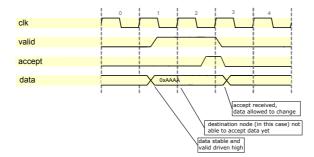

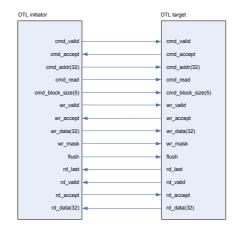

Æthereal uses streaming interfaces for its communication. For other protocols, i.e. protocols which need data and address ports, a shell can be used. The protocol shells bridge between a bus protocol and the streaming ports of the network [3]. In Figure 1.3 a schematic drawing of a target protocol shell as used in Æthereal is displayed. On the left of the figure the signals as used in the protocol and on the right side a streaming interface connected to the network is drawn.

Figure 1.3: Target protocol shell as used in Æthereal

A drawback of these different interfaces is that it is not possible in Æthereal to send data from a streaming NI to a Device Transaction Level (DTL) NI or vice versa.

## 1.5 Assignment description

The assignment for this Master's thesis is the design and implementation of a CCU which is able to connect a Montium TP to the Æthereal NoC as used in the Starburst SoC Generator. Within this research it is necessary to specify requirements of the CCU, programming the CCU and testbenches in VHDL and connect the CCU to Æthereal and to the Montium TP. After functional simulation of the whole system, the extended Starburst system has to be successfully tested on the Xilinx ML605 evaluation board.

## 1.6 Related work

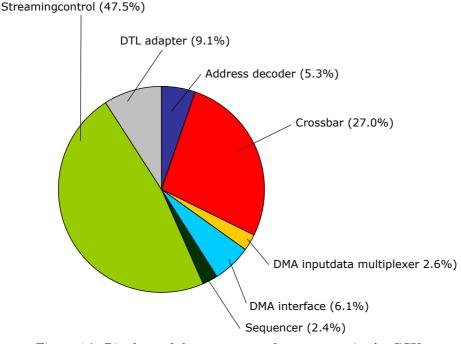

In [11], a network interface called Hydra is described. It is mentioned that there is not much related work on network interfaces, because it is often presented as a minor addition to a NoC and network interfaces are assumed to be straightforward. It is also stated that the design decisions in the NoC interface are important for the performance of the overall system. A CCU accommodates the communication between a Montium TP and the NoC. A circuit-switched NoC [13] and a packet-switched NoC [5] are used. The CCU is synthesized in 0.13  $\mu m$  with a constraint on the clock frequency of 200 MHz. This resulted in about 19000 gates (0.106  $mm^2$ ), which is about 5% of the area of the Montium TP [8]. A large part (41.5%) of the total area is needed for input buffering and

output buffering. The crossbar connecting the 10 Montium busses to 4 network lanes only uses 9.5% of the CCU area. The NoC uses flits for communication. The flow control and flit formatting are responsible for 20% of the total area.

## 1.7 Document structure

In this chapter, an introduction to the subject has been given. It also treated the scope of the project. In chapter 2, the requirements of the CCU are explained. Chapter 3 describes the implementation of the CCU. Chapter 4 gives Field Programmable Gate Array (FPGA) and ASIC synthesis results and the data rates that can be achieved when using the CCU. In chapter 5, a communication application is mapped onto the two Montium cores to show a working CCU. In the last chapter the conclusions and recommendations are presented. Three appendices are added to this report: a design specification, a memory map and the source code for a small application which was executed on the FPGA board.

## Chapter 2

## Requirements

In this chapter the requirements of the CCU are specified. It is divided into three sections: the tasks of the CCU, the interface description to the Montium and the interface description to the NoC NIs. As already mentioned in the introduction, on the NoC side, the type of interface (Memory-Mapped Input-Output (MMIO) or streaming) and the number of interfaces are configurable. On the Montium interface side, the number of streaming IO and the number of GPI and GPO pins are parameterizable.

## 2.1 View at system level

The Montium TP has to be configured, before any processing can be done by the Montium TP. This means the Montium TP is dependent on the configuration data from the NoC. After startup of a system containing a Montium TP, the first task of the CCU is routing configuration data from the NoC to the Montium. After the Montium is configured, the Montium can select the communication scheme using the SIO lines. With these SIO lines, network lanes are connected to global busses of the Montium.

### 2.1.1 Tasks of the CCU

The CCU has the following tasks [10]:

- load data to be processed from the NoC

- store (partly) processed data to the NoC

- pause the Montium core (necessary when DMA operations are done, input data is unavailable or saving energy when no work is available)

- restart the Montium TP from pause

- reset the Montium TP

- configure the Montium TP

The network is not configured by the CCU. In Æthereal, there is one processor which has a connection to the configuration port of the NoC. This processor opens and closes connections between cores connected to the NoC.

A difference between the CCU described in reference [10] and this CCU is the location of the clock domain crossing. The Æthereal NoC takes care of the correct exchange of data between different clock domains, in contrast to the CCU described in reference [10] where the clock domain crossing is inside the CCU by means of dual port asynchronous FIFOs.

## 2.1.2 Communication with other cores

As mentioned in section 1.4, Æthereal supports a streaming protocol as well as bus protocols. In the Starburst SoC generator, the MicroBlazes are only connected by a DTL interface. Therefore the Montium TP cores have to be configured by DTL. For communication with other Montium TP cores a streaming interface can better be used, because a streaming interface has less overhead than DTL and is faster.

## 2.2 Area

The area usage of a chip is an important design parameter as there is a strong relation between the area usage of a chip and its price [2] and its power consumption. Therefore it is important to keep the area of the CCU as small as possible. An estimate of an area requirement can be made by taking the Hydra CCU as a reference. The Hydra uses 0.106  $mm^2$  in 0.13  $\mu m$  technlogy, which is about 5% of the area of the Montium TP [11]. As in the CCU connecting Æthereal to the Montium, some memory inside the CCU is unnecessary (see section 2.6.1), a requirement is that the CCU must use less than 5% of the area of the Montium TP.

## 2.3 Clock frequency

The clock frequency of the CCU has to be the same as the Montium, because the clock domain crossing is handled by Æthereal. It is important that the CCU will not be the limiting factor for the clock frequency of the Montium TP. In other words: the longest combinatorial path has to be inside the Montium TP and not in the CCU.

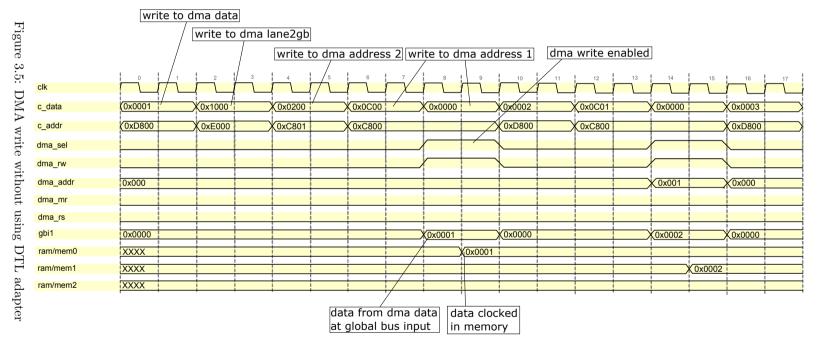

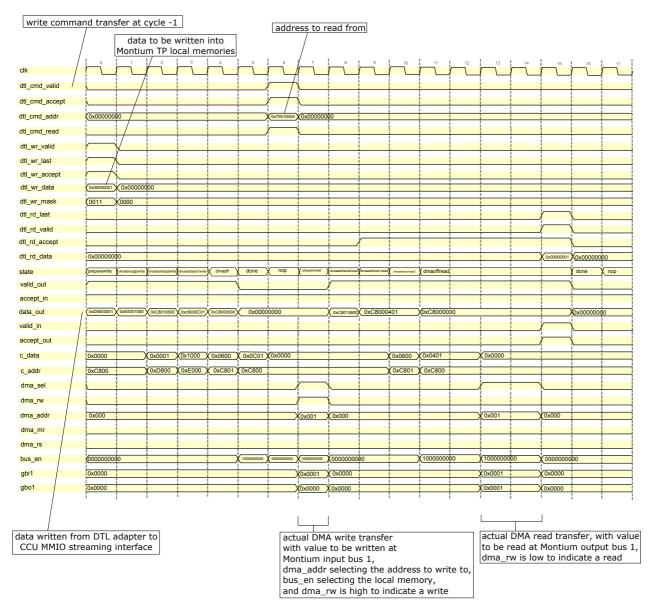

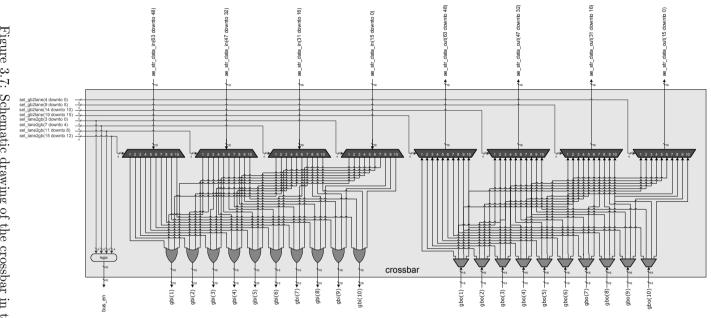

#### 2.3.1 Latency