# **UNIVERSITY OF TWENTE.**

Faculty of Electrical Engineering, Mathematics & Computer Science

# Evaluating Performance and Energy Efficiency of the Hybrid Memory Cube Technology

ing. A.B. (Arvid) van den Brink Master Thesis August 2017

Exam committee:

dr. ir. A.B.J. (André) Kokkeler ir. E. (Bert) Molenkamp ir. J. (Hans) Scholten S.G.A. (Ghayoor) Gillani, M.Sc.

Computer Archtecture for Embedded Systems Group Faculty of Electrical Engineering, Mathematics and Computer Science University of Twente P.O. Box 217 7500 AE Enschede The Netherlands

### Abstract

Embedded systems process fast and complex algorithms these days. Within these embedded systems, memory becomes a major part. Large (amount of bytes), small (in terms of area), fast and energy efficient memories are needed not only in battery operated devices but also in High Performance Computing systems to reduce the power consumption of the total system.

Many systems implement their algorithm in software, usually implying a sequential execution. The more complex the algorithm, the more instructions are executed and therefore the execution time and power consumption increases accordingly. Parallel execution can be used to compensate for the increase in execution time introduced by the sequential software. For parallel execution of regular, structured algorithms, hardware solutions, like an FPGA, can be used. Only the physical boundaries of FPGAs limits the amount of parallelism.

In this thesis a comparison is made between two systems. The first system is using the Hybrid Memory Cube memory architecture. The processing element in this system is an FPGA. The second system is a common of the shelf graphical card, containing GDDR5 memory with a GPU as processing unit.

The Hybrid Memory Cube memory architecture is used to give an answer to the main research question: "*How does the efficiency of the Hybrid Memory Cube compare to GDDR5 memory?*". The energy efficiency and the performance, in terms of speed, are compared to a common of the shelf graphical card. Both systems provide the user with a massively parallel architecture.

Two benchmarks are implemented to measure the performance of both systems. The first is the data transfer benchmark between the host system and the device under test and the second is the data transfer benchmark between the GPU and the GDDR5 memory (AMD Radeon HD7970) or the FPGA and the HMC memory. The benchmark results show an average speed performance gain of approximately  $5.5 \times$  in favour of the HMC system.

Due to defective HMC hardware, only power measurements are compared when both the graphical card and HMC system were in the *Idle* state. This resulted that the HMC system is approximately 34.75% more energy efficient than the graphical card.

To my wife, Saloewa, who supported me the last three years pursuing my dreams.

# Contents

| At | ostrac                                               | t                           | i                                                                                                                                                                                 |

|----|------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Li | st of                                                | igures                      | viii                                                                                                                                                                              |

| Li | st of '                                              | ables                       | ix                                                                                                                                                                                |

| GI | ossa                                                 | y                           | xi                                                                                                                                                                                |

| 1  | Intro<br>1.1<br>1.2<br>1.3                           | duction<br>Context          | <b>1</b><br>1<br>3<br>3                                                                                                                                                           |

| I  | Bac                                                  | kground                     | 5                                                                                                                                                                                 |

| 2  | Rela                                                 | ed Work                     | 7                                                                                                                                                                                 |

| 3  | Men<br>3.1<br>3.2<br>3.3<br>3.3<br>3.4<br>3.5<br>3.6 | Principles of operation     | <ol> <li>9</li> <li>10</li> <li>12</li> <li>12</li> <li>13</li> <li>13</li> <li>13</li> <li>14</li> <li>15</li> <li>15</li> <li>17</li> <li>19</li> <li>25</li> <li>26</li> </ol> |

| 4  | <b>Ben</b><br>4.1<br>4.2<br>4.3                      | Device transfer performance | <b>29</b><br>30<br>31<br>31                                                                                                                                                       |

|    | 4.3.1 Median Filter                                                                                                                                                                                          | 31 |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5  | Power and Energy by using Current Measurements                                                                                                                                                               | 35 |

| 6  | Power Estimations                                                                                                                                                                                            | 39 |

|    | <ul> <li>6.1 Power Consumption Model for AMD Graphics Processing Unit (GPU) (Graphics Construction (GCN)).</li> <li>6.2 Power Consumption Model for HMC and Field Programmable Gate Array (FPGA).</li> </ul> | 40 |

|    |                                                                                                                                                                                                              |    |

| II | Realisation and results                                                                                                                                                                                      | 43 |

| 7  | MATLAB Model and Simulation Results                                                                                                                                                                          | 45 |

|    | 7.1 Realisation                                                                                                                                                                                              |    |

|    | 7.1.1 Image Filtering                                                                                                                                                                                        |    |

|    | 7.2 Results                                                                                                                                                                                                  |    |

|    | 7.2.1 MATLAB results                                                                                                                                                                                         | 46 |

| 8  | Current Measuring Hardware                                                                                                                                                                                   | 47 |

|    | 8.1 Realisation                                                                                                                                                                                              | 47 |

|    | 8.2 Results                                                                                                                                                                                                  | 48 |

| 9  | GPU Technology Efficiency                                                                                                                                                                                    | 51 |

|    | 9.1 Realisation                                                                                                                                                                                              |    |

|    | 9.1.1 Host/GPU system transfer performance                                                                                                                                                                   | 51 |

|    | 9.1.2 GPU system local memory (GDDR5) transfer performance                                                                                                                                                   | 52 |

|    | 9.1.3 GPU energy efficiency test                                                                                                                                                                             | 52 |

|    | 9.2 Results                                                                                                                                                                                                  |    |

|    | 9.2.1 Host/GPU transfer performance                                                                                                                                                                          |    |

|    | 9.2.2 GPU/GDDR5 transfer performance                                                                                                                                                                         |    |

|    | 9.2.3 GDDR5 energy efficiency results                                                                                                                                                                        | 55 |

| 10 | 0 Hybrid Memory Cube Technology Efficiency                                                                                                                                                                   | 57 |

|    | 10.1 Realisation                                                                                                                                                                                             | 57 |

|    | 10.1.1 Memory Controller Timing Measurements                                                                                                                                                                 |    |

|    | 10.1.1.1 User Module - Reader                                                                                                                                                                                |    |

|    | 10.1.1.2 User Module - Writer                                                                                                                                                                                |    |

|    | 10.1.1.3 User Module - Arbiter                                                                                                                                                                               |    |

|    | 10.1.2 Memory Controller Energy Measurements                                                                                                                                                                 |    |

|    | 10.2 Results                                                                                                                                                                                                 |    |

|    | 10.2.2 HMC energy efficiency results                                                                                                                                                                         |    |

|    |                                                                                                                                                                                                              | 00 |

|    | I Conclusions and future work                                                                                                                                                                                | 65 |

| 11 | 1 Conclusions                                                                                                                                                                                                | 67 |

| •• | 11.1 General Conclusions                                                                                                                                                                                     |    |

|    | 11.2 HMC performance                                                                                                                                                                                         |    |

|    | 11.3 HMC power consumption                                                                                                                                                                                   |    |

|     | 11.4 HMC improvements                                                                                                                                                  | 69                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 12  | Future work         12.1 General future work         12.2 Hybrid Memory Cube Dynamic power         12.3 Approximate or Inexact Computing         12.4 Memory Modelling | <b>71</b><br>71<br>71<br>71<br>71 |

| IV  | Appendices                                                                                                                                                             | 73                                |

| A   | Mathematical Image Processing         A.1       Image Restoration         A.1.1       Denoising         A.1.1.1       Random noise                                     | <b>75</b><br>75<br>75<br>75       |

| в   | Arduino Current Measure Firmware                                                                                                                                       | 79                                |

| С   | Field Programmable Gate Array                                                                                                                                          | 81                                |

| D   | Test Set-up                                                                                                                                                            | 85                                |

| Е   | Graphics Processing Unit                                                                                                                                               | 87                                |

| F   | Riser Card                                                                                                                                                             | 89                                |

| G   | Benchmark C++/OpenCL Code                                                                                                                                              | 93                                |

| н   | Image Denoising OpenCL Code                                                                                                                                            | 107                               |

| I   | MATLAB Denoise Code                                                                                                                                                    | 109                               |

| Ine | dex                                                                                                                                                                    | 111                               |

| Bi  | bliography                                                                                                                                                             | 113                               |

# **List of Figures**

| 2.1        | HMC module: AC510 board                                                                                                                                    | 8  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1        | Temporal locality: Refer to block again                                                                                                                    | 9  |

| 3.2        | Spatial locality: Refer nearby block                                                                                                                       | 9  |

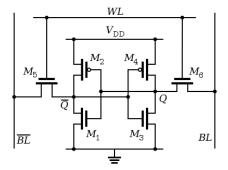

| 3.3        | Six transistor SRAM cell                                                                                                                                   | 10 |

| 3.4        | Four transistor SRAM cell                                                                                                                                  | 11 |

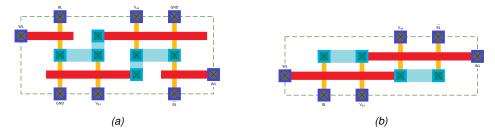

| 3.5        | SRAM cell layout: (a) A six transistor cell; (b) A four transistor cell                                                                                    | 11 |

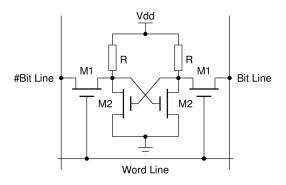

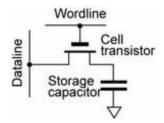

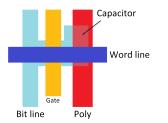

| 3.6        | One transistor, one capacitor DRAM cell                                                                                                                    | 11 |

| 3.7        | One transistor, one capacitor cell                                                                                                                         | 12 |

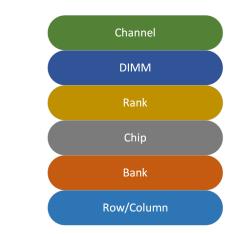

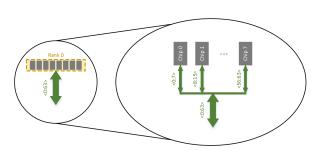

| 3.8        | Dual In-Line Memory Module memory subsystem organisation                                                                                                   | 15 |

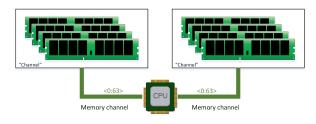

| 3.9        | Dual In-Line Memory Module (DIMM) Channels                                                                                                                 | 16 |

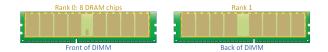

| 3.10       | DIMM Ranks                                                                                                                                                 | 16 |

| 3.11       | DIMM Rank breakdown                                                                                                                                        | 16 |

| 3.12       | DIMM Chip                                                                                                                                                  | 17 |

| 3.13       | DIMM Bank Rows and Columns                                                                                                                                 | 17 |

| 3.14       | Double Data Rate type 5 Synchronous Graphics Random Access Memory (GDDR5) .                                                                                | 18 |

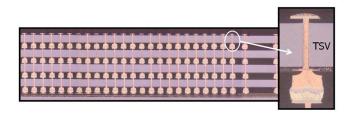

| 3.15       | Cross Sectional Photo of HMC Die Stack Including Through Silicon Via (TSV) Detail                                                                          |    |

|            | (Inset) [1]                                                                                                                                                | 19 |

| 3.16       | HMC Layers [2]                                                                                                                                             | 19 |

| 3.17       | Example HMC Organisation [3]                                                                                                                               | 20 |

| 3.18       | HMC Block Diagram Example Implementation [3]                                                                                                               | 21 |

|            | Link Data Transmission Example Implementation [3]                                                                                                          | 22 |

|            | Example of a Chained Topology [3]                                                                                                                          | 23 |

| 3.21       | Example of a Star Topology [3]                                                                                                                             | 23 |

| 3.22       | Example of a Multi-Host Topology [3]                                                                                                                       | 24 |

|            | Example of a Two-Host Expanded Star Topology [3]                                                                                                           | 24 |

| 3.24       | HMC implementation: (a) 2 Links; (b) 32 Lanes (Full width link)                                                                                            | 25 |

| 3.25       | GDDR5 - Pseudo Open Drain (POD)                                                                                                                            | 26 |

|            |                                                                                                                                                            |    |

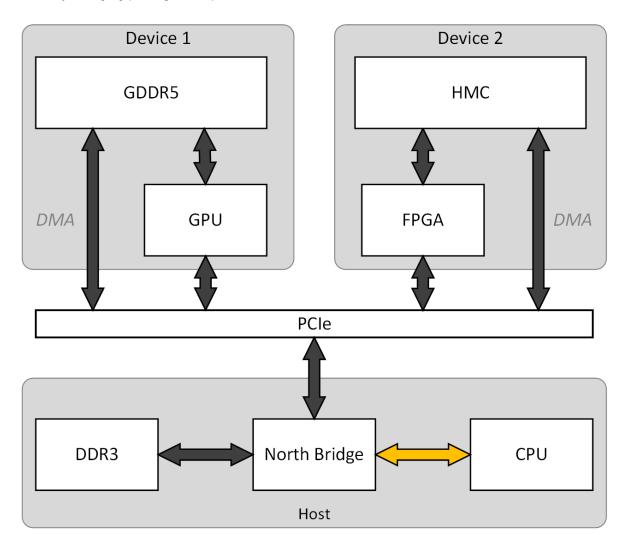

| 4.1        | Functional block diagram of test system                                                                                                                    | 29 |

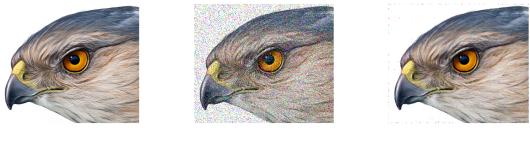

| 4.2        | Denoising example: (a) Original; (b) Impulse noise; (c) Denoised ( $3 \times 3$ window)                                                                    | 33 |

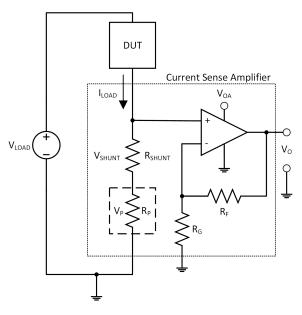

| 5.1        | Current Sense Amplifier                                                                                                                                    | 37 |

|            |                                                                                                                                                            | •  |

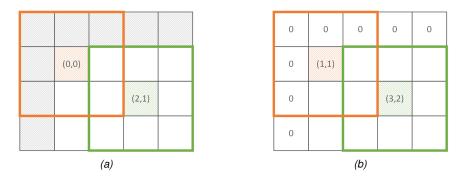

| 7.1<br>7.2 | Median Filtering: (a) Boundary exceptions; (b) No Boundary exceptions MATLAB Simulation: (a) Original; (b) Impulse Noise; (c) Filtered (3x3); (d) Filtered | 45 |

|            | (25x25)                                                                                                                                                    | 46 |

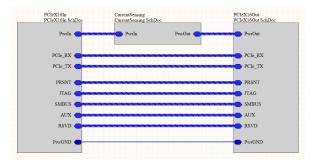

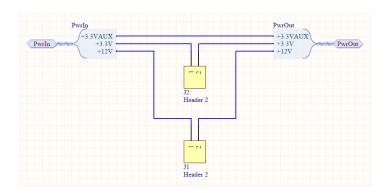

| 8.1        | Riser card block diagram                                                                                                                                   | 47 |

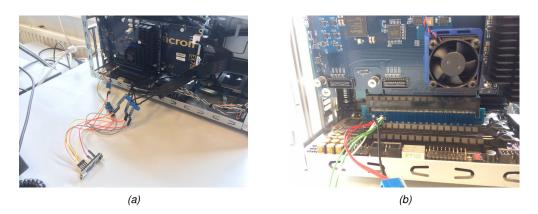

| 8.2                          | Test set-up: (a) Overview; (b) Riser card Printed Circuit Board (PCB) - with HMC Backplane inserted      | 48                         |

|------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|

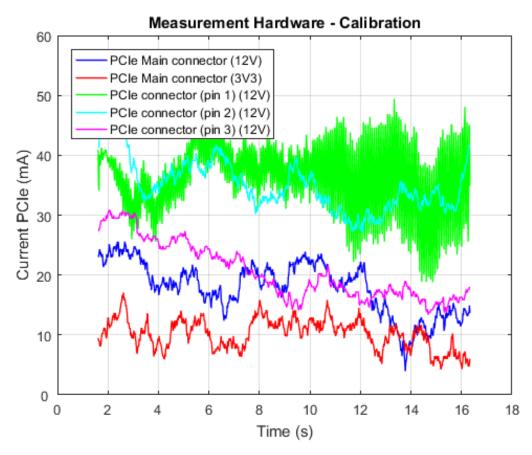

| 8.3<br>8.4<br>8.5            | Hall Sensor board ACS715 - Current Sensing                                                               | 48<br>48<br>48<br>50       |

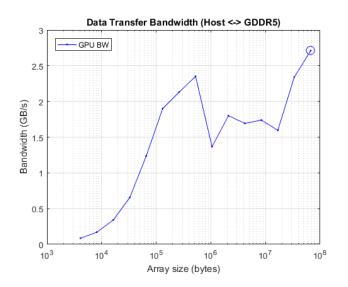

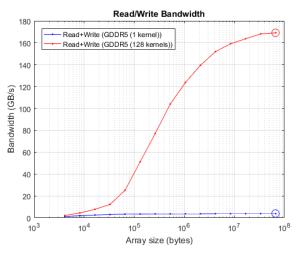

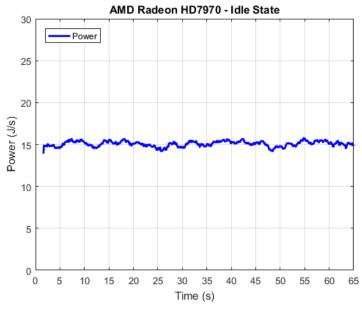

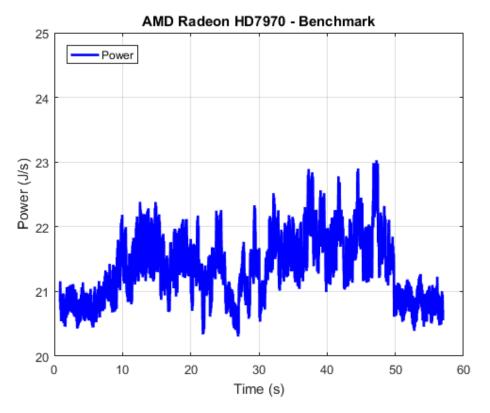

| 9.1<br>9.2<br>9.3<br>9.4     | Host to GPU Bandwidth       GPU Local memory Bandwidth         GPU Idle Power       GPU Benchmark Power  | 53<br>54<br>55<br>56       |

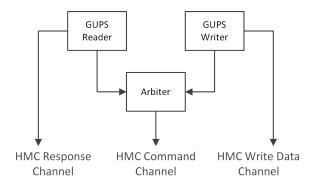

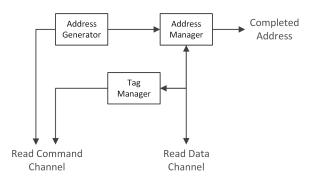

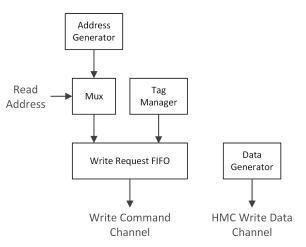

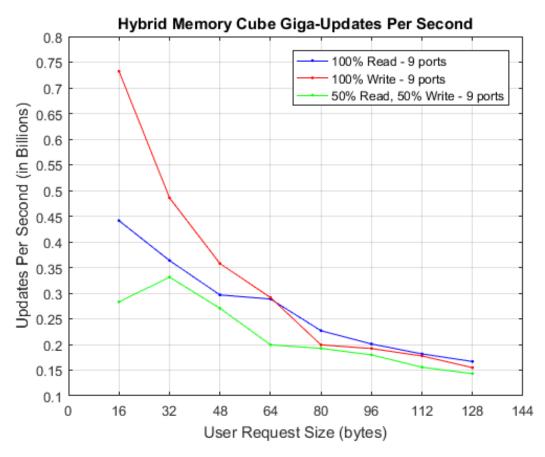

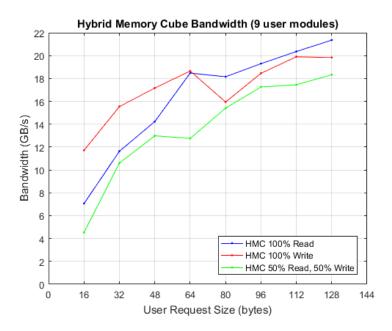

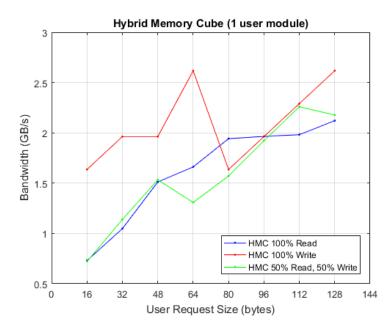

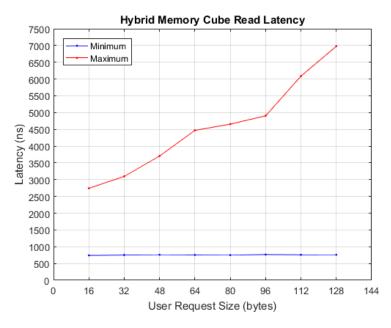

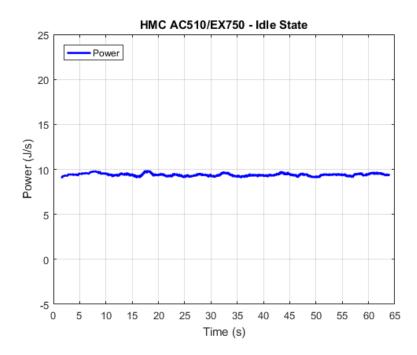

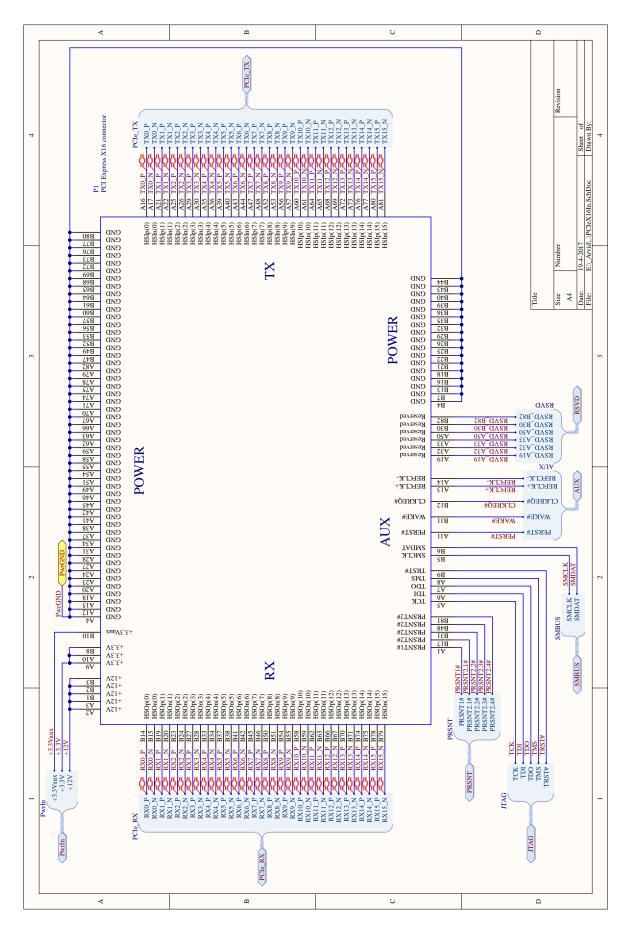

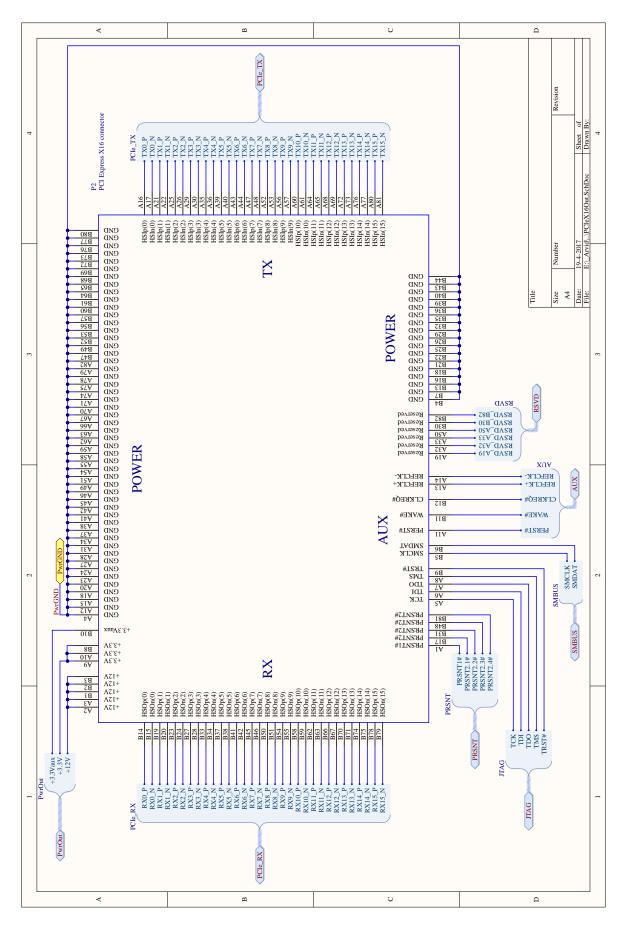

| 10.2<br>10.3<br>10.4<br>10.5 | Hybrid Memory Cube Memory Controller - User Module Top Level                                             | 58<br>59<br>59<br>61<br>62 |

| 10.7                         | Access Memory (DDR3) Bandwidth       Hybrid Memory Cube Read Latency         HMC Idle Power       Hereit | 62<br>63<br>63             |

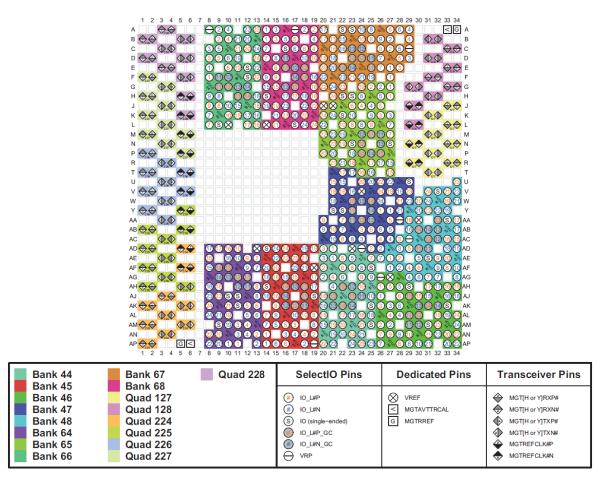

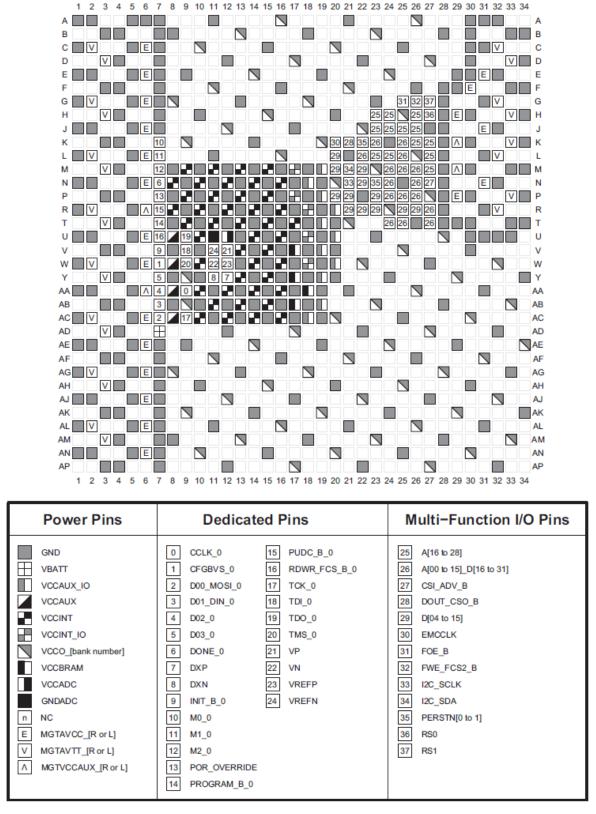

| C.2<br>C.3                   | XCKU060 Banks                                                                                            | 81<br>81<br>82<br>83       |

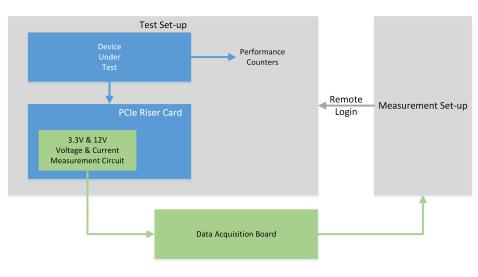

| D.1                          | Test Set-up block diagram                                                                                | 85                         |

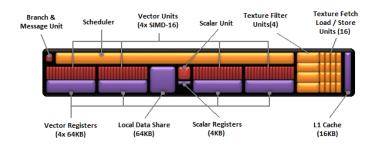

| E.1<br>E.2                   | AMD Radeon HD 7900-Series Architecture                                                                   | 87<br>87                   |

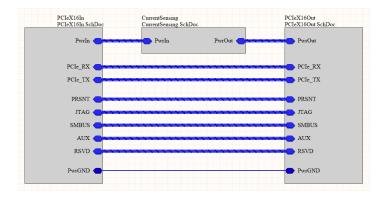

| F.1<br>F.2<br>F.3<br>F.4     | Riser card block diagram                                                                                 | 89<br>89<br>90             |

|                              | section                                                                                                  | 91                         |

# **List of Tables**

|      | RAM main operations       Memory energy comparison                                                                        |    |

|------|---------------------------------------------------------------------------------------------------------------------------|----|

| 4.1  | PCIe link performance                                                                                                     | 30 |

| 5.1  | Current sensing techniques                                                                                                | 38 |

| 7.1  | Median Filter Image Sizes                                                                                                 | 46 |

| 8.1  | AC715 Hall sensors average current - Power off                                                                            | 49 |

|      | Host to GPU Bandwidth       GPU Local memory Bandwidth         GPU Local memory Bandwidth       GPU Median Filter Metrics | 55 |

| 10.1 | Hybrid Memory Cube Bandwidth (9 user modules)                                                                             | 61 |

| 11.1 | Memory Bandwidth Gain                                                                                                     | 68 |

|      | Kintex UltraScale FPGA Feature Summary                                                                                    |    |

# Glossary

| ADC   | Analog to Digital Converter                                          | HPC    | High Performance Computing                 |

|-------|----------------------------------------------------------------------|--------|--------------------------------------------|

| ΑΡΙ   | Application Programming Interface                                    | HPCC   | HPC challenge                              |

| ASIC  | Application Specific Integrated Circuit                              | IC     | Integrated Circuit                         |

| BFS   | Breadth-First Search                                                 | I/O    | Input/Output                               |

| CAS   | Column Address Select                                                | LFSR   | Linear Feedback Shift Register             |

| CBR   | CAS Before RAS                                                       | LM     | Link Master                                |

| СК    | Command Clock                                                        | LS     | Link Slave                                 |

| CMOS  | Complementary Metal Oxide Semiconductor                              | MCU    | Micro Controller Unit                      |

| CMV   | Common-mode Voltage                                                  | MOSFET | Metal-Oxide-Semiconductor Field-Effect     |

| CMR   | Common-mode Rejection                                                |        | Transistor                                 |

| CNN   | Convolutional Neural Network                                         | MRI    | Magnetic Resonance Imaging                 |

| CPU   | Central Processing Unit                                              | ODT    | On-Die Termination                         |

| CSP   | Central Signal Processor                                             | -      | Open Computing Language                    |

| DDR   | Double Data Rate SDRAM                                               | P2P    | Point-To-Point                             |

| DDR3  | Double Data Rate type 3 Synchronous Dynamic                          | P22P   | Point-To-Two-Point                         |

|       | Random Access Memory                                                 | PC     | Personal Computer                          |

| DIMM  | Dual In-Line Memory Module                                           | PCB    | Printed Circuit Board                      |

| DLL   | Delay Locked Loop                                                    | PCle   | Peripheral Component Interconnect Express  |

| DMA   | Direct Memory Access                                                 | PDF    | Probability Density Function               |

| DRAM  | Dynamic Random Access Memory                                         | PLL    | Phase Locked Loop                          |

| DSP   | Digital Signal Processing                                            | POD    | Pseudo Open Drain                          |

| DUT   | Device Under Test                                                    | RAM    | Random Access Memory                       |

| DVFS  | Dynamic Voltage/Frequency Scaling                                    | RAS    | Row Address Select                         |

| EOL   | End Of Life                                                          | ROR    | RAS Only Refresh                           |

| FLIT  | Flow Unit                                                            | SDP    | Science Data Processor                     |

| FPGA  | Field Programmable Gate Array                                        | SDRAM  | Synchronous Dynamic Random Access Memory   |

| GCN   | Graphics Core Next                                                   | SGRAM  | Synchronous Graphics Random Access Memory  |

| GDDR  | Double Data Rate Synchronous Graphics                                | SKA    | Square Kilometre Array                     |

|       | Random Access Memory                                                 | SLID   | Source Link Identifier                     |

| GDDR5 | Double Data Rate type 5 Synchronous Graphics<br>Random Access Memory | SR     | Self Refresh                               |

| ODU   | •                                                                    | SRAM   | Static Random Access Memory                |

| GPU   | Graphics Processing Unit                                             | TSV    | Through Silicon Via                        |

| GUPS  | Giga-Updates Per Second                                              | VHDL   | VHSIC (Very High Speed Integrated Circuit) |

| HBM   | High Bandwidth Memory                                                |        | Hardware Description Language              |

| HDL   | Hardware Description Language                                        | WCK    | Write Clock                                |

| HMC   | Hybrid Memory Cube                                                   | WE     | Write Enable                               |

# Chapter 1

# Introduction

#### 1.1 Context

Many embedded systems are using fast and complex algorithms to perform the designated task these days. The execution of these algorithms commonly requires a Central Processing Unit (CPU), memory and storage. Nowadays, memory becomes a major part of these embedded systems. The demand for larger memory sizes in increasingly smaller and faster devices requires a memory architecture that occupies less area, performs at higher speeds and uses less power consumption. Not only in battery operated devices the power consumption is a key feature, also in High Performance Computing (HPC) systems the total power consumption is important. For example, a smartphone user wants to use the phone for many hours without the need of recharging the smartphone or like the HPC systems used for the international Square Kilometre Array (SKA) telescope [4] by one of its partners ASTRON [5], where the energy consumption is becoming a major concern as well. This HPC system consist of the Central Signal Processor (CSP) [6] and the Science Data Processor (SDP) [7] elements and many more. These elements consume multiple megawatts of power. Reducing the power consumption in these systems is as important as in mobile, battery powered devices.

To reduce the amount of energy used by a system, a new kind of memory architecture, like the Hybrid Memory Cube (HMC) [8], can be used. Despite the reduction in area and energy usage and the increase in speed, the rest of the system still uses the same computer architecture as the general purpose systems and therefore the system is not fully optimised for the execution of the same algorithms. Introducing an FPGA, to create optimised Digital Signal Processing (DSP) blocks, can also reduce the amount of energy and time needed for the complex tasks. The FPGA is a specialised Integrated Circuit (IC) containing predefined configurable hardware resources, like *logic blocks* and *DSPs*. By configuring the FPGA, any arbitrary digital circuit can by made.

The computational power needed depends on the complexity of the executed algorithm. Using a general purpose CPU needs the algorithm to be described in software. This software is made up out of separate instructions which are usually executed in sequence. The more complex the algorithm, the more instructions needed for the execution, hence the execution time increases.

Parallel execution can be used to compensate for the increase in execution time introduced by the sequential software. For parallel execution of regular, structured algorithms hardware solutions, like an FPGA, are ideal. For parallel computations the physical boundaries of FPGAs limit the amount of

parallelism. More complex algorithms can require more resources than available in the FPGA. If a full parallel implementation does not fit in the FPGAs *area*, pipelining<sup>1</sup> can be used to execute parts of the algorithm sequentially over time. The trade-off between resource usage and execution time is made by the developer.

The use of an FPGA can be seen as the trade-off between area and time as an FPGA can be configured specifically for the application it is used for. In the field of radio astronomy, like in other applications, many algorithms similar to image processing are seen. Image processing algorithms are very suitable for implementation on an FPGA due to the following properties:

- The algorithms are computationally complex

- · Computations can potentially be performed in parallel

- · Execution time can be guaranteed due to deterministic behaviour of the FPGA

As mentioned before image processing is essential in many applications, including astrophysics, surveillance, image compression and transmission, medical imaging and astronomy, just to name a few. Images in just one dimension are called signals. In two dimensions images are in the planar field and in three dimensions volumetric images are created, like Magnetic Resonance Imaging (MRI). These *images* can be coloured (*vector-valued functions*) or in gray-scale (*single-value functions*). Many types of imperfections, like noise and blur, in the acquired data often degrade the image. Before any feature extraction and further analysis is done, the images have to be first pre-processed.

In this research on energy efficiency of the HMC architecture, image denoising will be used. The technique used is the Median filter. Because this image processing algorithm, like most image processing algorithms, is highly complex and is executed on a fast amount of data, the combination of the HMC technology and FPGAs seems a logical choice.

The configuration of an FPGA can be done with a Hardware Description Language (HDL). Due to the possible parallelism in the hardware and the lower clock frequency of the FPGA in comparison to a CPU, in combination with HMC memory, a much lower energy consumption and execution time can possibly be obtained. To describe the hardware architecture, languages like VHSIC (Very High Speed Integrated Circuit) Hardware Description Language (VHDL) and Verilog are used. The manual work required is cumbersome.

Another framework is Open Computing Language (OpenCL). OpenCL is a framework for writing programs that execute across heterogeneous platforms consisting of CPUs, GPUs, DSPs, FPGAs and other processors or hardware accelerators. OpenCL specifies a programming language (based on C99) for programming these devices and Application Programming Interfaces (APIs) to control the platform and execute programs on the compute devices. OpenCL provides a standard interface for parallel computing using task-based and data-based parallelism.

<sup>&</sup>lt;sup>1</sup>A pipeline is a set of processing elements connected in series, where the output of one element is the input of the next. The elements of a pipeline are often executed in parallel or in time-sliced fashion. In that case of time-slicing, some amount of buffer storage is often inserted between the elements.

### 1.2 Problem statement

To evaluate the efficiency of the HMC, it is necessary to use a benchmark which can also run on other memory architectures, like GDDR5. The benchmark will provide the following metrics:

- Achievable throughput/latency (performance);

- Achievable average power consumption.

This research will attempt to answer the following questions:

- What is the average power consumption and performance of the HMC?

- How does the power consumption of the HMC compare to GDDR5 memory?

- · How does the performance of the HMC compare to GDDR5 memory?

- What are the bottlenecks and (how) can this be improved?

Realising a hardware solution for mathematically complex and memory intensive algorithms has potential advantages in terms of energy and speed. To analyse these advantages, a solution on an FPGA driven Hybrid Memory Cube architecture is realised and compared to a similar OpenCL software solution on a GPU. The means to answer the research questions are summarised into the following statements:

- How to realise a feasible image denoising implementation on an FPGA and HMC?

- · How to realise a feasible image denoising implementation on a GPU?

- How to realise a feasible benchmark to compare the GPU with the FPGA and HMC?

- Does the FPGA and HMC implementation have the potential to be more energy and performance efficient compared to the GPU solution?

### **1.3 Approach and outline**

Image denoising can be solved in different ways. To realise one solution that fits on both the FPGA/HMC and the GPU this solution must first be determined. This one solution must be implemented in Hardware Description Language (HDL) and in software. C $\lambda$ aSH is suitable for formulating complex mathematical problems and transforming this formulation into VHDL or Verilog HDL, but OpenCL is also supported for both the HMC and GPU architectures.

Part I - Background, contains the information on the different topics used in the research. Chapter 3 describes the different memory architectures of the memory modules used. Chapter 4 introduces the basic concepts regarding memory and CPU/GPU/FPGA benchmarking.

Part II - Realisation and results, shows the realised solutions and the results found.

Part III - Conclusions and future work are given.

Part I

# Background

# **Chapter 2**

# **Related Work**

Since the Hybrid Memory Cube is a fairly new memory technology, little has been studied on the impact on performance and energy efficiency. As an HMC I/O interface can achieve an external bandwidth up to 480 GB/s, using high-speed serial links, this comes at a cost. The static power of the off-chip links is largely dominating the total energy consumption of the HMC. As proposed by Ahn et al. [9] the use of dynamic power management for the off-chip links can result in an average energy consumption reduction of 51%.

Another study by Wang et al. [10] proposes to deactivate the least used HMCs and using erasure codes to compensate for the relatively long wake-up time of over  $2\mu s$ .

In 2014 Rosenfeld [11] defended his PhD thesis on the performance exploration of the Hybrid Memory Cube (HMC). For his research he used only simulations of the HMC architecture.

Finally, a paper by Zhu, et al. [12], discusses that GPUs are widely used to accelerate dataintensive applications. To improve the performance of data-intensive applications, higher GPU memory bandwidth is desirable. Traditional Double Data Rate Synchronous Graphics Random Access Memory (GDDR) memories achieve higher bandwidth by increasing frequency, which leads to excessive power consumption. Recently, a new memory technology called High Bandwidth Memory (HBM) based on 3D die-stacking technology has been used in the latest generation of GPUs developed by AMD, which can provide both high bandwidth and low power consumption with in-package stacked DRAM memory, offering  $> 3 \times$  the bandwidth per watt of GDDR5<sup>1</sup>. However, the capacity of integrated in-packaged stacked memory is limited (e.g. only 4GB for the state-of-the-art HBM-enabled GPU, AMD Radeon Fury X [13], [14]). In his paper, Zhu et al. implement two representative dataintensive applications, Convolutional Neural Network (CNN) and Breadth-First Search (BFS) on an HBM-enabled GPU to evaluate the improvement brought by the adoption of the HBM, and investigate techniques to fully unleash the benefits of such HBM-enabled GPU. Based on his evaluation results, Zhu et al. first propose a software pipeline to alleviate the capacity limitation of the HBM for CNN. They then designed two programming techniques to improve the utilisation of memory bandwidth for the BFS application. Experiment results demonstrate that the pipelined CNN training achieves a 1.63x speed-up on an HBM enabled GPU compared with the best high-performance GPU on the

<sup>&</sup>lt;sup>1</sup>Testing conducted by AMD engineering on the AMD Radeon R9 290X GPU vs. an HBM-based device. Data obtained through isolated direct measurement of GDDR5 and HBM power delivery rails at full memory utilisation. Power efficiency calculated as GB/s of bandwidth delivered per watt of power consumed. AMD Radeon R9 290X (10.66GB/s bandwidth per watt) and HBM-based device (35 + GB/s bandwidth per watt), AMD FX-8350, Gigabyte GA-990FX-UD5, 8GB DDR3-1866, Windows 8.1 x64 Professional, AMD Catalyst 15.20 Beta. HBM-1

market, and the two, combined optimisation techniques for the BFS algorithm makes it at most 24.5x (9.8x and 2.5x for each technique, respectively) faster than conventional implementations.

At the time of writing this report, the Hybrid Memory Cube technology is, as far as known, only used in two applications. The first implementation is the HMC produced by Micron (formerly Pico-Computing) [15], [16], see figure 2.1. This module is used for the experiments in order to get the performance and power measurements, which are discussed in the rest of this thesis.

Figure 2.1: HMC module: AC510 board

The second product known of using HMC, 3D stacking, technology is Intel's Knights Landing products [17], [18].

# **Chapter 3**

# Memory architectures

It was predicted by computer pioneers that computer systems and programmers would want unlimited amounts of fast memory. A *memory hierarchy* is an economical solution to that desire, which takes advantage of trade-offs and locality in the cost-performance of current memory technologies. Most programs do not access all code or data uniformly, as stated by the Principle of Locality. Locality occurs in space (*spatial locality*) and in time (*temporal locality*). Moreover, for a given technology and power budget smaller hardware can be made faster, led to hierarchies based on memories of different sizes and speeds.

### 3.1 Principle of Locality

When executing a program on a computer, this program tends to use instructions and read or write data with addresses near or equal to those used recently by that program. The Principle of Locality, also known as the *Locality of Reference*, is the phenomenon of the same value or related storage locations being frequently accessed. There are two types of locality:

Temporal locality: refers to the reuse of specific data and/or resources within relatively small time durations.

Figure 3.1: Temporal locality: Refer to block again

• Spatial locality: refers to the use of data elements within relatively close storage locations. Sequential locality, a special case of spatial locality, occurs when data elements are arranged and accessed linearly, e.g. traversing the elements in a one-dimensional array.

Figure 3.2: Spatial locality: Refer nearby block

For example, when exhibiting spatial locality of reference, a program accesses consecutive memory locations and during temporal locality of reference a program repeatedly accesses the same memory location during a short time period. Both forms of locality occur in the following code snippet:

```

sum = 0;

for (i = 0; i < n; i++)

sum += a[i];

return sum;

```

In the above code snippet, the variable i is referenced several times in the for loop where i is compared against n, to see if the loop is complete, and also incremented by one at the end of the loop. This shows *temporal* locality of reference in action since the CPU accesses i at different points in time over a short period of time.

This code snippet also exhibits *spatial* locality of reference. The loop itself adds the elements of array a to variable sum. Assuming C++ stores elements of array a into consecutive memory locations, then on each iteration the CPU accesses adjacent memory locations.

#### 3.2 RAM memory cell

SRAM is a type of semiconductor memory that uses *flip-flops* to store a single bit. SRAM exhibits data remanence (keeping its state after writing or reading from the cell) [19], but it is still volatile. Data is eventually lost when the memory is powered off.

The term *static* differentiates SRAM from DRAM which must be periodically refreshed. SRAM is faster but more expensive than DRAM, hence it is commonly used for CPU cache while DRAM is typically used for main memory. The advantages of SRAM over DRAM are lower power consumption, simplicity (no refresh circuitry is needed) and reliability. There are also some disadvantages: a higher price and lower capacity (amount of bits). The latter disadvantage is due to the design of an SRAM cell.

A typical SRAM cell is made up of six Metal-Oxide-Semiconductor Field-Effect Transistors (MOS-FETs). Each bit in an SRAM (see figure 3.3) is stored on four transistors (M1, M2, M3 and M4). This cell has two stable states which are used to denote 0 and 1. Two additional transistors (M5 and M6) are used to control the access to that cell during read and write operations.

Figure 3.3: Six transistor SRAM cell

A four transistor (4T) SRAM (see figure 3.4) is quite common in standalone devices, which is implemented in special processes with an extra layer of poly-silicon, allowing for very high-resistance pull-up resistors. The main disadvantage of using 4T SRAM is the increased static power due to the constant current flow through one of the pull-down transistors.

Figure 3.4: Four transistor SRAM cell

Generally, the fewer transistors needed per cell, the smaller each cell. Since the cost of processing a silicon wafer is relatively fixed, therefore using smaller cells and so packing more bits on a single wafer reduces the cost per bit. In figure 3.5a the layout of a 6T cell with dimensions  $5 \times P_{Metal}$  by  $2 \times P_{Metal}$  is shown. A 4T cell, as can be seen in figure 3.5b, has only a dimension of  $5 \times P_{Metal}$  by  $1.5 \times P_{Metal}$ .  $P_{Metal}$  denote the Metal Pitch used by the manufacturing process. The pitch is the centre to centre distance between the metals, having minimal width and minimal spacing.

Figure 3.5: SRAM cell layout: (a) A six transistor cell; (b) A four transistor cell

To access the memory cell (see figure 3.3) the *word line* (WL) gives access to transistors M5 and M6 which, in turn, control whether the cell (cross-coupled inverters) should be connected to the *bit lines* (BL). These bit lines are used for both write and read operations. Although it is not strictly necessary to have two bit lines, the two signals (BL and  $\overline{BL}$ ) are typically provided in order to improve noise margins.

Figure 3.6: One transistor, one capacitor DRAM cell

Opposed the the *static* SRAM, there is the *dynamic* DRAM cell (see figure 3.6). In this type of memory cell the data is stored in a separate capacitor within the IC. A charged capacitor denotes a 1 and discharged denotes a 0. However, a non-conducting transistor will always leak a small amount, discharging the capacitor, and the information in the memory cell eventually fades unless the capacitors charge is refreshed periodically, hence *Dynamic* in the name. The DRAM cell layout is even smaller as can be seen in figure 3.7

Figure 3.7: One transistor, one capacitor cell

The structural simplicity is DRAMs advantage. Compared to the four or even six transistors required in SRAM, just one transistor and one capacitor is required per bit in DRAM. This allows for very high densities, billions of these 1T cells can fit on a single chip. On the other hand, due to its *dynamic* nature, DRAM consumes relatively large amounts of power.

### 3.3 Principles of operation

Both types of RAM architectures have three main operations:

| SRAM    | DRAM         |  |

|---------|--------------|--|

| Standby | No Operation |  |

| Reading |              |  |

| Writing |              |  |

Table 3.1: RAM main operations

Due to the volatile nature of the DRAM architecture there is a fourth main operation, called Refresh

An SRAM cell has three different states: standby (the circuit is idle), reading (the data has been requested) or writing (updating the contents). SRAM operating in read mode and write modes should have *readability* and *write stability*, respectively. Assuming a six transistor implementation, the three different operations work as follows:

#### 3.3.1 SRAM - Standby

If the word line is not asserted, the transistors M5 and M6 disconnect the cell (M1, M2, M3 and M4) from the bit lines. The two cross-coupled inverters in the cell will continue to reinforce each other as long as they are connected to the supply  $V_{dd}$ .

#### 3.3.2 SRAM - Reading

In theory, reading only requires asserting the word line and *reading* the SRAM cell state by a single access transistor and bit line, e.g. M6/BL and  $M5/\overline{BL}$ . Nevertheless, bit lines are relatively long and have large parasitic capacitance. To speed up reading, a more complex process is used in practice:

- 1. Pre-charge both bit lines BL and  $\overline{BL}$ , that is, driving both lines to a threshold voltage midrange between a logic 1 and 0 by an external circuitry (not shown in figure 3.3).

- 2. Assert the word line WL to enable both transistors M5 and M6. This causes the BL voltage to either slightly rise (nMOS<sup>1</sup> transistor M3 is *OFF* and pMOS<sup>2</sup> transistor M4 is *ON*) or drop (M3 if *ON* and M4 *OFF*). Note that if BL rises,  $\overline{BL}$  drops and vice versa.

- 3. A sense amplifier will sense the voltage difference between BL and  $\overline{BL}$  to determine which line has the higher voltage and thus which logic value (0 or 1) is stored. A more sensitive sense amplifier speeds up the read operation.

#### 3.3.3 SRAM - Writing

To write to SRAM the following two steps are needed:

- 1. Apply the value to be written to the bit lines. If writing a 1, BL = 1 and  $\overline{BL} = 0$ .

- 2. Assert the word line WL to latch in the value to be stored.

This operation works, because the bit line input-drivers are designed to be much stronger than the relatively weak transistors in the cell itself so they can easily override the previous state of the cross-coupled inverters. In practice, the nMOS transistors M5 and M6 have to be stronger than either bottom nMOS (M1/M3) or top pMOS (M2/M4) transistors. This is easily obtained as pMOS transistors are much weaker than nMOS when same sized. Consequently when one transistor pair (e.g. M3/M4) is only slightly overridden by the write process, the opposite transistors pair (M1/M2) gate voltage is also changed. This means that the M1 and M2 transistors can be easier overridden, and so on. Thus, cross-coupled inverters magnify the writing process.

#### 3.3.4 DRAM - Refresh

Due to the charge leaking away out of the capacitor over time, this charge on the individual cells must be refreshed periodically. The frequency with which this refresh must occur depends on the silicon technology used to manufacture the memory chip and the design of the memory cell itself.

Each cell must be accessed and restored during a refresh interval. In most cases, refresh cycles involve restoring the charge along an entire row. Over the period of the entire interval, every cell in a row is accessed and restored. At the end of the interval, this process begins again.

Memory designers have a lot of freedom in designing and implementing memory refresh. One choice is to fit the refresh cycles between normal read and write cycles, another is to run refresh cycles on a fixed schedule, forcing the system to queue read/write operations when they conflict with the refresh requirements.

<sup>&</sup>lt;sup>1</sup>n-type MOSFET. The channel in the MOSFET contains electrons

<sup>&</sup>lt;sup>2</sup>p-type MOSFET. The channel in the MOSFET contains holes

Three common refresh options are briefly described below:

#### • RAS Only Refresh (ROR)<sup>3</sup>

Normally, DRAMs are refreshed one row at a time. The refresh cycles are distributed across the refresh interval so that all rows are refreshed within the required time period. Refreshing one row of DRAM cells using ROR, occurs in the following steps:

- The address of the row to be refreshed is applied at the address pins

- RAS is switched from *High* to *Low*. CAS<sup>4</sup> must remain *High*

- At the end of the, by specification, required amount of time, RAS is switch to High

#### CAS Before RAS (CBR)

Like  $\overline{RAS}$  Only Refresh, CBR refreshes one row at a time. Refreshing a row using  $\overline{CAS}$  Before  $\overline{RAS}$ , occur in the following steps:

- CAS is switched from *High* to *Low*

- $\overline{WE}^5$  is be switched to *High* (Read).

- After a specified required amount of time, RAS is switch to Low

- An internal counter determines the row to be refreshed

- After a specified required amount of time, TAS is switch to High

- After a specified required amount of time, RAS is switch to High

The main difference between CBR and ROR is the way for keeping track of the row address, respectively an internal counter or externally supplied.

#### • Self Refresh (SR)

Also known as **Sleep Mode** or **Auto Refresh**. SR is a unique method of refresh. It uses an on-chip oscillator to determine the refresh rate and, like the CBR method, an internal counter to keep track of the row address. This method is frequently used for battery-powered mobile applications or applications that uses a battery for backup power.

The timing required to initiate SR is a CBR cycle with  $\overline{RAS}$  active for a minimum amount of time as specified by the manufacturer. The length of time that a device can be left in *sleep mode* is limited by the power source used. To exit,  $\overline{RAS}$  and  $\overline{CAS}$  are asserted *High*.

#### 3.3.5 DRAM - Reading

To read from DRAM the following eight steps are needed:

- 1. Disconnect the sense amplifiers

- 2. Pre-charge the bit lines (differential pair) to exactly equal voltages that are midrange between logical *High* and *Low*. (E.g. 0.5V in the case of '0'= 0V and '1'= 1V)

- 3. Turn off the pre-charge circuitry. The parasitic capacitance of the "long" bit lines will maintain the charge for a brief moment

- 4. Assert a logic 1 at the word line WL of the desired row. This causes the transistor to conduct, enabling the transfer of charge to or from the capacitor. Since the capacitance of the bit line is typically much larger than the capacitance of the capacitor, the voltage on the bit line will slightly decrease or increase. (E.g. 0.45V='0' or 0.55V='1'). As the other bit line will stay at 0.5V there is a small difference between the two bit lines

<sup>&</sup>lt;sup>3</sup>RAS: Row Address Select

<sup>&</sup>lt;sup>4</sup>CAS: Column Address Select

<sup>&</sup>lt;sup>5</sup>WE: Write Enable

- 5. Reconnect the sense amplifiers to the bit lines. Due to the positive feedback from the crossconnected inverters in the sense amplifiers, one of the bit lines in the pair will be at the lowest voltage possible and the other will be at the maximum high voltage. At this point the row is *open* (the data is available)

- 6. All cells in the *open* row are now sensed simultaneously, and the sense amplifier outputs are latched. A column address selects which latch bit to connect to the external data bus. Reading different columns in the same (*open*) row can be performed without a row opening delay because, for the open row, all data has already been sensed and latched

- 7. While reading columns in an *open* row is occurring, current is flowing back up the bit-lines from the output of the sense amplifiers and recharging the cells. This reinforces ("*refreshes*") the charge in the cells by increasing the voltage in the capacitor (if it was charged to begin with), or by keeping it discharged (if it was empty).

Note that, due to the length of the bit lines, there is a fairly long propagation delay for the charge to be transferred back to the cells capacitor. This takes significant time past the end of sense amplification and thus overlaps with one or more column reads

8. When done with reading all the columns in the current *open* row, the word line is switched *Off* to disconnect the cell capacitors (the row is "*closed*") from the bit lines. The sense amplifier is switched *Off*, and the bit lines are pre-charged again (Next read starts from item 3).

#### 3.3.6 DRAM - Writing

To store data, a row is *opened* and a given column sense amplifier is temporarily forced to the desired *Low* or *High* voltage, thus causing the bit line to discharge or charge the cells capacitor to the desired value. Due to the sense amplifiers positive feedback configuration, it will hold a bit line at a stable voltage even after the forcing voltage is removed. During a write to a particular cell, all the columns in that row are sensed simultaneously (just as during reading), so although only a single columns cell capacitor charge is changed, the entire row is *refreshed*.

### 3.4 Dual In-Line Memory Module

Figure 3.8: Dual In-Line Memory Module memory subsystem organisation

Nowadays, CPU architectures have integrated memory controllers. The controller connects to the top of the memory subsystem through a *channel* (see figure 3.8). On the other end of the *channel*

are one or more DIMMs (see figure 3.9). The DIMM contains the actual DRAM chips that provide 4 or 8 bits of data per chip.

Figure 3.9: DIMM Channels

Current CPUs support triple or even quadruple channels. These multiple, independent channels increase data transfer rates due to the concurrent access of multiple DIMMs. Due to interleaving, latency is reduced when operating in triple-channel or in quad-channel mode. The memory controller distributes the data amongst the DIMMs in an alternating pattern, allowing the memory controller to access each DIMM for smaller bits of data instead of accessing a single DIMM for the entire chunk of data. This provides the memory controller more bandwidth for accessing the same amount of data across channels instead of traversing a single channel when it stores all data in one DIMM.

The Dual Inline of the DIMM refers to the DRAM chips on both sides of the module. The "group" of chips on one side of the DIMM called a *Rank* (see figure 3.10). Both *Ranks* on the DIMM can be accessed simultaneously by the memory controller. Within a single memory cycle 64 bits of data is accessed. These 64 bits may come from the 8 or 16 DRAM chips, depending on the data width of a single chip (see figure 3.11).

Figure 3.10: DIMM Ranks

Figure 3.11: DIMM Rank breakdown

DIMMs come in three rank configurations: single-rank, dual-rank or quad-rank configuration. Ranks are denoted as (xR). Together the DRAM chips grouped into a rank contain 64 bit of data. If a DIMM contains DRAM chips on just one side of the PCB, containing a single 64-bit chunk of data, it is referred to as a single-rank (1R) module. A dual rank (2R) module contains at least two 64 bit chunks of data, one chunk on each side of the PCB. Quad ranked DIMMs (4R) contains four 64 bit chunks,

two chunks on each side. To increase capacity, combine the ranks with the largest DRAM chips. A quad-ranked DIMM with 4Gb chips equals 16GB DIMM ( $^{4Gb\times8 \text{ chips}\times4 \text{ ranks}}/_{8 \text{ bits}}$ ).

Figure 3.12: DIMM Chip

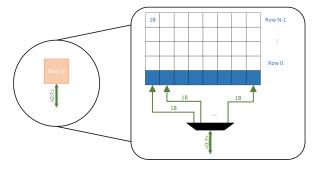

Finally, the DRAM chip is made up of several *banks* (see figure 3.12). These banks are independent memory arrays which are organised in rows and columns (see figure 3.13).

Figure 3.13: DIMM Bank Rows and Columns

For example, a DRAM chip with 13 address bits for *Row* selection, 10 address bits for *Column* selection, 8 *Banks* and 8 bits per addressable location, this chip has a total density of  $2^{Rows} \cdot 2^{Cols} \cdot Banks \cdot Bits_{Addressable} = 2^{13} \cdot 2^{10} \cdot 8 \cdot 8 = 512$ Mbit (64M x 8 bits).

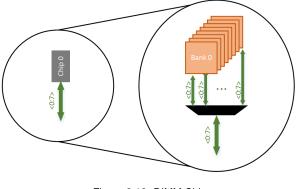

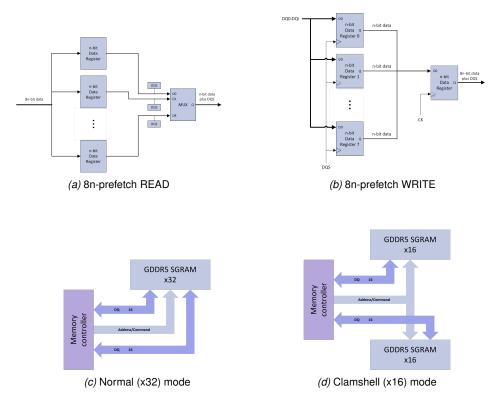

### 3.5 Double Data Rate type 5 Synchronous Graphics Random Access Memory

GDDR5 is the most commonly used type of Synchronous Graphics Random Access Memory (SGRAM) at the moment of writing this thesis. This type of memory has a high *bandwidth* (Double Data Rate SDRAM (DDR)) interface for use in HPC and graphics cards.

This SGRAM is a specialised form of Synchronous Dynamic Random Access Memory (SDRAM), based on DDR3 SDRAM. Functions like *bit masking*, i.e. writing a specified set of bits without affecting other bits of the same address, and *block write*, i.e. filling a block of memory with one single value. Although SGRAM is single ported, it can open two memory pages at once, simulating the dual ported nature of other video RAM technology.

GDDR5 uses a DDR3 interface and an 8n-prefetch architecture (see figures 3.14a and 3.14b) to achieve high performance operations. The prefetch buffer depth (8n) can also be thought of as the ratio between the core memory frequency and the Input/Output (I/O) frequency. In an 8n-prefetch architecture, the I/Os will operate  $8 \times$  faster than the memory core (each memory access results in a burst of 8 datawords on the I/Os). Thus a 200MHz memory core is combined with I/Os that each operate eight times faster (1600 megabits per second). If the memory has 16 I/Os, the total read bandwidth would be  $200MHz \times 8datawords/access \times 16I/Os = 25.6Gbit/s$ , or 3.2GB/s. At Power-up, the device is configured in x32 mode or in x16 clamshell mode, where the 32-bit I/O, instead of being connected to one IC, is split between two ICs (one on each side of the PCB), allowing for a doubling of the memory capacity.

Just by adding additional DIMMs to the memory channels is the traditional way of increasing memory density in PC and server applications. However, this dual-rank configuration can lead to performance degradation resulting from the dual-load signal topology (The databus is share by both ranks). GDDR5 uses a single-loaded or Point-To-Point (P2P) data bus for the best performance.

GDDR5 devices are always directly soldered on the PCB and are not mounted on a DIMM. In *x16 mode*, the data bus is split into two 16-bit wide buses that are routed separately to each device (see figure 3.14d). The *Address* and *Command* pins are shared between the two devices to preserve the total I/O pin count at the controller. However, this Point-To-Two-Point (P22P) topology does not decrease system performance because of the lower data rates of the address or command bus.

Figure 3.14: Double Data Rate type 5 Synchronous Graphics Random Access Memory (GDDR5)

GDDR5 operates with two different clock types. A differential Command Clock (CK) as a reference for address and command inputs, and a forwarded differential Write Clock (WCK) as a reference for

data reads and writes, that runs at twice the CK frequency. A Delay Locked Loop (DLL) circuit is driven from the clock inputs and output timing for read operations is synchronised to the input clock. Being more precise, the GDDR5 SGRAM uses a total of three clocks:

- 1. Two write clocks associated with two bytes: WCK01 and WCK23

- 2. One Command Clock (CK)

Over the GDDR5 interface 64-bits of data (two 32-bit wide data words) per WCK can be transferred. Corresponding to the 8n-prefetch, a single write or read access consists of a 256-bit wide two CK clock cycle data transfer at the internal memory core and eight corresponding 32-bit wide one-half WCK clock cycle data transfers at the I/O pins.

Taking a GDDR5 with 5 Gbit/s data rate per pin as an example, the CK runs with 1.25 GHz and both WCK clocks at 2.5 GHz. The CK and WCKs are phase aligned during the initialisation and training sequence. This alignment allows read and write access with minimum latency.

### 3.6 Hybrid Memory Cube

As written in [20] the Hybrid Memory Cube combines several stacked DRAM dies on top of a Complementary Metal Oxide Semiconductor (CMOS) logic layer forming a so called **cube**. The combination of both DRAM technology and CMOS technology dies makes this a **hybrid** chip, hence the name Hybrid Memory Cube. The dies in the 3D stack are connected by means of a dense interconnect mesh of Through Silicon Vias (TSVs), which are metal connections extending vertically through the entire stack (see figures 3.15 and 3.16).

Figure 3.15: Cross Sectional Photo of HMC Die Stack Including TSV Detail (Inset) [1]

Figure 3.16: HMC Layers [2]

Unlike conventional DDR3 DIMM which has the electrical connection through the pressure of the pins in the connector, the TSVs form a permanent connection between all the layers in the stack. The TSV connections provide a very short (less then a *mm* up to a few *mm*) with less capacitance than the long PCB trace buses which can extent to many *cm*, hence data can be transmitted at a reasonable high data rate through the HMC stack without the use of power hungry and expensive I/O drivers [21].

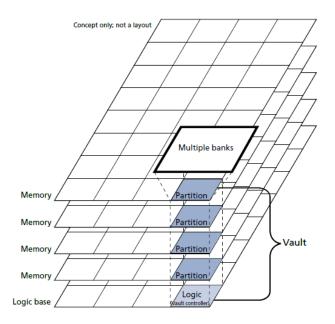

Within each HMC [3], memory is vertically organised. A partition of each memory die is combined into a vault (see figure 3.17). Each vault is operationally and functionally independent. The base of a vault contains a vault controller located in the CMOS die. The role of the vault controller is like a traditional memory controller in that it sends DRAM commands to the memory partitions in the vault and keeps track of the memory timing constraints. The communication is through the TSVs. A vault is more or less equivalent to a conventional DDR3 channel. However, unlike traditional DDR3 memory, the TSV connections are much shorter than the conventional bus traces on a motherboard and therefore have much better electrical properties. An illustration of the architecture can be seen in figure 3.17.

Figure 3.17: Example HMC Organisation [3]

The vault controller, by definition, may have a queue to buffer references inside that vaults memory. The execution of the references within the queue may be based on need rather than the order of arrival. Therefore the response from the vault to the external serial I/O links will be out of order. When no queue is implemented and two successive packets have to be executed on the same bank, the vault controller must wait for the bank to finish its operation, before the next packet can be executed, potentially blocking packet executions to other banks inside that vault. The queue can potentially optimise the memory bus usage.

Requests from a single external serial link to the same vault/bank address will be executed in order of arrival. Requests from different external serial links to the same vault/bank address are not guaranteed to be executed in order. Therefore the requests must be managed by the host controller (e.g. an FPGA or CPU).

The functions managed by the logic base of the HMC are:

- · All HMC I/O, implemented as multiple serialised, full duplex links

- Memory control for each vault; Data routing and buffering between I/O links and vaults

- · Consolidated functions removed from the memory die to the controller

- Mode and configuration registers

- BIST for the memory and logic layer

- Test access port compliant to JTAG IEEE 1149.1-2001, 1149.6

- Some spare resources enabling field recovery from some internal hard faults.

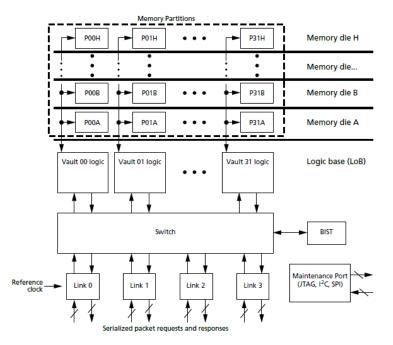

A block diagram example for an implementation of a 4-link HMC configuration is shown in figure 3.18.

Figure 3.18: HMC Block Diagram Example Implementation [3]

Commands and data are transmitted in both directions across the link using a packet based protocol where the packets consist of 128-bit Flow Units (FLITs). These FLITs are serialised, transmitted across the physical lanes of the link, then re-assembled at the receiving end of the link. Three conceptual layers handle packet transfers:

- The physical layer handles serialisation, transmission, and de-serialisation

- The link layer provides the low-level handling of the packets at each end of the link.

- The transaction layer provides the definition of the packets, the fields within the packets, and the packet verification and retry functions of the link.

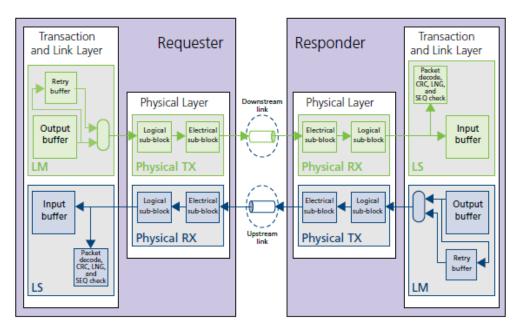

Two logical blocks exist within the link layer and transaction layer (see figure 3.19):

- The Link Master (LM), is the logical source of the link where the packets are generated and the transmission of the FLITs is initiated.

- The Link Slave (LS), is the logical destination of the link where the FLITs of the packets are received, parsed, evaluated, and then forwarded internally.

The nomenclature below is used throughout this report to distinguish the direction of transmission between devices on opposite ends of a link. These terms are applicable to both host-to-cube and cube-to-cube configurations.

**Requester:** Represents either a host processor or an HMC link configured as a pass-through link. A requester transmits packets downstream to the responder.

**Responder:** Represents an HMC link configured as a host link (See figure 3.20 through figure 3.23). A responder transmits packets upstream to the requester.

Figure 3.19: Link Data Transmission Example Implementation [3]

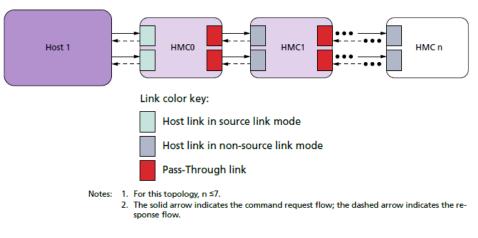

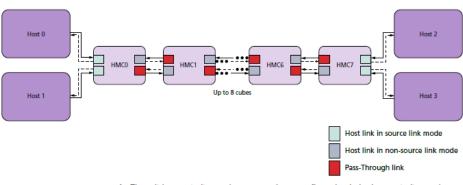

Multiple HMC devices may be chained together to increase the total memory capacity available to a host. A network of up to eight HMC devices and 4 host source links is supported, as will be explained in the next paragraphs. Each HMC in the network is identified through the value in its CUB field, located within the request packet header. The host processor must load routing configuration information into each HMC. This routing information enables each HMC to use the CUB field to route request packets to their destination.

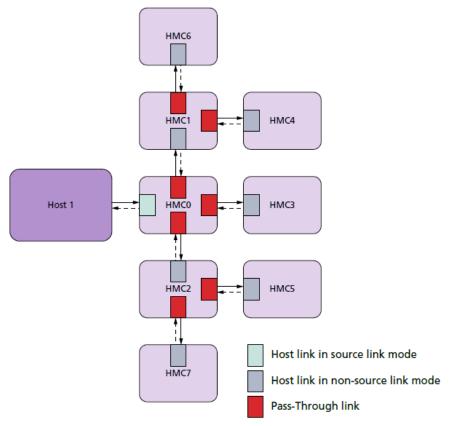

Each HMC link in the cube network is configured as either a **host link** or a **pass-through link**, depending upon its position within the topology. See figure 3.20 through figure 3.23 for illustrations.

A **host link** uses its Link Slave to receive request packets and its Link Master to transmit response packets. After receiving a request packet, the host link will either propagate the packet to its own internal vault destination (if the value in the CUB field matches its programmed cube ID) or forward it towards its destination in another HMC via a link configured as a pass-through link. In the case of a malformed request packet whereby the CUB field of the packet does not indicate an existing CUBE ID number in the chain, the request will not be executed, and a response will be returned (if not posted) indicating an error.

A **pass-through link** uses its Link Master to transmit the request packet towards its destination cube, and its Link Slave to receive response packets destined for the host processor.

Figure 3.20: Example of a Chained Topology [3]

Note: 1. The solid arrow indicates the command request flow; the dashed arrow indicates the response flow.

Figure 3.21: Example of a Star Topology [3]

Note: 1. The solid arrow indicates the command request flow; the dashed arrow indicates the response flow.

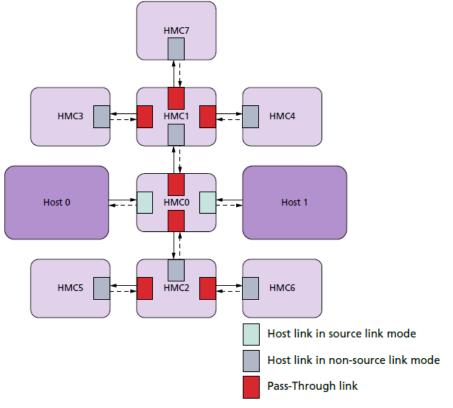

Figure 3.22: Example of a Multi-Host Topology [3]

Note: 1. The solid arrow indicates the command request flow; the dashed arrow indicates the response flow.

An HMC link connected directly to the host processor must be configured as a host link in source mode. The Link Slave of the host link in source mode has the responsibility to generate and insert a unique value into the Source Link Identifier (SLID) field within the tail of each request packet. The unique SLID value is used to identify the source link for response routing. The SLID value does not serve any function within the request packet other than to traverse the cube network to its destination vault where it is then inserted into the header of the corresponding response packet. The host processor must load routing configuration information into each HMC. This routing information enables each HMC to use the SLID value to route response packets to their destination. Only a host link in source mode will generate an SLID for each request packet. On the opposite side of a pass-through link is a host link that is not in source mode. This host link operates with the same characteristics as the host link in source mode for response routing purposes only. The SLID value generated by the host link in source mode for response routing purposes only. The SLID fields within the request packet tail and the response packet header are considered Don't Care" by the host processor. See figure 3.20 through figure 3.23 for illustrations for supported multi-cube topologies.

### 3.6.1 HMC Bandwidth and Parallelism

As mentioned in the previous section, a high bandwidth connection within each vault is available by using the TSVs to interconnect the 3D stack of dies. The combination of the number of TSVs (the density per cube can be in the thousands) and the high frequency at which data can be transferred provides a high bandwidth.

Because of the number of independent vaults in an HMC, each build up out of one or more banks (as in DDR3 systems), a high level of parallelism inside the HMC is achieved. Since each vault is roughly equivalent to a DDR3 channel and with 16 or more vaults per HMC, a single HMC can support an order of magnitude more parallelism within a single package. Furthermore, by stacking more dies inside a device, a greater number of banks per package can be achieved, which in turn is beneficial to parallelism.

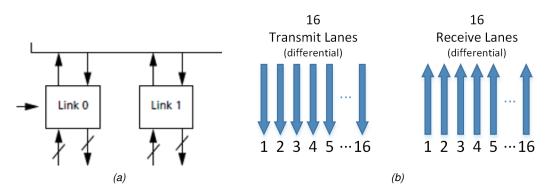

The overall build up of the HMC, depending on the cubes configuration, can deliver an aggregate bandwidth of up to 480GB/s (see figure 3.24).

Figure 3.24: HMC implementation: (a) 2 Links; (b) 32 Lanes (Full width link)

The available total bandwidth on an 8 Links, Full width HMC implementation is calculated as follows:

- 15 Gb/s per Lane

- 32 Lanes = 4 Bytes

- 8 Links / Cube = 480 GB/s / Cube

For the AC-510 [16] UltraScale-based SuperProcessor with HMC, providing 2 half width links, the total available bandwidth is equal to  $15Gb/s \times 2 \times 2 = 60GB/s$

### 3.6.2 GDDR5 versus HMC

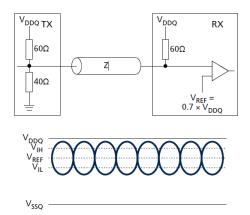

To reduce the power consumption of GDDR5 many techniques have been employed. A POD signalling scheme, combined with an On-Die Termination (ODT) resistor [22] will only consume static power when driving *LOW* as can be seen in figure 3.25.

Lowering the supply voltage ( $\approx 1.5V$ ) of the memory, Dynamic Voltage/Frequency Scaling (DVFS) and the usage of independent ODT strength control of the command, address and data lines, are some of the other techniques used in GDDR5 memory. The DVFS [23] technique reduces power by adapting the voltage and/or the frequency of the memory interface while satisfying the throughput requirements of the application. However, this reduction in power results in the degradation of the throughput.

Using all these techniques, to get a maximum throughput or bandwidth of 6.0Gbps a relatively high clock frequency is needed. For example, the memory clock of the AMD Radeon(tm) HD 7970 GHz edition GPU is equal to 1500MHz.

Figure 3.25: GDDR5 - Pseudo Open Drain (POD)