# The Creation of a Flexible, Functional Simulation Generator for the Montium Tile Processor

Master's Thesis by

# L. Ordelmans

July 2, 2007

graduation committee: Prof. Dr. Ir. G.J.M. Smit Dr. Ir. A.B.J. Kokkeler Dr. Ir. L.T. Smit Ir. K.L. Hofstra

Computer Architecture for Embedded Systems Department of Computer Science University of Twente

# Voorwoord

Dit verslag beschrijft het werk dat ik heb uitgevoerd ter afronding van mijn Master opleiding Computer Science aan de Universiteit Twente. Het beschrijft het ontwerp en de implementatie van een simulator voor de Montium, een herconfigureerbare chip, waarbij gebruik gemaakt wordt van code generatie.

Ik heb veel plezier gehad tijdens het werken aan deze opdracht, met name toen de eerste delen begonnen te werken en ik de principes onder de knie kreeg.

Toen ik begon met afstuderen zou ik eigenlijk een andere opdracht uitvoeren, het was de bedoeling dat ik een DSP algorithme zou gaan mappen op de zojuist genoemde chip. Vrij snel ontdekte ik echter dat deze opdracht mij helemaal niet lag, en na een tijd getwijfeld te hebben besloot ik hiermee bij mijn begeleider aan te kloppen, en had ik mij er reeds bij neergelegd dat ik opnieuw op zoek moest naar een afstudeerplek. Tot mijn aangename verassing bleek het team van Recore Systems best bereid was om samen met mij een nieuwe opdracht uit te zoeken. Na ongeveer een goed deel van de middag ideeën te hebben uitgewisseld, ben ik mij vervolgens gaan verdiepen in de nieuwe opdracht, waarvan u het eindverslag nu aan het lezen bent. Ik wil dan ook graag de mensen van Recore Systems bedanken voor het mogelijk maken van deze opdracht en alle ondersteuning tijdens mijn afstudeer periode. Met name Lodewijk, Klaas, Paul en Gerard bij wie ik terecht kon met vragen over mijn opdracht danwel over de Montium, maar ook de rest van het team voor de gezellige tijd. Tevens wil ik natuurlijk mijn begeleiders van de UT, Gerard Smit en André Kokkeler bedanken voor hun inbreng tijdens de maandelijkse voortgangsgesprekken.

Ter afsluiting wil ik nog bedanken mijn moeder en Inge, mijn vriendin, voor hun steun tijdens mijn toch best lange studieweg van ruim 6 jaar.

Enschede, Juni 2007 Luke Ordelmans

#### Abstract

Simulation is an important tool for (DSP) software developers. In order to test, debug, analyze and improve algorithms the developer needs to be able to see how his work gets executed by the target system. This thesis describes the design and implementation of a functional simulator created for the Montium Tile Processor, a domain specific reconfigurable accelerator, that makes use of code-generation to achieve the speed of a binary compiled simulator but preserves the flexibility of an interpretive one. The simulation generator uses a binary configuration compiled for the Montium TP together with some (optional) design parameters of the specific Montium instance to generate program source code that is compilable on a general purpose desktop computer. By implementing this simulation generator in Java SE 6, the program will be portable between different machines and operating systems. Another benefit from this choice is that it becomes possible for the generated simulation to be compiled and instantiated internally (without leaving the generator to start a external compiler) and instantly, totally invisible for the end-user, effectively making the generator itself work as a flexible and fast simulator. In order to make interaction with the simulator as easy as possible, a graphical user interface was build around it. This gives the developer the possibility to edit his source code, compile it and simulate it all in a single, easy to use, environment.

Benchmarks show that this new simulation approach is a factor of 10 times faster than the existing interpretive simulator, while providing more flexibility in terms of Montium design parameters (directly available to the enduser). Benchmarks also show that even though using C instead of Java as the target language for code-generation, will result in somewhat faster simulations, the difference in performance isn't big enough to provide a good reason to abandon the portability and extendability benefits provided by using Java.

# Contents

| 1        | Intr           | roduction                            |   |  |

|----------|----------------|--------------------------------------|---|--|

|          | 1.1            | The Montium Tile Processor 13        | 3 |  |

|          | 1.2            | Assignment                           | 8 |  |

|          | 1.3            | Structure of this report             | 9 |  |

| <b>2</b> | $\mathbf{Rel}$ | ated Work 21                         | 1 |  |

|          | 2.1            | Simulation techniques                | 1 |  |

|          |                | 2.1.1 (V)HDL simulators              | 1 |  |

|          |                | 2.1.2 Instruction level simulators   | 2 |  |

|          |                | 2.1.3 Binary compiled simulation     | 2 |  |

|          | 2.2            | The 'Simsation' simulator            | 3 |  |

|          | 2.3            | The Montium TP Simulation Generator  | 3 |  |

| 3        | Des            | ign 25                               | 5 |  |

|          | 3.1            | Benefits of a functional simulator   |   |  |

|          | 3.2            | Simulation generation                | 5 |  |

|          | 3.3            | Target Language                      | 7 |  |

|          | 3.4            | Required functionality (API)         | 8 |  |

|          | 3.5            | Software Design                      |   |  |

|          | 3.6            | Flexibility                          | 9 |  |

|          |                | 3.6.1 Montium design parameters      | 9 |  |

|          |                | 3.6.2 Functional behaviour           | 9 |  |

|          | 3.7            | Initial State and end-results        | 0 |  |

|          | 3.8            | The optimization steps               |   |  |

|          |                | 3.8.1 Straight forward optimizations |   |  |

|          |                | 3.8.2 Look-back optimizations        |   |  |

|          |                | 3.8.3 Look-ahead optimizations       |   |  |

| 4        | Imr            | lementation 33                       | 3 |  |

| _        | 4.1            | Configuration parser                 |   |  |

|          | 4.2            | Sequencer                            |   |  |

|          |                | 4.2.1 Cycle code generation          |   |  |

|          |                | 4.2.2 State Machine                  |   |  |

|          |     | 4.2.3 Switch/case bottleneck issue                                                   | 36              |

|----------|-----|--------------------------------------------------------------------------------------|-----------------|

|          | 4.3 | Code generation                                                                      | 37              |

|          |     | 4.3.1 Decoders                                                                       | 38              |

|          |     | 4.3.2 Global and Local Interconnections                                              | 39              |

|          |     | 4.3.3 Streaming IO                                                                   | 40              |

|          |     | 4.3.4 Register Files                                                                 | 41              |

|          |     | 4.3.5 Address Generation Units                                                       | 42              |

|          |     | 4.3.6 Code generation visitor for the ALUs                                           | 43              |

|          | 4.4 | Code generation summarized                                                           | 48              |

|          | 4.5 | Code Compilation process                                                             | 49              |

|          |     | 4.5.1 Compilation of Java code                                                       | 49              |

|          |     | 4.5.2 Compilation of C code                                                          | 49              |

|          | 4.6 | Backwards stepping via snapshots                                                     | 50              |

|          | 4.7 | Optimizations                                                                        | 50              |

|          |     | 4.7.1 Data dependencies (external)                                                   | 51              |

|          |     | 4.7.2 Data dependencies (internal)                                                   | 52              |

|          |     | 4.7.3 Selective code generation                                                      | 52              |

|          |     | 4.7.4 Hotspot or Loop detection                                                      | 54              |

|          |     |                                                                                      |                 |

| <b>5</b> | Con | nmunication and Configuration Unit                                                   | 57              |

|          | 5.1 | The Hydra CCU                                                                        | 57              |

|          | 5.2 | Simulating the CCU                                                                   | 59              |

| 6        | Rec | onfigurable fabric of the Annabelle                                                  | 63              |

|          |     |                                                                                      |                 |

| 7        | Res |                                                                                      | 67              |

|          | 7.1 | Flexibility                                                                          | 67              |

|          |     | 7.1.1 Runtime flexibility                                                            | 67              |

|          |     | 7.1.2 Compile time flexibility                                                       | 68              |

|          | 7.2 | Simulation Performance                                                               | 68              |

|          |     | 7.2.1 Motivation and Overview                                                        | 68              |

|          |     | 7.2.2 Benchmark setup                                                                | 69              |

|          |     | 7.2.3 Performance Java versus C Output                                               | 70              |

|          |     | 7.2.4 Performance compared to 'Simsation' without CCU .                              | 75              |

|          |     | 7.2.5 Performance compared to 'Simsation' with CCU                                   | 76              |

|          |     | 7.2.6 Improvements achieved by optimizations                                         | 77              |

|          |     | 7.2.7 Running multiple simulations in parallel                                       | 80              |

|          |     |                                                                                      |                 |

| 8        | Cor | clusion and Recommendations                                                          | 81              |

| 8        |     | clusion and Recommendations                                                          | <b>81</b><br>81 |

| 8        | 8.1 | Conclusion                                                                           | 81              |

| 8        |     | Conclusion                                                                           | 81<br>81        |

| 8        | 8.1 | ConclusionRecommendations for Future Work8.2.1Simulation of a complete Annabelle SoC | 81<br>81<br>82  |

| 8        | 8.1 | Conclusion                                                                           | 81<br>81        |

|              | 8.2.4                     | Generation of Java byte-code                                                               | 83 |

|--------------|---------------------------|--------------------------------------------------------------------------------------------|----|

|              | 8.2.5                     | More integration with other tools                                                          | 84 |

|              | 8.2.6                     | Create a complete test-suite                                                               | 84 |

|              | 8.2.7                     | Create a framework to integrate the simulation gener-<br>ator with a Scripting environment | 84 |

| A            | The Simul                 | ator API                                                                                   | 87 |

| в            | Montium Design Parameters |                                                                                            |    |

| $\mathbf{C}$ | Simulation Datastructure  |                                                                                            |    |

| D            | FU Helpe                  | r Methods                                                                                  | 95 |

| $\mathbf{E}$ | Source use                | ed for Benchmarking the CCU                                                                | 97 |

# List of Figures

| 1.1  | Montium Tile Processor and CCU                                     | 14 |

|------|--------------------------------------------------------------------|----|

| 1.2  | Simplified schematic of the Arithmetic and Logic Unit              | 15 |

| 1.3  | Register File inside an ALU                                        | 15 |

| 1.4  | Control of an Montium ALU                                          | 17 |

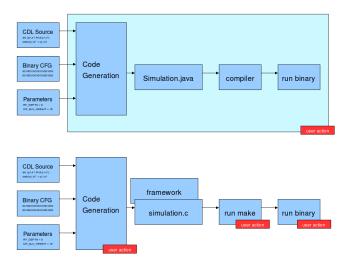

| 3.1  | Code Generation schematic                                          | 26 |

| 3.2  | The Simulation Generation process using Java (above) or C $$ .     | 27 |

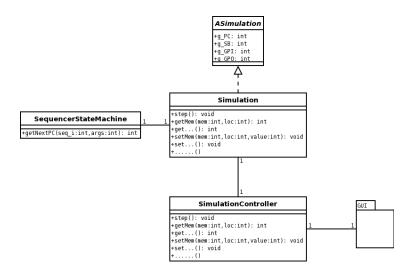

| 3.3  | Simplified UML overview of the Simulator design                    | 29 |

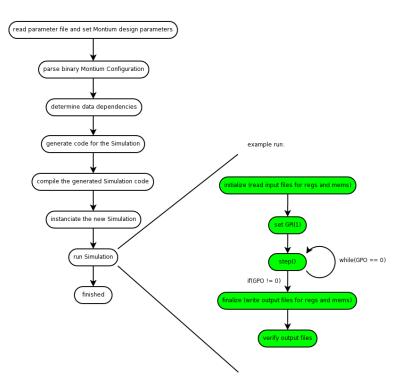

| 4.1  | Simulation Generator overview                                      | 33 |

| 4.2  | Register File CR (4 positions)                                     | 34 |

| 4.3  | Register File CR (8 positions)                                     | 35 |

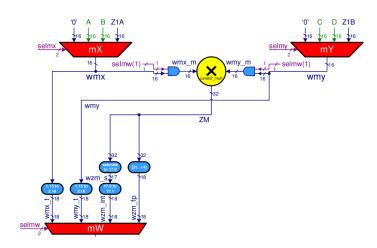

| 4.4  | Small piece of the ALU datapath                                    | 44 |

| 4.5  | Functional Units in the ALU datapath                               | 46 |

| 4.6  | Transitions from type 1 instructions                               | 51 |

| 4.7  | Transition from type 2 instructions                                | 51 |

| 4.8  | Transition from type 3 instruction                                 | 51 |

| 4.9  | Selective code generation for RF read addresses                    | 53 |

| 4.10 | Selective code generation for an ALU                               | 54 |

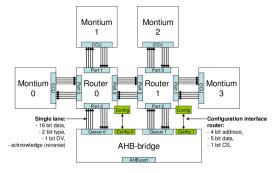

| 5.1  | the Montium Tile connected to a NoC router                         | 57 |

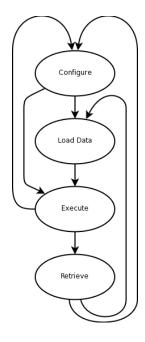

| 5.2  | State diagram for the CCU[1]                                       | 58 |

| 6.1  | Reconfigurable fabric of the Annabelle chip $\ldots \ldots \ldots$ | 63 |

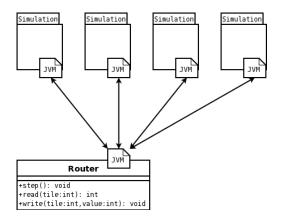

| 6.2  | UML overview of approach 1                                         | 64 |

| 6.3  | UML overview of approach 2                                         | 65 |

| 6.4  | Graphical representation of a router configuration                 | 66 |

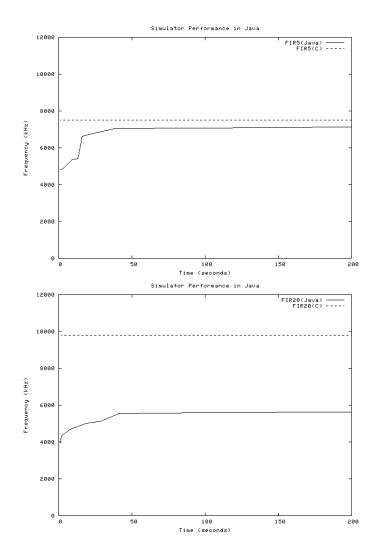

| 7.1  | Simulation speed for FIR algorithms                                | 71 |

| 7.2  | Simulation speed for FFT algorithms                                | 72 |

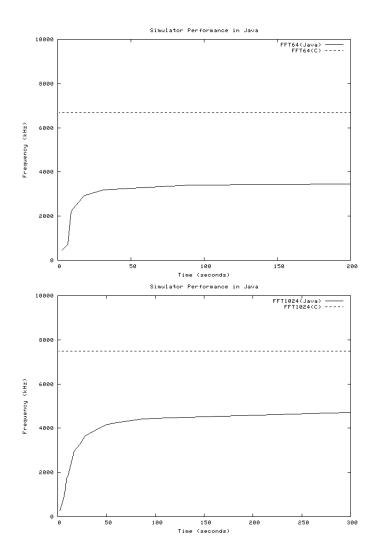

| 7.3  | Simulation speed for the 1920-points FFT with input-scaling        | 73 |

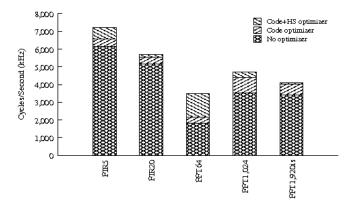

| 7.4  | Optimization Effects on Performance (non-streaming)                | 79 |

| 8.1  | Block diagram of the Annabelle chip $\ . \ . \ . \ . \ . \ .$      | 82 |

# List of Listings

| 4.1  | Structural description of a Register File configuration register  | 35 |  |

|------|-------------------------------------------------------------------|----|--|

| 4.2  | Main simulator loop - the step() method                           | 36 |  |

| 4.3  | Generated switch/case tree                                        | 37 |  |

| 4.4  | Example generated code for individual interconnects, trans-       |    |  |

|      | fers a value from memory 9 to register A of the first processing  |    |  |

|      | part                                                              | 39 |  |

| 4.5  | Example generated code for combined interconnects                 | 39 |  |

| 4.6  | Example generated code for Streaming IO input                     | 41 |  |

| 4.7  | Example generated code for Streaming IO output                    | 41 |  |

| 4.8  | Example generated code for a Register File                        | 41 |  |

| 4.9  | Example generated AGU code                                        | 42 |  |

| 4.10 | Code describing the data<br>path fragment shown in Figure $4.4$ . | 44 |  |

| 4.11 | Example generated ALU code 1                                      | 46 |  |

| 4.12 | Example generated ALU code 2                                      | 46 |  |

| 4.13 | Example generated ALU code 3                                      | 46 |  |

| 4.14 | Example generated code for an entire cycle                        | 48 |  |

| 6.1  | Simulating the reconfigurable part of the Annabelle               | 66 |  |

| 6.2  | Example router configuration file                                 | 66 |  |

| 7.1  | Example parametric datapath                                       | 68 |  |

| 7.2  | Benchmark Loop                                                    | 69 |  |

| 7.3  | Benchmark Loop for Simsation                                      | 75 |  |

| 7.4  | Benchmark Loop for Simsation (CCU)                                | 76 |  |

| A.1  | Simulation API                                                    | 87 |  |

| C.1  | Basic Simulation Datastructure                                    | 93 |  |

| D.1  | FU Helper Methods                                                 | 95 |  |

| E.1  | CDL Source used for Benchmarking the CCU                          | 97 |  |

# Glossary

| AGU                  | Address Generation Unit                     |

|----------------------|---------------------------------------------|

| ALU                  | Arithmetic and Logic Unit                   |

| API                  | Application Programming Interface           |

| CCU                  | Communication and Configuration Unit        |

| DSP                  | Digital Signal Processing                   |

| DSRA                 | Domain Specific Reconfigurable Accelerator  |

| $\operatorname{FFT}$ | Fast Fourier Transformation                 |

| FIR                  | Finite Impulse Response                     |

| GPI                  | General Purpose Input                       |

| GPO                  | General Purpose Output                      |

| GUI                  | Graphical User Interface                    |

| ISA                  | Instruction Set Architecture                |

| MAC                  | Multiply Accumulate                         |

| Montium TP           | Montium Tile Processor                      |

| NoC                  | Network-on-Chip                             |

| $\mathbf{PC}$        | Program Counter: the address indicating     |

|                      | where a processor is in its instruction se- |

|                      | quence                                      |

| PPA                  | Processing Part Array                       |

| SB                   | Status Bits                                 |

| SIO                  | Streaming Input and Output                  |

| $\operatorname{SoC}$ | System-on-Chip                              |

| UML                  | Unified Modeling Language                   |

| VHDL                 | Very High Speed Integrated Circuit Hardware |

|                      | Description Language                        |

|                      |                                             |

# Chapter 1

# Introduction

### 1.1 The Montium Tile Processor

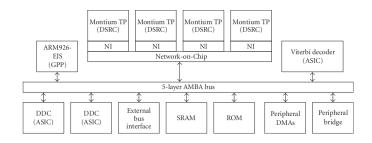

Battery powered mobile devices nowadays tend to be given more and more functionality. To support this functionality the demand for more processing power and flexibility increases while energy consumption needs to be kept at a minimum. For addressing this problem the Chameleon System-on-Chip template was designed. In the Chameleon SoC, heterogeneous processing tiles are connected via a network-on-chip. The essence of this idea is that the processing of a task is performed by a tile that has the best support for that specific kind of task[1]. The Montium Tile processor[1][2] is a domain specific reconfigurable accelerator, DSRA, for a Chameleon System-on-Chip. It is less flexible than a general purpose processor, but more efficient in doing the specific tasks it is targeted for. The target application domain the Montium TP was designed for is the domain of 16-bit DSP algorithms like Finite Impulse Response (FIR-) filters and Fast Fourier Transformations (FFTs). The Montium TP is capable of doing multiple calculations in a single clock-cycle by using 5 rich ALUs, specifically designed for DSP algorithms, in parallel. Every one of these ALUs can do some logic functions, a Multiply-Accumulate (MAC) and a butterfly operation all together in a single clock-cycle. A Montium Tile consist of a Montium Tile processor and a Communication and Configuration Unit (CCU) connecting the Tile within the SoC. Within the Smart chips for Smart Surroundings (4S) project [4] the Annabelle prototype chip was developed. The Annabelle consist of, among other things, an ARM926 general purpose processor with a 5-layer AMBA bus, 4 Montium Tile Processors, a Viterbi decoder, two digital down converters (DDCs), memory and external connections[3].

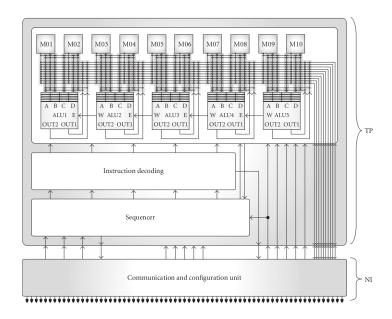

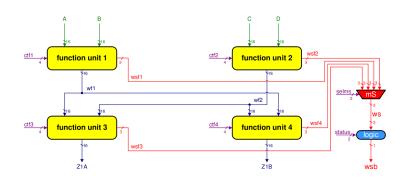

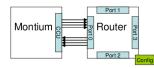

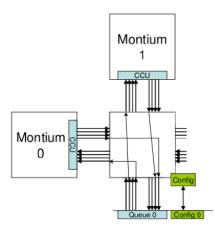

Figure 1.1: Montium Tile Processor and CCU

Figure 1.1 show the Montium Tile Processor together with the Communication and Configuration Unit. An single ALU together with its register files and two memories is called a Processing Part (PP). The five ALUs together are referred to as the Processing Part Array (PPA).

#### The Montium ALUs

Figure 1.2 shows a simplified schematic of the Montium's Arithmetic and Logic Unit (ALU). To accommodate many DSP operations that work on more than two operands, e.g. a Multiply-Accumulate (MAC) operation works on three operands, the Montium ALU has four input operands (most ALUs have only two input operands). Each of these input operands has a private register file, which cannot be bypassed, and can be written by multiple sources (e.g. memories or interconnects). Every cycle the Montium ALU produces two outputs which are directly connected to the interconnect. The ALU consist of an upper and a lower level. The upper level contains four function units, these function units implement general arithmetic and logic functions. The lower level contains an MAC and a butterfly unit typically used in many DSP algorithms. Each ALU has a single status bit output that can be tested by the sequencer that controls the Processing Part Array (PPA).

Figure 1.2: Simplified schematic of the Arithmetic and Logic Unit

**remark:** To minimize the number of configuration registers used, the Montium compiler will try to merge instructions whenever possible. Example given: Assume an algorithm that needs a ALU to performs a MAC operation every other clock cycle, but doesn't need the ALU the remaining cycle. The Montium configuration will simple contain a single configuration for the ALU, containing the MAC operation. The unwanted result, generated every clock cycle the MAC isn't needed, simply gets disregarded, since it will not be used/written anywhere.

#### **Register Files**

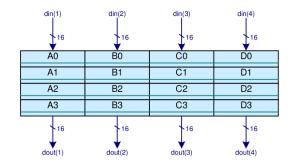

Every ALU in the Montium Tile has four register files, one for every single input A, B, C and D. Every one of these register files can hold up to four 16 bit values. Each register file is controlled by a read address, a write address and a write enable signal.

Figure 1.3: Register File inside an ALU

#### The Montium AGUs

There are 10 local memories on the Tile, every PP has two local memories, denoted as left-hand side memory and right-hand side memory. Every memory in the Montium has its own reconfigurable Address Generation Unit (AGU). These AGUs can generate simple memory access sequences typically used in DSP algorithms. Operations that these AGUs include are, among others, incrementation, bit-reversal, apply-ing and-masks.

#### Interconnect System

The Montium Processing Part Array has a reconfigurable interconnect for flexible routing of data within the Tile, that can use a different configuration every clock cycle. There are 10 Global Busses (GB01..GB10) used for interprocess communication and every PP has a local bus connecting the ALU to its local register files and two local memories. In total there are 20 data sources in the PPA (10 memories and 10 ALU outputs) and 30 data sinks (10 memories and 20 register files). In addition to on-tile communication the CCU can use the Global Busses to connect the tile to the outside world, every cycle at most 4 inputs and 4 outputs can enter and exit the Tile via the CCU.

#### Control in the Montium TP

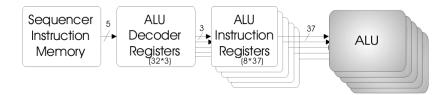

The combinations of concurrent functions the five ALUs can perform in a single clock cycle is called a pattern. The flexibility of the PPA results in a vast amount of possible patterns. The programmability of the PPA is limited for efficiency reasons. For example[7] take the control of an ALU (see Figure 1.2). In the Montium each ALU has 37 control signals, resulting in  $2^{37}$  possible function patterns per ALU. In practise however, only a few combinations are actually used. The functions an ALU needs to execute a stored in *ALU instruction registers*. Each ALU has 8 of these registers, at runtime every clock cycle one of these registers is selected to control the function of the ALU. An *ALU decoder register*, which is also a configuration register, determines which ALU instruction register is been selected for every ALU. As there are five ALUs on the PPA, there are  $8^5$  different combinations possible. However in practise not all of these are actually used for one application. Therefore, there are only 32 ALU decoder registers in the Montium.

Figure 1.4: Control of an Montium ALU

Every cycle the sequencer instruction selects a ALU decoder register which will select an ALU instruction register for every ALU. In summary the 185 (5 x 37) control signals for the ALUs are reduces to 5 signals for selection of the ALU decoder register. This same two layered scheme is also used for the memories, register files and interconnect configurations.

#### The Montium Sequencer

The Montium sequencer is basically a state machine, that in every clock selects a register for every decoder (ALU decoder, memory decoder, register decoder and interconnect decoder). The current address in the sequencer program, called the Program Counter (PC), specifies which register to select in every decoder. The flow trough this sequencer program can be influenced by the sequencer instruction and arguments. The Montium sequencer has a fixed instruction set:

| encoding | mnemonic | description                  |

|----------|----------|------------------------------|

| 000      | JCC      | Jump Condition Code          |

| 001      | JNC      | Jump Not Condition (code)    |

| 010      | LLC      | Load Loop Counter            |

| 011      | LOOP     | Loop                         |

| 100      | SIG      | General purpose IO signaling |

| 101      | CCC      | Call Condition Code          |

| 110      | CNC      | Call Not Condition (code)    |

| 111      | RET      | Return                       |

The branch instructions (JCC, JNC, CCC and CNC) can use the ALU status outputs, handshake signals from the CCU and internal sequencer flags. Although the sequencer supports conditional jumps, their usage should be kept to a minimum for optimum performance. Algorithms that require a lot of conditional code can better be implemented on a general purpose processor. The Montium Tile has four 11-bit loop counters that can be used either individually or combined in pairs. A simple Montium sequencer program could look like this:

| PC | sequencer instruction | arguments | description                     |

|----|-----------------------|-----------|---------------------------------|

| 0  | JNC                   | $GPI_0 0$ | wait for "Data Valid" $(GPI_0)$ |

| 1  | JNC                   | TRUE 0    | single cycle                    |

| 2  | LLC                   | 0 1022    | load $LC_0$ with 1022           |

| 3  | LOOP                  | 03        | loop on $LC_0$ (to PC 3)        |

| 4  | SIG                   | 0 1       | set $GPO_0$                     |

| 5  | SIG                   | 10        | clear $GPO_0$                   |

| 6  | JCC                   | TRUE      | jump to beginning               |

## 1.2 Assignment

Development and study of algorithm mapping onto a coarse grained reconfigurable architecture requires the possibility to verify and debug the produced code. Several reasons exist why testing on a real chip is not always a good option:

- 1. A development board may not always be available to a developer, since these development boards are expensive to produce.

- 2. During the development process the developer needs to be able to see how his code is being processed, how variable values change over time, where data comes from and goes to (the developer needs to be able to look inside the contents of the chips registers and memories).

- 3. The developer needs to be able to observe and verify the implementation effects of his algorithm, especially in the field of DSP algorithms some effects may only become visible or reliable after extensive simulation (e.g. quantization effects). For these reasons a fast simulator of the target architecture is needed.

The simulator currently available for the Montium TP, 'Simsation', has some disadvantages:

1. It is not very flexible for the end-user. While compiler options are available to developers to change certain attributes of the Montium TP instance, these changes do not work on the current simulator (in fact a binary compiled with custom parameters will not work in the current simulator at all).

- 2. Since it simulates the internals of the architecture it has to do a lot of (extra) work not really interesting to a software developer who just wants to verify the results of his program. Speed especially becomes an important issue when algorithm precision needs to be analyzed, since verifying (average) bit-error-rates of certain scaling or quantization effects often requires simulating many billions of cycles.

- 3. It proofed to be somewhat burdensome to implement a Graphical User Interface on top of it. Communication with the simulator is possible only via a (telnet) socket and thus a lot of message passing and parsing needs to be done. Exporting a public API could greatly simplify this process.

The goal of this project is to research, design, implement and test a functional simulation generator for the Montium TP which has to be flexible in terms of architecture parameters and fast in execution.

## **1.3** Structure of this report

After this introduction, in Chapter 2, some related work will briefly be summarized to place this work in perspective to what has already been done in similar research projects. In Chapter 3 some design choices made in the early stage of the project will be discussed. After the design choices are made clear the implementation of the simulation generation process is explained in Chapter 4, there the reader can also find examples of generated code blocks. In Chapter 5 the Communication and Configuration Unit of the Montium Tile will be discussed. Chapter 6 will show how the created simulation generator is extended to simulate the Annabelle prototype chip, created within the 4S project. Chapter 7 will present the results achieved in this project, including benchmarks and comparisons. These results will be followed by some conclusions and recommendations in Chapter 8 which will be the final chapter in this report.

# Chapter 2

# **Related Work**

Probably since the day digital chips where first introduced there has been a need for software that can simulate those chips. This need comes for the same reasons that where already mentioned in the introduction: the unavailability of real hardware and the possibility for the developer to see inside the chip while a program is running. So a lot of research has been performed in the field of simulators. This chapter summarizes some research projects related to this project in order to give some perspective.

## 2.1 Simulation techniques

Several different approaches can be identified for creating simulators: (1) (V)HDL Simulators, (2) Instruction Level Simulators and (3) Binary compiled simulations

#### 2.1.1 (V)HDL simulators

Simulations based upon VHDL or Verilog hardware description languages emulate all signals that exist in the real hardware thus provide a real close one-to-one relation to the actual chip. This is particularly useful when the correct functional behaviour of the chip has to be examined. This approach can also be used for examining real elapsed time or energy consumption of the chip (or the specific implementation of an algorithm). The main disadvantage of this approach is that it is really slow, the simulator will typically require many thousands of host cycles to simulate a single target cycle.

An approach close to HDL simulation was researched by Aly and Salem [8], [9]. They build *RTLJava*, an RTL (Register Transfer Level) simulator written in Java. They use Java's built-in multithreading and observability features to deal with concurrency, parallel execution of statements, and reactivity problems that most HDL simulators cope with. This approach results in a simulator that resembles the hardware closely, but is easier to

modify, operate and link to other software than a VHDL simulation. A disadvantage is that it has to do a lot of update calls to all the primitive objects to simulate a single cycle.

#### 2.1.2 Instruction level simulators

Instruction level simulators usually act as op-code interpreters, a target program is executed by decoding every op-code instruction sequentially, just before execution (just as the real chip would do). However, the internals of the simulator do not necessarily resemble the real chip at all. Because all decoding and interpreting steps have to be done at runtime, these simulators tend to perform rather poorly.

A big problem often faced when creating instruction level simulators lies in the fact that it is quite a lot of work to develop one for every newly developed chip. *Sleipnir* [10] is a tool that eases writing IL-(instruction level) simulators. It makes the development of IL-simulators easier by only requiring a description of the target chip. It works by compiling a machine description language into C source code files, which can be compiled to an executable simulator. The generated simulator is an interpretive simulator, meaning it has to decode instructions at runtime. Togawa et al. [11] also use code-generation to generate an instruction level simulator for DSP type processors. Their main goal was to include support for packed SIMD instructions.

#### 2.1.3 Binary compiled simulation

In case of binary compiled simulation the simulator generates a native binary for the host platform directly based upon the input program meant for the target chip. So for every target program a new unique simulator binary will be generated. This approach generally results in very fast simulations, but very often lacks end-user flexibility because the hardware description of the target platform is usually embedded inside the binary generator.

Pees et al. [12] designed a compiled binary simulator based on the machine description language LISA. Later this work was extended by Nohl et al. [13] with their so-called JIT-CSS, Just-In-Time Cache Compiler, technique to regain the flexibility of an interpretive simulator. It worked by pre-compiling all instruction blocks beforehand, placing them in a cache and then run the simulation just like an 'interpretive' simulator would but instead of interpreting every instruction it will fetch the desired one from the compiler cache.

## 2.2 The 'Simsation' simulator

Another project closely related to this project is the currently existing Montium TP simulator, 'Simsation', already mentioned in the Introduction. 'Simsation' is an interpretive simulator that simulates all internal signals that exist inside the Montium TP hardware architecture. The user has to navigate through a tree like structure to locate the different variables of interest (or create scripts to do so). Though this simulator works correctly, it has a few drawbacks: (1) It lacks end-user flexibility in terms of Montium design parameters, (2) It is not really fast, and finally (3) There is no Graphical User Interface available (and it is not designed so that one can easily be added on top of it).

# 2.3 The Montium TP Simulation Generator

In this project we will try to combine the flexibility of interpretive simulators with the performance of binary simulation. We do this by creating a simulation generator that can generate and compile new binary simulations internally (based on a binary target program and design parameters for the target). Because in the case of the Montium Tile Processor we have an entire *configuration*, ( $\approx$  the program), available beforehand, we can generate and compile code not just for single instructions, but for the entire configuration at once. Another difference with Instruction Set Architectures, or ISA, is that ISA based systems all start every cycle by decoding the next instruction, fetching operands, doing some calculation on the operands and finally writing the result back to some memory entity. The Montium TP however, being a coarse-grained reconfigurable chip, doesn't have this sequential behaviour so obviously available.

# Chapter 3

# Design

### 3.1 Benefits of a functional simulator

A functional simulator simulates the functional behaviour of its target platform, in contrast to simulating all internal signals. This means that the functional behaviour can be implemented in a way that is efficient on the host architecture, for example a multiplier that uses multiple steps in the VHDL description, with or without intermediate results, would also take multiple steps to simulate in a VHDL simulator approach but in a functional simulator it would just be passed to the host processor as a single multiply instruction with two operands. Obviously this functional approach results in much better performance of the resulting simulator.

# 3.2 Simulation generation

Instead of simulating a Montium program by interpreting a configuration cycle for cycle we instead generate Java code for the configuration, compile it (internally) and start an instance of this newly created program. This gives us the best of two worlds of simulators. It provides the flexibility of an interpreter, because we can use runtime variables. But it should also give us the performance of a binary compiled simulation, because we in fact generate a compilable version of the current program and compile it. The generator will thus use two inputs: (1) the binary Montium configuration and (2) the specific Montium Design Parameters (if the latter is omitted, the generator will continue with the default Montium Design Parameters).

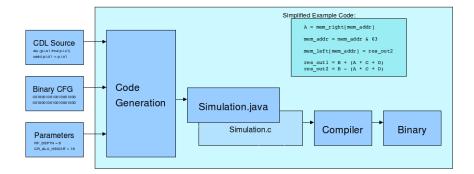

Figure 3.1: Code Generation schematic

Figure 3.1 shows schematically how the Simulation Generation process works. The generator has up to three inputs:

- 1. CFG, the pseudo-binary Montium configuration as is generated by the Montium Compiler (mandatory input).

- 2. PRM, the Montium Design Parameters (optional, as there are default parameters).

- 3. CDL Source, the source code that was used to create the binary Montium configuration (optional, not actually used in the code-generation process but only used for visualization).

Though it would have been possible to build a simulation generator that uses CDL source as primary input, there are several reasons why the compiled configuration file was chosen for this:

- Several steps the compiler performs are needed before simulation generation. If CDL source would be the primary input for the simulation generator these steps would have to be duplicated:

- Semantic checking of the source code.

- Allocation of global- and local interconnects.

- By using the binary configuration format as input the simulation generator will also be able to simulate configurations compiled with future (higher level language) compilers.

# 3.3 Target Language

Because the final simulator needs to be portable, Java was chosen as the target language. All end-users will need to have, in order to use the simulator, is a JDK installed on their system. No external libraries will be required. Using Java also makes it easy to separate the program functionality from the user interface, making it easy to embed the simulation generator in a future integrated development environment or maybe even embed it a some sort of scriptable environment.

Another important reason to prefer Java is the new *compiler* feature introduced in JDK 6 SE. This new internal compiler feature makes it possible to create a simulation generator that will perform the code generation and compilation process **internally**, hiding these details from end-users. This means the end-user doesn't need to understand, or even know about this code generation and compilation process, nor does he need to make explicit calls to a compiler or build tool. In case of C code generation a complete C toolchain (e.g. GCC and make) is required on the running machine.

However, since C is still assumed to be faster than Java in program execution, the generator will be designed so that it can produce either Java or C code. Benchmarks will be performed to see whether Java truly is a viable choice.

Figure 3.2: The Simulation Generation process using Java (above) or C

## **3.4** Required functionality (API)

For operation of the simulation the generated simulator will have to export a public accessible API. This API will provide the end-user, via a graphical interface or even directly from an Java program, with basic controls needed to manipulate a running simulation. The basic API should in some way provide at least the following functionality to the end-user:

| run(int n)              | run n cycles                    |

|-------------------------|---------------------------------|

| $\operatorname{step}()$ | run a single cycle              |

| back()                  | step back a single cycle        |

| back(int n)             | step back n cycles              |

| get(name)               | show the current value of:      |

|                         | - a register                    |

|                         | - a memory location             |

|                         | - a status bit                  |

| set(name)               | override the current value of:  |

|                         | - a register                    |

|                         | - a memory location             |

|                         | - a status bit                  |

| watch(name)             | break upon the value change of: |

|                         | - a register                    |

|                         | - a memory location             |

|                         | - a status bit                  |

Please note that this is not the final implemented API. For a complete overview of the final implemented API see appendix A.

## 3.5 Software Design

Figure 3.3 is a simplified UML view of how the final **generated** Simulator is build, the *ASimulation* class is an abstract class that is needed so we can refer to Simulation methods inside the encapsulating program (e.g. make calls to  $getMem(int \ m, int \ l)$  from inside the GUI classes) without having an actual Simulation class instantiated, or even compiled. The *Simulation* class is the most important class, this is the class that has to be generated by the generation process. It will implicitly contain the Montium design parameters and the Montium Configuration that were passed as inputs to the simulation generator. The SimulationController is responsible for loading and managing the Simulation instance. It also keeps track of cycles simulated (the Simulation doesn't care about cycles), and provides some higher-level interactions with the Simulation (e.g. parse command-line commands containing *Strings* like  $setReg(pp1 \ A \ 6)$  or running until a certain value changes). The *SequencerStateMachine* is responsible for cal-

culating the new *Program Counter* every cycle, based upon the current PC, the tile SB (status bits), the current instruction and the arguments given.

Figure 3.3: Simplified UML overview of the Simulator design

## 3.6 Flexibility

One of the two goals of this new simulator was to obtain more flexibility with regard to Montium design parameters and internal functional behaviour.

#### 3.6.1 Montium design parameters

The currently available Montium compiler supports several parameters describing characteristics of a Montium Tile instance. This flexibility should also be available in the simulator, not just to the engineers at *Recore Systems* that have access to the simulator source code, but also to their clients. Thus these parameters should be runtime configurable.

These parameters should include, but not necessarily be limited to, the height of decoder and configuration registers, the width of memory addresses (thus the size of memories) and the depth of register files. For a complete list or currently implemented parameters see appendix B.

#### 3.6.2 Functional behaviour

Besides parametric changes it should also be possible to easily extend/change the functionality of the functional units of the Tile. Even making changes to the datapath should stay simple enough to be performed whenever needed. Examples of such changes could be removal of one or both levels of functional units or extending the level 1 functional units with MIN and MAX function (by default only available in the level 2 functional units). Because clients probably shouldn't be allowed complete freedom to the datapath functionality, this flexibility is not necessary at runtime. Moreover implementing this kind of flexibility at runtime would require some sort of specification language for describing this functional behaviour, and using that language would require skills similar to normal programming skills. Rather than inventing a new specification language one could just as well use Java code itself for the specification, assuming it is possible to isolate this code in a single place. This code isolation can be achieved by using the Visitor pattern for code generation of ALU expressions and creating *helper functions* for the different operation in the Functional Units.

## 3.7 Initial State and end-results

For testing of algorithms it is often useful to start a simulator with all the memories and register files filled with some initial values. For fast correctness testing it can also be useful to compare the final contents of all memories and registers with some pre-defined *expected results*. Finally, to produce some figures about results it can be convenient to be able to write all memory-and register contents to easily parseable output files at any time during the simulation. For these input and output files it was chosen to use the same format the currently available simulator uses, so that these are interchange-able and don't have to be created twice. The format is quite simple, the files have an hexadecimal address-value pair on every line.

# 3.8 The optimization steps

One of the prospected advantages of functional simulation in contrast with full signal simulation, combined with the fact that we analyze the entire configuration beforehand, is that now several optimization steps can be performed. Everything that has no effect on the final state change of the simulator can be removed from the generated code.

#### 3.8.1 Straight forward optimizations

The most straight-forward form of optimization lies in disregarding statements that don't change anything to begin with. For example calculating the output of a functional unit that isn't really used can be skipped.

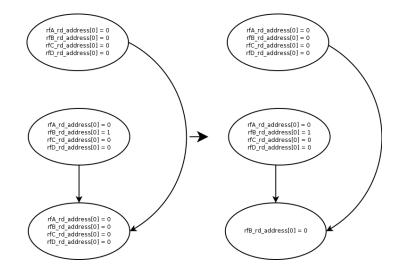

### 3.8.2 Look-back optimizations

All transition from one line in the sequencer program to the next can be deduction from the configuration. This means that already at generation time the generator can identify what the previous PC could have been. If for all these predecessors a certain read address were the same as for the current PC, than the simulation code for that assignment can be left out in the code for this PC (this will probably remove close to 20 assignments in many cycles, since in many cycles the register file read addresses remain the same).

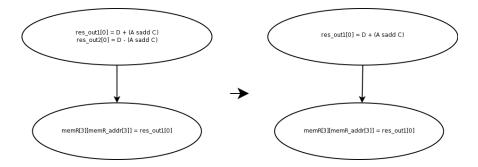

#### 3.8.3 Look-ahead optimizations

This is probably the most effective optimization scheme, for it is capable of removing big blocks of unnecessary calculations. The Montium Tile processor generates 10 outputs for its 5 ALUs, but many of these outputs are never actually written anywhere. At generation time it should be possible for the generator to check all possible *next-states* of the current state, if none of these *followers* write a specific output to a memory, register or global interconnect we can remove the calculations that provide that specific output without changing the end-results of the simulation.

# Chapter 4

# Implementation

This Chapter describes the implementation of the Simulation Generator. The overall flow of a simulation is shown in Figure 4.1. The white boxes represent steps in the Simulation Generator and the colored boxes are an example of how a Simulation run could look like.

Figure 4.1: Simulation Generator overview

#### 4.1 Configuration parser

The Montium compiler produces pseudo-binary output files containing a Montium TP configuration which can be loaded into a Montium processor via its configuration interface. Because the configuration data bus of the Montium is 16 bits wide but configuration lines can vary in width, e.g. an ALU configuration line is currently 37-bits wide, two different views of the configuration entity exist: (1) the normal view, in which every entity has it's own specific width and (2) the configuration view, in which every entity is at most 16-bits wide.

The pseudo-binary configuration file contains the 16-bits configuration view, but for processing the information and building a simulator the normal view is needed. So the first task the simulation generator has when it receives a new configuration is decoding this flat configuration view into a datastructure for which all information can be retrieved easily and selectively. Later, during the code generation process, the internal datastructure, created during this parse, can be called to return individual register contents within the entire Montium configuration. e.g. assuming the datastructure for the Montium configuration is stored in *config* then:

$Bv\_SequencerInstruction \ instr \ = \ (\ Bv\_SequencerInstruction \ ) \ config \ . \ getImSeq \ ( \ ) \ [N] \ ;$

will assign the  $N^{th}$  line in the sequencer program, and subsequently calling:

```

int alu_i = instr.get("alu_i");

```

will assign the active line number to select in the *Alu Decoder*. Similar calls can be made to fetch any entity within the loaded configuration.

Because the simulation generator has to be flexible when it comes to Montium design parameters, the conversion from the configuration view to the internal datastructure has to take into account these parameters al well. If for example the design parameters state that the register files should have a depth of 8 (instead of the default depth of 4) the conversion from configuration view to normal view has to realize that for addressing within these register files now 3 bits are required. So, consequently an *register file configuration line* will be 4 bits wider as well (see examples, one bit extra for both read addresses and one bit extra for both write addresses). So, the simulation generator will have to 'know' how all the design parameters affect the configuration space.

| rfA_rd | rfA_wr | rfA_we | rfB_rd | rfB_wr | rfB_we |

|--------|--------|--------|--------|--------|--------|

| 00     | 00     | 0      | 11     | 00     | 0      |

Figure 4.2: An example Register File configuration line, for 4 position deep register files

|   | rfA_rd | rfA_wr | rfA_we | rfB_rd | rfB_wr | $rfB_we$ |

|---|--------|--------|--------|--------|--------|----------|

| ſ | 000    | 000    | 0      | 101    | 000    | 0        |

Figure 4.3: An example Register File configuration line, for 8 position deep register files

The defaults for all these column names and sizes are stored in respectively the *Constants* class and the *StructureVariables* class, and are overridden (if necessary) during the reading of the Montium design parameter file (passed to the generator program as a start-up parameter). A single structure definition looks like Listing 4.1.

| CR_RFAB_COLNAMES = { "rfA_rd", "rfA_wr",       | "rfA_we", "rfB_rd", | "rfB_wr", "rfB_we" }; |

|------------------------------------------------|---------------------|-----------------------|

| $CR\_RFAB\_COLWIDTH = \{ 2, 2, 1, 2, 2, 1 \};$ |                     |                       |

Listing 4.1: Structural description of a Register File configuration register

#### 4.2 Sequencer

Simulation of the Montium *sequencer* consist of two very distinct parts. The first sequencer related task is collecting all actions for the Tile to perform for a certain line in the sequencer program. This part is done by the simulation generator. The second sequencer related task is the runtime task to provide the simulation with the next address in the sequencer program, or the PC, to execute.

#### 4.2.1 Cycle code generation

For every line in the sequencer program a block of code is generated that is the functional equivalent of what the real Montium Tile would do during execution of this sequencer line. This step in code generation will create by far the biggest and most important part of the *Simulation* class. Whenever the **step()** function is called the simulator will check the current PC (Program Counter), execute the code generated for that specific sequencer instruction: update memory, register and global bus values, calculate required ALU outputs, etc and finally return. All the information about actions to perform in a certain PC cycle can be found in the binary configuration. This process is thoroughly described later on.

#### 4.2.2 State Machine

The second sequencer related task, providing the simulation with the next PC, depends on data that is only available at runtime, during a simulation 'run'. This cannot be done at generation time, so for this purpose a *SequencerStateMachine* class is created which will be instantiated by the

simulation at runtime. All this class does is generate the new PC and update the Loop Counters and the General Purpose Out signals whenever necessary.

#### 4.2.3 Switch/case bottleneck issue

Because the first thing that needs to happen when stepping into the next cycle is jumping to the code specific for the active sequencer line, the naive way of building up the step function is to create one huge switch/-case statement containing the code blocks for all possible sequencer lines.

```

public void step(){

switch(PC){

case 0:

...

case N:

}

}

```

Listing 4.2: Main simulator loop - the step() method

This approach would however create a lot of runtime overhead, because most cases would not be taken (a program that uses all sequencer lines in an evenly distributed fashion would produce N/2 jump misses on average for every cycle). This is in fact a known problem/drawback of big switch/case statements in today's software world. C in fact has a solution for this: create an array of function pointers and use that as a table to get the jump addresses from. To find out whether this would pose a big problem in our generated simulation some benchmarks where performed on two different approaches:

- 1. Use C function pointers as a reference.

- 2. Use a single huge switch/case statement, as described above.

- 3. Use so-called anonymous classes extending some interface that has a run() method, and place these anonymous classes in an array (this resembles the C function pointer approach).

|                       | minutes | seconds | calls/sec  | score |

|-----------------------|---------|---------|------------|-------|

| C (function pointers) | 9.48    | 588     | 1.13E + 11 | 100   |

| Anonymous Classes     | 16.58   | 1018    | 6.55E + 10 | 57.76 |

| One big Switch Case   | 13.41   | 821     | 8.12E + 10 | 71.62 |

Table 4.1: Benchmark results 'anonymous classes' vs. switch

The above benchmarks where executed with 256 different case statements, with a single line of actual code inside them. To prevent the compiler from optimizing the step out of the actual execution the code was setup to return an integer depending on input values, which is again passed to the next **step()** call. The results of this benchmark showed that using anonymous classes was not a solution to our problem, but it also showed that using the switch/case wasn't as bad as expected. So it was decided to proceed with this approach (hoping to optimize it somewhat more later on).

Because Java has a hard limit on the maximum length a method can be the switch/case statement was split up in two levels. In the first level step() jump to step1() if the PC to execute next lies between 0 and 15, jump to step2() if it lies between 16 and 31, and so on for all possible lines in the sequencer program. Mid-way during the project it was discovered that this approach indeed still held back performance by some sort of bottleneck issue, so some different variations on this approach where tested and finally some extra trial-and-error testing showed that the best approach was in fact:

• Create a tree with a maximum of four levels, balancing the code blocks amongst the number of required levels (if there are just 4 lines in the sequencer program, create only one level, if there are 12 lines create 2 levels with 3 leaves in all the second level methods.... and so on (when all 256 sequencer configurations are used this will give a 4 level tree with 4 'leaves' in the final levels).

Listing 4.3: Generated switch/case tree

#### 4.3 Code generation

When the code generation process starts first the basic simulation necessities are written to the *Simulation* class. These necessities contain the following distinct elements:

- Montium Tile datastructure, placeholders for all internal variables like memories, registers and intermediate results.

- Simulation initialization functions, methods that take care of reading input files, writing output files, resetting the simulation and so forth.

- Simulation API, these are the get() and set() functions used to obtain/manipulate the Tile's state information during simulation

- Helper functions, that implement the special functions inside the Functional Units that can not be expressed in 'in-fix' java notation, these helper functions also include status bit update methods.

The full Tile datastructure is given in Appendix C and the Function Unit Helper functions can be found in Appendix D. The other methods are not included in this report, because they have little value to people other that the software maintainer of this project. When these basic simulation necessities are written to a Simulation class, the Sequencer code generation process is started. This will add the code blocks for every sequencer line present in the loaded configuration. The configuration however, contains all the actions without any notion of precedence. In order to create a sequential piece of java code for every block, a sequence<sup>1</sup> in which things should happen has to be created:

- 1. check if tile blocked by IO (if so **break** without change)

- 2. Fetch value from lane\_in lanes

- 3. Write values to lane\_out lanes

- 4. Calculate next Program Counter

- 5. Reset Status Bits

- 6. Set read addresses for the register files

- 7. Write registers, using the correct write addresses

- 8. Undo previous bit-reversal and calculate new AGU outputs

- 9. Write memories

- 10. Calculate ALU outputs

#### 4.3.1 Decoders

The decoders of the Montium Tile processor only select the active addresses for different configuration registers. So they do not need to become a real part of the simulation at runtime. For every cycle for which the generator needs to generate code it will select all the decoder lines to use, based upon the active sequencer line. With these decoder lines the generator can select the correct configuration register for every entity (Register File, ALU, AGU or Interconnect) it should generate code for.

<sup>&</sup>lt;sup>1</sup>The correct sequence is not uniquely defined, several correct variations also exist.

#### 4.3.2 Global and Local Interconnections

For transferring data from the different data sources to data sinks the Montium PPA (Processing Part Array) has a configurable interconnect that can be reconfigured every clock cycle. Several components of this interconnect can be configured individually:

- The active *global interconnect* configuration registers define the sources for the global busses.

- The active *streaming IO* configuration register defines whether any of the global busses is connected to the outside world via in- and output lanes.

- The active *local interconnect to memory* configuration registers define the sources for local busses to the local memories of the processing parts.

- The active *local interconnect to register* configuration registers define the sources for local busses to the local register files of the processing parts.

Sequentially resolving these connections individually would result in code like in Listing 4.4 for a single write action.

```

// gint -> connect memory 9 to global bus 2

GB02 = mem_left [4] [memL_address [4]];

// lint2r -> connect global bus 2 to the local interconnect to

// register of the first processing part

lint_rfA_connection [0] = GB02;

// rfAB -> write the value on the local interconnect to register

// to register A address 0

rfA [0] [rfA_wr_pointer [0]] = lint_rfA_connection [0];

```

Listing 4.4: Example generated code for individual interconnects, transfers a value from memory 9 to register A of the first processing part

Because all this information is available at generation time, and since we are only interested in simulation of the functional behaviour, this generated code can be reduced to a single assignment like shown in Listing 4.5.

For every write actions in a Register or Memory, and for every Streaming output, the source that produced the value to the interconnect can be discovered by combining the information in the active *local interconnect to memory*, *local interconnect to register*, *global interconnect* and *streaming IO* configuration registers mentioned above.

$rfA[0][rfA_wr_pointer[0]] = mem_left[4][memL_address[4]];$

Listing 4.5: Example generated code for combined interconnects

Because this source determination has to be done at several places in the code, namely for all Register writes, Memory writes and Streaming IO outputs the *GlobalInterconnect* class was created. Given the *target* in the specific local interconnect (or 'lane2gb'), the active configuration for the global interconnects and the active streaming IO configuration, it returns a String representing the source variable inside the generated Simulation class (this String is then immediately added to the generated code). These Strings returned by the *GlobalInterconnect* can be any of:

| "mem_left[04][memL_address[04]]"  | any left-h      |

|-----------------------------------|-----------------|

| "mem_right[04][memR_address[04]]" | any right-      |

| "res_out1[04]"                    | the $1^{st}$ re |

| "res_out2[04]"                    | the $2^{nd}$ re |

| "GB[09]"                          | any glob        |

|                                   | connected       |

any left-hand side memory. any right-hand side memory. the  $1^{st}$  result of any ALU. the  $2^{nd}$  result of any ALU. any global bus (indirectly connected via the Streaming IO configuration (see next section)).

#### 4.3.3 Streaming IO

To allow streaming algorithms, the Montium Tile is connected to a NoC (Network-on-Chip), via a CCU (Communication and Configuration Unit). One of the tasks of this CCU is providing data to- and consuming data from the global busses in the Montium. The CCU part of this process consist of adding data to- and reading data from a FIFO buffer. In streaming algorithms the Montium configuration decides when to connect a global bus to an external lane. Via this connection the Montium can now receive data from the CCU output buffer or write data to the CCU input buffer.

During code generation this means that when streaming IO is enabled for a certain line in the sequencer program, the code generator needs to check whether a certain global bus is connected to a lane input and if so generate code for fetching the next value from the CCU buffer and assign it to the specific global bus variable (global busses are represented by a single variable in the simulator). If later in that cycle that global bus is used as a source for a register or memory write, we can simple assign the variable name for that bus. Also some code has to be added that breaks out of the current execution if there is no value received from the CCU. That way the simulator would remain executing the same block over-and-over until the next value is available thus simulating blocked IO. Code generated in a cycle using streaming IO input will look like Listing 4.6.

Listing 4.6: Example generated code for Streaming IO input

If any of the *gb2lane* columns in the active streaming IO configuration is non-zero, then code will be generated for placing an output value on that specific lane, the CCU will retrieve this value after the Tile is done for this cycle. Code generated in a cycle using streaming IO output will look like this:

| FType = 0;                   | // set flit-type for data to CCU        |

|------------------------------|-----------------------------------------|

| lane_out_buf[0] = res_out1[0 | ]; // set data ready for reading by CCU |

| $data_waiting [0] = true;$   | // inform the CCU there is new data     |

Listing 4.7: Example generated code for Streaming IO output

#### 4.3.4 Register Files

Every ALU in the Montium Tile has four register files, one for every single input A, B, C and D. The current Tile has four positions for every one of these register files (the compiler and the simulator can vary this depth, by altering the RF\_DEPTH parameter).

Before calculations can be done the simulator has to know the active read and write positions in these register files. They can be obtained from configuration registers  $cr_rfab$  and  $cr_rfcd$  of the processing part, selected by the Register decoder. Write sources can be decoded by combining the information in the local interconnect to register, the global interconnect and the streaming IO configurations. For a single processing part this will result in code blocks like this one:

Listing 4.8: Example generated code for a Register File

#### 4.3.5 Address Generation Units

The Montium Tile processor contains a reconfigurable Address Generation Unit or AGU for every memory on the tile. These AGUs are capable of generating simple addressing schemes often used in DSP algorithms[1]. The code generation for the AGUs works according to the following sequence: (all references to registers refer to configuration registers, their values are retrievable from the currently loaded Montium configuration.)

- 1. check (the *add\_offset* register to see) if the *sel\_offset* register for this cycle should be added to the previous address or be used directly as new offset. And add the corresponding code to the simulation.

- 2. add code to the simulation that applies the AND mask from the *sel\_mask* register to the memory address

- 3. check (the *add\_base* register to see) if the *sel\_base* register for this cycle should be added to the previous base-register or be used directly as new base. Add the corresponding code to the simulation.

- 4. check if *load\_addr* is set for this cycle, if so then decode the source location from the local and global interconnect registers and add code for using either the low, if *load\_low* is set, or the high part of received 16-bit value as new memory address.

- 5. save a backup of the address register and apply bit-reversal on the output address if  $br_width != 0$  (This backup is restored in the next cycle just before the AGU will produce a new output).

- 6. check if the *we*, write enable, bit is set in the current memory configuration register and if so, decode the source from the local interconnect to memory, the global interconnect and the streaming IO configuration registers values and write this to the active memory address.

The code generated for a single AGU could look like this:

|   | $memL_address [4] = (memL_address [4] + 1) \& MEM_MINUS_ONE;$<br>$memL_address [4] = (memL_address [4] \& 63);$ |

|---|-----------------------------------------------------------------------------------------------------------------|

| 1 | memL_base $[4] = 1;$                                                                                            |

|   | memL_address [4] = (memL_address [4])   (memL_base [4] << MEM_WIDTH_WO_BASE);                                   |

|   | $prev_memL_address[4] = memL_address[4];$                                                                       |

| 1 | $memL_address[4] = BitUtil.reverseBits(memL_address[4], 6, MEM_ADDR_WIDTH);$                                    |

Listing 4.9: Example generated AGU code

#### 4.3.6 Code generation visitor for the ALUs

As mentioned before in Sectionrefsect:funcflex, the visitor pattern was used to create so-called abstract syntax trees (ASTs) of the ALU instructions. This way all code related to the code-generation can be kept in one single place, in the *JavaCodeGenerationVisitor*. AST nodes have been made for:

| name            | parents                   | description                        |

|-----------------|---------------------------|------------------------------------|

| IntNode         | none                      | fixed integer value                |

| NullNode        | none                      | fixed '0'                          |

| VarNode         | none                      | a variable name accessible in      |

|                 |                           | the Simulation class, e.g.         |

|                 |                           | "rfA[pp][rfa_rd_pointer[pp]]"      |

| Add             | in0, in1, enable          | addition node                      |

| FU_std_lvl1     | in0, in1, ctf             | top-level Functional Unit          |

| FU_std_lvl2     | in0, in1, ctf             | second level Functional Unit       |

| Mult            | in0, in1, sel             | multiplication node                |

| Mux             | in $0 \dots$ in $N$ , sel | multiplexer node                   |

| RtMux           | in0, in1                  | multiplexer node, that can only    |

|                 |                           | make a decision at runtime         |

| Convert115to216 | in0                       | add precision bits                 |

| Convert115to416 | in0                       | add precision bits                 |

| Convert170to171 | in0                       | add precision bits                 |

| Convert216to316 | in0                       | add precision bits                 |

| Convert316to416 | in0                       | add precision bits                 |

| ConvertEnable   | in0, status               | enables a parent node, or pass '0' |

| GetHigh         | in0                       | node that takes high part of a     |

|                 |                           | 32-bit multiplier result           |

|                 |                           | (fixed-point multiplication)       |

| Saturate32to17  | in0                       | saturates a 32-bit multiplier      |

|                 |                           | result to 17.0 fixed-point value   |

|                 |                           | (integer multiplication)           |

| Saturateto216   | in0                       | saturates the east-west result     |

|                 |                           | to 2.16                            |

| Scale           | in0, sel                  | scale the end result if requested  |

| Roundto415      | in0                       | rounds the end result              |

| Saturateto115   | in0                       | saturates the end result to 1.15   |

Table 4.2: Overview of AST Nodes

These AST nodes are interconnected in *Alu.java* to represent the current datapath structure. This datapath structuring code remains quite readable, so that future modifications to the datapath can be implemented in the simulation generator with minimal effort. It's even possible to extend this structure with conditional connections, creating runtime flexibility in the datapath. Listing 4.10 shows an example of the ALU connection code, for the fragment of the Montium datapath shown in Figure 4.4, the entire datapath can be described in this very syntax:

```

// level 2.mux

mux_mX = new Mux( new Wire(new NullNode()), wA, wB,

new Wire(fu[2]), selmx

new Wire(new NullNode()), wC, wD,

mux_mY = new Mux(

new Wire(fu[3]), selmy

level

2. multiplier

mult = new Mult(new Wire(mux_mX), new Wire(mux_mY))

selmw

// level 2. converters and muxes left

21 2. converters and muxes left

= new Saturate32to17(new Wire(mult));

= new GetHigh(new Wire(mult));

= new Convert115to216(new Wire(mux_mX));

= new Convert115to216(new Wire(mux_mY));

= new Convert170to171(new Wire(conv[0]));

= new Mux( new Wire(conv[2]), new Wire(conv[3]),

new Wire(conv[4]), new Wire(conv[1]),

selmw

conv [0]

conv [1]

conv [2]

conv

3

conv

[4]

mux_mW

selmw

);

```

Listing 4.10: Code describing the datapath fragment shown in Figure 4.4

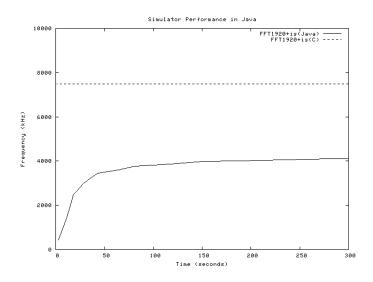

Figure 4.4: Small piece of the ALU datapath

An ALU code block can be generated simply by setting all selection signals from the ALU configuration and then calling the **visit()** method on the two lowest multiplexers selecting the ALU outputs (res\_out1 and res\_out2). The AST is then build bottom-up, meaning the code generation visitor will traverse upwards in the datapath, only generating code for Nodes it actually passes.

#### example

Take the above datapath image and assume that: selmx = 01, selmy = 11 and selmw = 11 (this means that the output of the multiplexer mux\_mW should become the 18-bit fixed-point value of A \* Z1B).

If  $mux_mW$  is now visited by the visitor, it will traverse up to the *GetHigh* converter Node, because *selmw* selects the 4th input of the multiplexer. Next the visitor will traverse to the *mult* Node and from there it will traverse to the  $mux_mX$  Node and the  $mux_mY$  Node. From the  $mux_mX$  Node it will traverse to the wA Node, because *selmx* selects the second input of the multiplier. From there the visitor will traverse no further, because it has reached the top of this AST path (the wA Node is a *VarNode* that only generates code and has no parent nodes). From the  $mux_mY$  node it will traverse up to the FU4 Node outside the range of the above image.