## Sparse Matrix Vector Multiplication on a Field Programmable Gate Array

September 2007

Marcel van der Veen

University of Twente Faculty of Electrical Engineering, Mathematics and Computer Science Computer Architecture for Embedded Systems (CAES) group

Committee: dr. ir. A.B.J. Kokkeler, ir. E. Molenkamp prof. dr. ir. G.J.M. Smit

## Abstract

Sparse Matrix Vector Multiplication (SMVM) has been a subject of research in the computer science field quite some time. The SMVM is an expensive operation used in the Conjugate Gradient algorithm. The Conjugate Gradient is an iterative algorithm used to solve linear equations.

The Finite Element Method is used in a lot of engineering areas like structural analysis, fluid dynamics, heat transport and electromagnetism. Within the Finite Element Method, the Conjugate Gradient algorithm is used to solve large sets of linear equations.

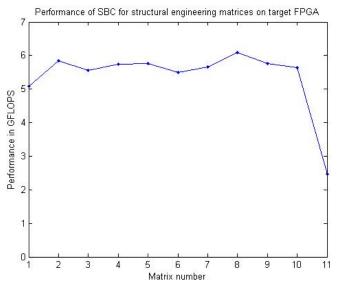

Within the research field of SMVM there are two directions, one direction tries to get the most out of general purpose processors while the other direction tries to make a fast implementation on a Field Programmable Array. This project introduced a new method for the SMVM on a Field Programmable Gate Array called Small Bandwidth Coverage (SBC).

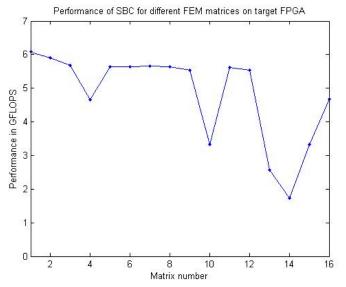

The main advantage of SBC is that the variation in performance caused by differences in the system matrices is only a factor two. Similar solutions have a variation in performance of a factor ten.

## Preface

This project was carried out within the Computer Architecture for Embedded Systems (CAES) group. I would like to thank everybody of the CAES group for a great ambiance. Everyone was equal, professors, teachers, PhD-students and master students. I always suggest master students looking for a master thesis to take look at the CAES group because of the atmosphere.

I would like to mention a few people in particular.

Gerard Smit is professor and head of the CAES group. Despite his busy schedule he is always sincerely interested in the work of all the people working within the CEAS group. He is one of the main factors for providing a great atmosphere.

Pascal Wolkotte and Philip Hölzenspies are two PhD-students who are always interested in the work of others. Always asking good critical question and making suggestions to improve results.

I also want to thank my supervisors Bert Molenkamp and Andre Kokkeler for reviewing my results and reports. They gave me enough room to work out my ideas while keeping the project within bounds.

# Contents

| 1. |        | uction                                               |     |

|----|--------|------------------------------------------------------|-----|

| 2. | Proble | m analysis                                           | 2   |

|    | 2.1.   | Finite Element Method                                |     |

|    | 2.1.1. |                                                      |     |

|    | 2.1.2. | System Matrix                                        | 3   |

|    | 2.1.3. | Reordering                                           | 4   |

|    | 2.1.4. | Solvers                                              | 4   |

|    | 2.2.   | Conjugate Gradient method                            | 5   |

|    | 2.2.1. | Introduction                                         | 5   |

|    | 2.2.2. | Steepest Descent                                     |     |

|    | 2.2.3. | Conjugate Gradient                                   | 9   |

|    | 2.2.4. | Complexity analysis                                  | 10  |

|    | 2.3.   | Sparse Matrix-vector multiplication                  | 11  |

|    | 2.3.1. | Compressed Row Storage Format                        | 11  |

|    | 2.4.   | FEM Matrices                                         | 12  |

|    | 2.4.1. | Example of a regular system matrix                   | .12 |

|    | 2.4.2. | Example of a irregular system matrix                 | 13  |

|    | 2.4.3. | System matrix of the Volume Reconstruction algorithm | .14 |

|    | 2.5.   | Field Programmable Gate Array                        | .15 |

|    | 2.5.1. | MAC unit                                             | 15  |

|    | 2.5.2. | Processing Element                                   | 15  |

| 3. | Desig  | 1 requirements                                       | .17 |

| 4. | Previo | us work                                              | 18  |

|    | 4.1.   | Striping based implementation                        | 18  |

|    | 4.2.   | Preprocessor implementation                          | 18  |

|    | 4.3.   | Straight forward implementation                      | 18  |

|    | 4.4.   | Stripe method                                        | .19 |

|    | 4.4.1. | Štripes                                              | .20 |

|    | 4.4.2. | Construction of SRIO stripes                         | .21 |

|    | 4.4.3. | Systolic array                                       | .22 |

|    | 4.4.4. | Utilization                                          | .23 |

|    | 4.4.5. | Cause of low utilization                             | .26 |

|    | 4.4.6. | Conclusion                                           | .26 |

|    | 4.5.   | Parallel Matrix Communication Network                | .27 |

|    | 4.5.1. | Parallel Matrix Computation Network - Example        | .28 |

|    | 4.5.2. | SIO Example                                          | .29 |

|    | 4.5.3. | Conclusion                                           | .30 |

| 5. | Altern | ative 1: Plans                                       | 31  |

|    | 5.1.   | Computing the SMVM on one PE                         | 31  |

|    | 5.1.1. | Plans                                                | 31  |

|    | 5.1.2. | PE Design                                            | .33 |

|    | 5.1.3. | Mapping of the system matrix                         | .33 |

|    | 5.1.4. | FPGA implementation                                  | .36 |

|    | 5.1.5. | Possible optimization                                | .37 |

|    | 5.2.   | Computing the SMVM on Multiple PEs                   | .40 |

|    | 5.2.1. | Introduction                                         | .40 |

|    | 5.2.2. | FPGA implementation                                  | .44 |

|    | 5.2.3. | Conclusion                                           | .45 |

|    | 5.3.   | Preprocessing                                        | .46 |

|    | 5.3.1. | Example                                              | .46 |

|    | 5.4.   | Conclusion                                           |     |

| 6. | Altern | ative 2: Small Band Coverage                         | .50 |

| 6.1.                           | Short Review of Stripe Method                   | .50 |  |

|--------------------------------|-------------------------------------------------|-----|--|

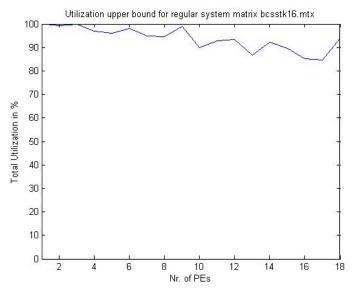

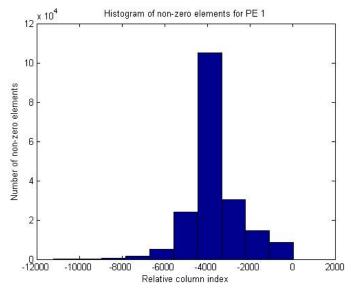

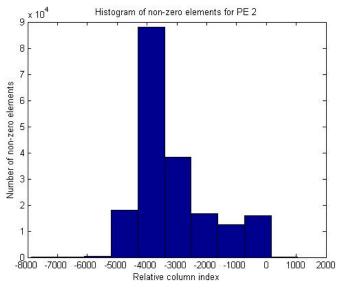

| 6.1.1.                         | Utilization of stripe method                    |     |  |

| 6.2.                           | Small Band Coverage                             |     |  |

| 6.3.                           | Design of PE.                                   |     |  |

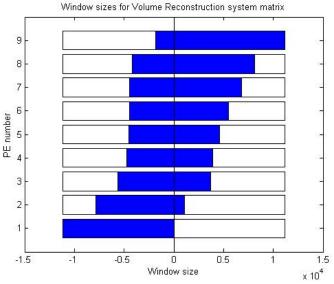

| 6.4.                           | PE band coverage                                |     |  |

| 6.5.                           | SMVM with Small Band Coverage                   |     |  |

| 6.5.1.                         | Example                                         |     |  |

| 6.6.                           | Problems                                        |     |  |

| 6.7.                           | Partial Result Adder                            | .57 |  |

| 6.8.                           | Preprocessing                                   |     |  |

| 6.8.1.                         | Overhead                                        |     |  |

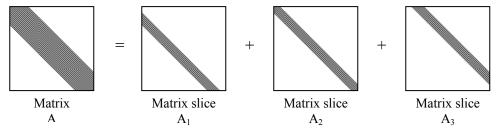

| 6.8.2.                         | Division in matrix slices                       |     |  |

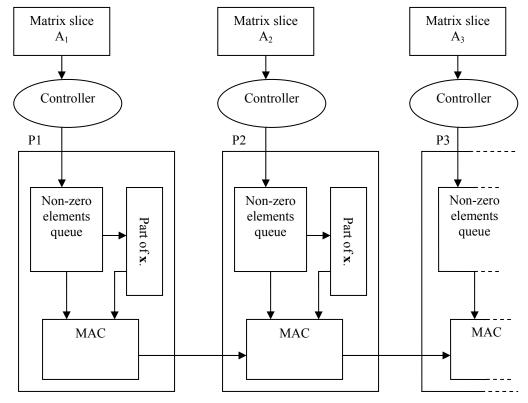

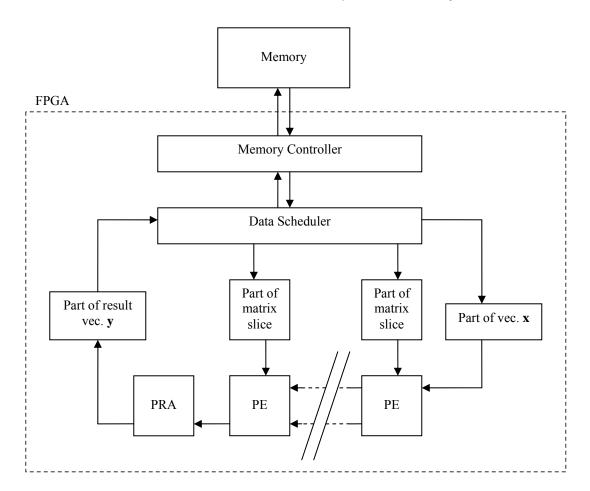

| 6.9.                           | Controller                                      |     |  |

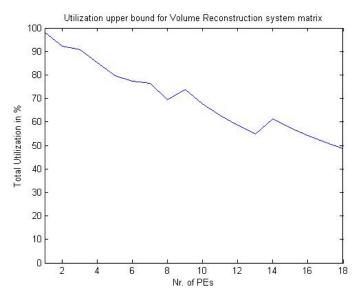

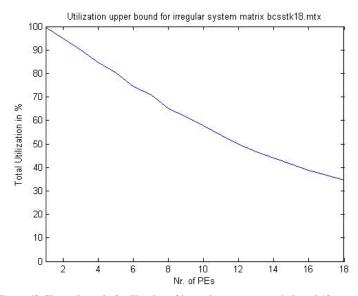

| 6.10.                          | Upper bound Utilization                         | .62 |  |

| 6.11.                          | Preprocessor                                    |     |  |

| 6.11.1                         | 1                                               |     |  |

| 6.11.2                         | . Scheduling the non-zero elements over the PEs | .67 |  |

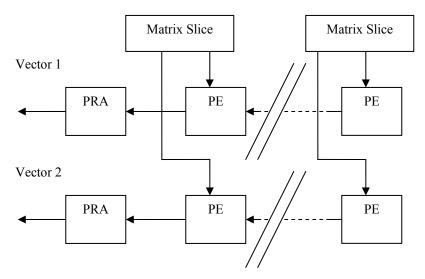

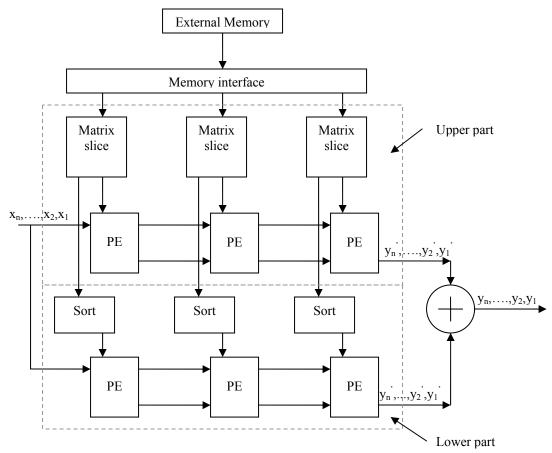

| 6.12.                          | Multi vector design                             |     |  |

| 6.13.                          | Total System                                    | .70 |  |

| 6.14.                          | Conclusion                                      |     |  |

| 7. Result                      | S                                               | .72 |  |

| 8. Future                      | Work                                            | .74 |  |

| 8.1.                           | Improving the partial result adder              | .74 |  |

| 8.2.                           | Symmetry                                        | .74 |  |

| 8.2.1.                         | Store partial results in local memory           |     |  |

| 8.2.2.                         | Convert CSC format into CSR format              | .76 |  |

| 8.2.3.                         | Conclusion                                      | .77 |  |

| 8.3.                           | Implementation                                  | .77 |  |

| 9. Conclusion                  |                                                 |     |  |

| References Original Assignment |                                                 |     |  |

| Original Assignment            |                                                 |     |  |

## 1. Introduction

The Finite Element Method (FEM) is a method often used for structural analysis to compute stress, deformations and internal forces on materials. It can also be used for fluid dynamics, heat transport, electromagnetism and other engineering areas. Recently this method is also used in a new research area: Volume Reconstruction in Diffuse Optical Tomography [1].

Car manufactures use the Finite Element Method for crash analysis. These analyses require a lot of computations. In [2] the execution time of different crash models for super computers is maintained. The crash analysis set is primarily used to compare the speed of different super computers with a real problem. One of the models is a crash with two cars (car2car model). The fastest time is set by the CRAY XT4 super computer with 512 AMD Dual Core Opteron processors running at 2.8 GHZ. Although this is a very fast system it still needs 6274 seconds (104 minutes) to complete [2]. A system with one Intel Dual Core Xeon processors running at 3.0 GHz needs 565261 seconds (157 hours) [2].

The speedup of the supercomputer scaled to 3.0 GHz is (565261/6274)\*(3.0/2.8) = 96.5. Normally you would expect a speedup of 512.

The idea of Diffuse Optical Tomography is to reconstruct the 3D volume of tissue. This technique will be used at first instance for the diagnosis of breast cancer. The Volume Reconstruction algorithm in Diffuse Optical Tomography requires a lot of computations but needs to be completed in several minutes. At the moment, the target time is about fifteen minutes [1]. Besides the time to complete, other factors play a role such as costs and the size of the system. Because the amount of computations is substantial but not as much as the car2car model, a super computer would have enough processing power to fulfill the time requirement. The disadvantage is that every system would need a super computer, which is expensive and uses a lot of energy.

In [1] the largest computational part of the Volume Reconstruction algorithm is optimized for an Intel dualcore Xeon 5140 Woodcrest running at 2.3 GHz and a Nvidia GeForce 8800 GTX. The results showed a small advantage for the Intel processor. To get near the target time of fifteen minutes, 88 processors would be needed. The Intel processor achieved about 2% of its peak performance. The Nvidia GPU uses less than 1% of its peak performance. A streaming based FPGA implementation might achieve better results.

## 2. Problem analysis

#### 2.1. Finite Element Method

#### 2.1.1. Introduction

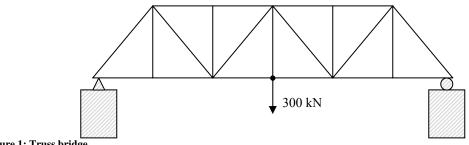

As explained in the previous chapter the Finite Element Method (FEM) can be used to analyze all kinds of physical processes. The physical processes are represented with models. One of the examples often used to explain the Finite Element Method is the determination of stress and the bending of a truss bridge.

Figure 1: Truss bridge

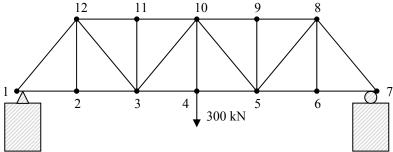

The idea of FEM is to divide the mathematical model into a finite number of elements to construct a discrete model. For the discrete model of the truss bridge only one simple element has to be used. This simple element is the 2-node truss element (also known as bar). Figure 2 plots the discrete model of the truss bridge.

Figure 2: Discrete model of truss bridge

Each intersection of lines has become a node and every line is an element. The discrete model has 12 nodes (numbered from 1 to 12) and 21 elements. With some formulas it is easy to determine the individual reaction of the simple elements. By combining the individual reactions, the reaction of the complete truss bridge can be determined. The combined individual reactions result in a matrix, referred as system or stiffness matrix K. The size of the system matrix K depends on the number of nodes and the dimension used. The truss bridge is modeled in two dimensions with 12 nodes. This means that the size of the system matrix becomes 24 by 24, for each node there is an x and y component.

Within FEM the system that has to be solved is K  $\mathbf{u} = \mathbf{f}$ . The meaning of vector  $\mathbf{u}$  and vector  $\mathbf{f}$  depends on the problem modeled. For mechanics the vector  $\mathbf{u}$  represents the nodal displacement and vector  $\mathbf{f}$  represents the nodal forces. Without going into detail the vector  $\mathbf{f}$  is known but the vector  $\mathbf{u}$  is unknown.

#### 2.1.2. System Matrix

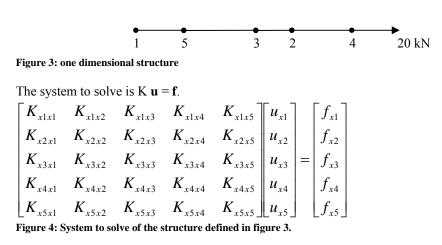

Consider the following one-dimensional problem.

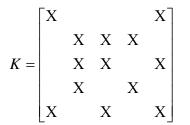

The force on a node only depends on the displacement of de node itself and the displacement of its neighbors. Thus the force on node one depends on the displacements of the node itself and the displacement of node five. The force on node two depends on the displacement of the node itself, node three and node four. Figure 3 represents the system matrix of the structure defined in figure 3. X indicates a non-zero value.

Figure 5: System matrix K of structure defined in figure 3.

The system matrix K in general has some important properties.

• The system matrix is sparse.

As seen in the example the force on a node only depends on its neighbors. The discrete models of real problems have usually more than 1,000 nodes while the number of neighbors lies in the order of ten. Meaning on average only 1% of the values are non-zero values. This results in a sparse matrix.

• The system matrix is symmetric.

Consider figure 3. The distance and the material of the element between node one and node five determine the value of  $K_{x1x5}$ . This value is the relation between the displacement of node five and the force on node one. Within the system matrix there is another value that represents the same element:  $K_{x5x1}$ . Thus for each element there are two values in the system matrix, one above and below the main diagonal.

• The system matrix can be reordered such that all non-zero values lie in a relatively small band. Reordering is covered in chapter 2.1.3.

### 2.1.3. Reordering

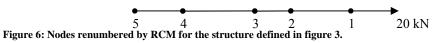

The numbering of the nodes is not fixed and can be chosen freely. The numbering of the nodes influences the position of the non-zero values in the system matrix K. For very large matrices a band matrix can have a great advantage. Common reordering methods to reduce the bandwidth are Cuthill McKee (CM) and reversed Cuthill McKee (RCM). RCM renumbers the nodes of the example problem in the following way.

The renumbered nodes result in the system matrix of figure 7.

Figure 7: System matrix of structure defined in figure 6.

Figure 5 and figure 7 represent both the same problem while their shape is completely different. For large system matrices a relative small band can have a large advantage.

#### 2.1.4. Solvers

To solve the system K  $\mathbf{u} = \mathbf{f}$ , two types of solvers can be used, direct and iterative. A direct solver will factorize the system matrix. Factorizing a large sparse matrix often yields in a dense matrix and is therefore impractical. Iterative solvers do not factorize the system matrix and are therefore preferred for large models. The Conjugate Gradient (CG) method is an iterative solver often used by FEM. The FEM used in the Volume Reconstruction algorithm also uses the CG algorithm.

#### 2.2. Conjugate Gradient method

#### 2.2.1. Introduction

The Conjugate Gradient method is an iterative linear equation solver. The major advantage of an iterative solver is that the matrix does not have to be factorized. Factorizing very large sparse matrices often yields in dense matrices. Handling very large dense matrices is impractical because of the storage requirements and the computational complexity.

The conjugate gradient method is an iterative method to calculate the vector  $\mathbf{x}$  in the system  $A^*\mathbf{x} = \mathbf{b}$  where matrix A and vector  $\mathbf{b}$  are given. Matrix A must be square, symmetric and positive-definite.

Although the intuition behind CG is discussed extensively in [3], it will be discussed briefly here. Because the idea behind Steepest Descent and Conjugate Gradient is discussed in a very intuitive way in [3] this explanation has the same outline. Also the same examples and figures as in [3] will be used. Another description of CG can be read in [4].

Another algorithm that solves the same system as CG is Steepest Descent. Both algorithms look very similar, the main difference is that CG converges faster. CG can be explained more easily from the explanation of Steepest Descent.

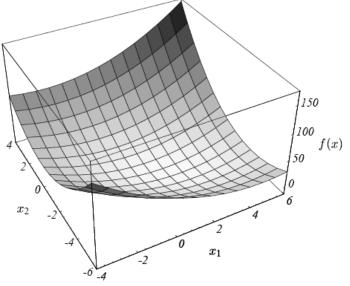

Steepest Descent and the Conjugate Gradient try to minimize the quadratic form of A\***x**=**b**. The quadratic form is:

$$f(\mathbf{x}) = \frac{1}{2}\mathbf{x}^T A\mathbf{x} - \mathbf{x}^T \mathbf{b}$$

It can be proven that if A is positive definite and symmetric, minimizing f is the same as solving A\*x=b.

In [3] the following sample problem is used to explain the ideas of SD and CG.

$$A = \begin{pmatrix} 3 & 2 \\ 2 & 6 \end{pmatrix}, \mathbf{b} = \begin{pmatrix} 2 \\ -8 \end{pmatrix}$$

The quadratic form  $f(\mathbf{x})$  of the example is plotted in the following figure.

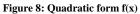

The lowest point in figure 8 is the solution of the system  $A^*x = b$ . In this sample problem that is x = [2, -2]. This can be seen more easily in the contour plot (figure 9).  $x_2$

Figure 9: Contour plot of f(x)

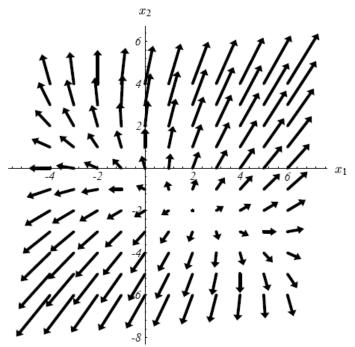

Figure 10: Gradient of f'(x)

De derivative of  $f(\mathbf{x})$  is defined as  $f'(\mathbf{x})$  and equals  $f'(\mathbf{x}) = A\mathbf{x} - \mathbf{b}$ The gradient points in the direction of the steepest increase of  $f(\mathbf{x})$ .  $f(\mathbf{x})$  can be minimized by setting  $f'(\mathbf{x})$  to zero.

#### 2.2.2. Steepest Descent

The Steepest Descent method starts at an arbitrary point  $\mathbf{x}_{(0)}$  and every iteration a step is taken to get closer to the solution of A\***x=b**. Every iteration will result in a better approximation. The number of iterations will depend on the maximum error term specified and the speed of converge.

Every iteration i a step is taken in the direction where  $f(\mathbf{x}_{(i)})$  decreases most quickly. This direction is the opposite of  $f'(\mathbf{x}_{(i)})$ . This is equal to  $-f'(\mathbf{x}_{(i)}) = \mathbf{b} - A\mathbf{x}_{(i)}$ , which is defined as the residual. The residual can be described as the direction of the steepest descent.

For the example described above the starting point  $\mathbf{x}_{(0)} = [-2, -2]$  is chosen. Every iteration a step is made along the direction of the steepest descent. This results in the following formula for the first iteration:  $\mathbf{x}_{(1)} = \mathbf{x}_{(0)} + \alpha \mathbf{r}_{(0)}$ , where  $\alpha$  determines the length of the step taken. In [3]  $\alpha_i$  is defined

as

$$\alpha_{(i)} = \frac{\mathbf{r}_{(i)}^T \mathbf{r}_{(i)}}{\mathbf{r}_{(i)}^T A \mathbf{r}_{(i)}}$$

.

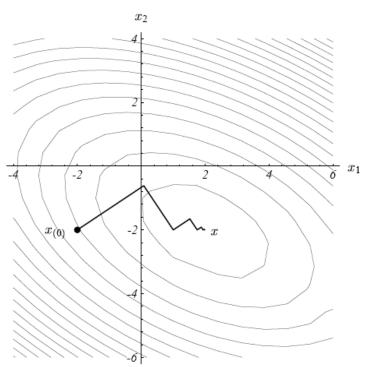

Figure 11: Convergence of Steepest Descent

In figure 11 the convergence of steepest descent for the example problem is shown. In [3]  $\alpha_i$  is difined such that the solid lines (in the direction of steepest descent) are orthogonal to each other.

Summarizing the Steepest Descent method is described as:

$$\mathbf{r}_{(i)} = \mathbf{b} - A\mathbf{x}_{(i)}$$

$$\alpha_{(i)} = \frac{\mathbf{r}_{(i)}^T \mathbf{r}_{(i)}}{\mathbf{r}_{(i)}^T A \mathbf{r}_{(i)}}$$

$$\mathbf{x}_{(i+1)} = \mathbf{x}_{(i)} + \alpha \mathbf{r}_{(i)}$$

The method of Steepest Descent as described above requires two matrix-vector multiplications per iteration. By using another formula to compute the residual, only one matrix-vector multiplication is needed.

$$\mathbf{r}_{(0)} = \mathbf{b} - A\mathbf{x}_{(0)}$$

$$\mathbf{r}_{(i+1)} = \mathbf{r}_{(i)} - \alpha_{(i)}A\mathbf{r}_{(i)}$$

This way, the matrix-vector product  $A\mathbf{r}_{(i)}$  is used for calculating both  $r_{(i)}$  and  $\alpha_{(i)}$ .

#### 2.2.3. Conjugate Gradient

The idea behind Conjugate Gradient is the same as behind Steepest Descent but instead of multiple steps in the same direction, steps in CG are never in the same direction. Steps in CG are not orthogonal to each other but conjugate.

Conjugate Gradient algorithm:

$$\vec{\mathbf{d}}_{(0)} = \vec{\mathbf{r}}_{(0)} = \vec{\mathbf{b}} - A\vec{\mathbf{x}}_{(0)}$$

$$\alpha_{(i)} = \frac{\vec{\mathbf{r}}_{(i)}^T \vec{\mathbf{r}}_{(i)}}{\vec{\mathbf{d}}_{(i)}^T A \vec{\mathbf{d}}_{(i)}}$$

$$\vec{\mathbf{x}}_{(i+1)} = \vec{\mathbf{x}}_{(i)} + \alpha_{(i)} \vec{\mathbf{d}}_{(i)}$$

$$\vec{\mathbf{r}}_{(i+1)} = \vec{\mathbf{r}}_{(i)} - \alpha_{(i)} A \vec{\mathbf{d}}_{(i)}$$

$$\beta_{(i+1)} = \frac{\vec{\mathbf{r}}_{(i+1)}^T \vec{\mathbf{r}}_{(i+1)}}{\vec{\mathbf{r}}_{(i)}^T \vec{\mathbf{r}}_{(i)}}$$

$$\vec{\mathbf{d}}_{(i+1)} = \vec{\mathbf{r}}_{(i+1)} + \beta_{(i+1)} \vec{\mathbf{d}}_{(i)}$$

In the context of this thesis it is to complex to describe the CG algorithm completely, see [3] for more details.

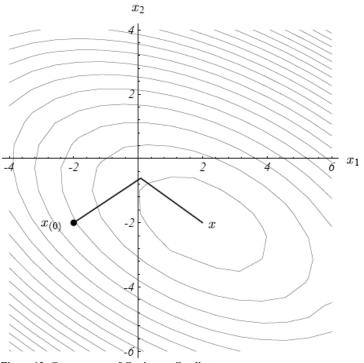

Figure 12: Convergence of Conjugate Gradient

In figure 12 the Convergence of Conjugate Gradient for the example problem is plotted. In general the number of iterations to converge is equal to the length of the vector x. In the sample problem the length of x is two and as can be seen in figure 12 the number of iterations is also two. This is regardless of the position of the starting point.

Unfortunately round off errors (because of floating point operations) result in accuracy loss. In chapter nine of [3] a convergence analysis of CG is done.

### 2.2.4. Complexity analysis

Variable  $\alpha$  and  $\beta$  are scalars, **d**, **r** and **x** are vectors and A is a matrix. There is one initial step which requires a sparse matrix-vector multiplication unless the initial vector **x** only contains zeros. The computation cost of the iterative part can be divided into different classes:

- One sparse matrix-vector multiplication

- Two inner products

- Three scalar vector multiplications

- Three vector additions/subtractions

The properties of the matrix have great impact on the computational complexity. The number of MAC operations for the SMVM is equal to the number of non-zeros. For dense matrix vector multiplication the number of multiplications is equal to the size of the matrix and does not depend on the number of non-zeros. The more non-zeros, the more dominant the SMVM operation is. In case of the Volume Reconstruction algorithm the SMVM takes 80% of the total required computational complexity of the CG algorithm.

#### 2.3. Sparse Matrix-vector multiplication

In the conjugate gradient algorithm one of the operations is a sparse matrix-vector multiplication:  $A^*x = y$ , A is a sparse matrix, x is a dense vector and y is the dense result vector. This sparse matrix-vector multiplication has to be calculated every iteration of the CG algorithm. Matrix A does not change during the algorithm only vector x changes.

#### 2.3.1. Compressed Row Storage Format

The storage of a dense matrix with n rows and m columns requires the storage of n \* m elements. In case of sparse matrices such storage scheme is very inefficient because most of the elements are zero. There are several other schemes to store sparse matrices. These schemes have one thing in common; they only store the non-zero elements. To prevent that the structure gets lost also the indices of the non-zero elements must be stored. The aim of these schemes is that multiplications with zero are not executed. Only the non-zero elements are multiplied with the corresponding elements of the vector. The corresponding elements of the vector can be accessed directly because the indices of the non-zero elements are stored. The most used format to store sparse matrices is the Compressed Row Storage (CRS) format.

CRS uses three vectors to store a sparse matrix. Vector 'val' contains all the non-zero elements. The order in which they are stored is row-wise. The vector 'col' contains the column index of each element stored in vector 'val'. The vector row indexes the start of a new 'row' within the 'val' and 'col' vectors. Notice that there is an additional index in the 'row' vector to indicate the end of the last row.

Example:

```

A = \begin{pmatrix} 1 & 0 & 0 & 2 \\ 0 & 0 & 3 & 0 \\ 0 & 4 & 5 & 0 \\ 0 & 0 & 0 & 6 \end{pmatrix}

val = (1 2 3 4 5 6)

col = (1 4 3 2 3 4)

row = (1 3 4 6 7)

```

Figure 13: Storage of matrix in Compressed Row Storage format.

```

With the following pseudo code the SMVM of a sparse matrix in CSR format can be computed:

for (int i=1; i =< n; i++)

for (int j = row(i); j < row(i+1); j++)

y(i) = val(j)*x(col(j)) + y(i);

```

n is the number of rows of the matrix

### 2.4. FEM Matrices

In chapter 2.1.2 the general properties of the system matrix were given. These general properties are:

- The system matrix is sparse.

- The system matrix is symmetric.

- The system matrix can be reordered such that all non-zero values lie in a relative small band.

Although the general properties hold for all the system matrices there can be quite some differences between them. At [11] a collection of system matrices is maintained. Implementations for SMVM are often benchmarked with these matrices. Besides these matrices this project focuses on the system matrix of the Volume Reconstruction algorithm, described in [1].

There is a lot of variation in the performance of current implementations for SMVM. These variations in performance are a direct result of the variations of the system matrices. This chapter addresses the differences in system matrices.

To classify the system matrices the following properties will be used:

- Size of the matrix (n \* n)

- Number of non-zeros

- Sparsity of the matrix

This value indicates the number of non-zeros compared to the number of entries.

• Bandwidth

Maximum difference in column index between the non-zero elements of one row.

• Relative bandwidth

Ratio between n and the bandwidth.

• Sparsity of the band

Indication on the number of non-zeros compared to the number of entries of the band.

#### 2.4.1. Example of a regular system matrix

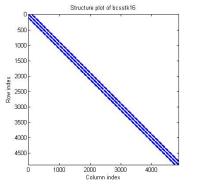

Figure 14: Structure plot of a regular system matrix

Figure 14 is a structure plot of matrix bcsstk16 which can be found at [11]. As can be seen in the figure, the matrix has a regular structure.

The regular matrix bcsstk16 has the following properties:Size4,884 \* 4,884Non-zeros290,378Sparsity1.2 %Bandwidth277Relative bandwidth5.7 %Sparsity of the band21.5 %Table 1: Properties of regular system matrix bcsstk16

### 2.4.2. Example of a irregular system matrix

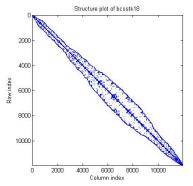

Figure 15: Structure plot of matrix bcsstk18

The matrix bcsstk18 (can be found at [11]) has the following properties:

| Size                                          | 11,948 * 11,948 |  |  |

|-----------------------------------------------|-----------------|--|--|

| Non-zeros                                     | 149,090         |  |  |

| Sparsity                                      | 0.1 %           |  |  |

| Bandwidth                                     | 2,483           |  |  |

| Relative bandwidth                            | 20.8 %          |  |  |

| Sparsity of the band                          | 0.5 %           |  |  |

| Table 2: Properties of system matrix bcsstk18 |                 |  |  |

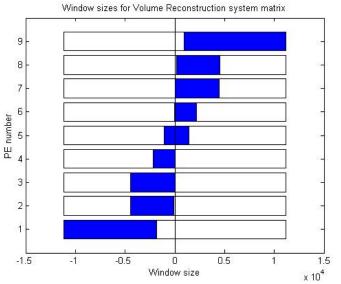

## 2.4.3. System matrix of the Volume Reconstruction algorithm

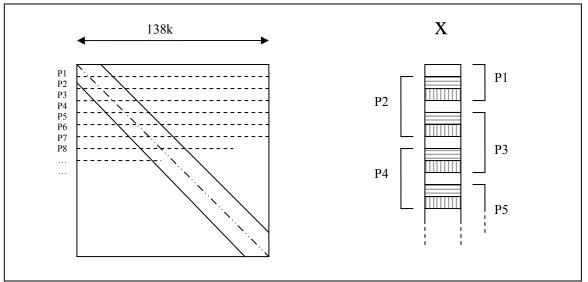

Figure 16: Structure plot of the Volume Reconstruction system matrix

| Size                                                       | 138,324 * 138,324 |  |  |

|------------------------------------------------------------|-------------------|--|--|

| Non-zeros                                                  | 2,460,562         |  |  |

| Sparsity                                                   | 0.013 %           |  |  |

| Bandwidth                                                  | 22,393            |  |  |

| Relative bandwidth                                         | 16.2 %            |  |  |

| Sparsity of the band                                       | 0.079 %           |  |  |

| Table 3: Properties of Volume Reconstruction system matrix |                   |  |  |

Figure 16 might give the impression that the sparsity of the band is quite high (high percentage). Figure 17 is a zoomed structure plot. From this figure it is clear that the sparsity of the band is low.

Figure 17: Zoomed structure plot of the Volume Reconstruction system matrix

The most important difference between the matrices described above, is the sparsity of the band. The most implementations of the SMVM achieve a reasonable performance for the regular system matrices as given in chapter 2.4.1. For the irregular system matrices the performance drops on average a factor 5 see [10]. This project focuses on the system matrix of the Volume Reconstruction algorithm. A good implementation for the SMVM will handle irregular system matrices almost as well as the regular system matrices.

## 2.5. Field Programmable Gate Array

There are several hardware architectures to perform complex tasks. One of these hardware architectures is a Field Programmable Gate Array (FPGA). FPGAs are devices that have a high performance potential while maintaining high flexibility.

An FPGA is a device which has a lot of components. Often there are a lot of simple components such as 4input LUTs (Look Up Tables) to implement for example AND, XOR, NOR or user defined functions, which are often combined with a flipflop. More complex components are for example the dedicated 18\*18 bit multipliers and the dedicated memory blocks.

The components are connected through a programmable interconnect. Complex functions can be implemented by combining the standard components which is done by configuring the FPGA. An FPGA design is thus represented by a configuration file. The same FPGA can be used for different algorithms just by loading another configuration file. Further, the time to market of an FPGA design is short compared to an ASIC design.

Often it is not so hard to implement an algorithm onto an FPGA, developing an implementation that uses the full potential of the FPGA is however difficult.

#### 2.5.1. MAC unit

For digital signal processing algorithms there are two common number representations, fixed point and floating point. Fixed point has a low hardware cost but a low precision while floating point is more complex but has a high precision. For most digital signal processing algorithms, fixed point numbers have a sufficient precision. Because the hardware for fixed point operations is much simpler compared with floating point most of the digital signal processing algorithms are executed on fixed point hardware. Almost all the DSPs use fixed point numbers.

The Volume Reconstruction algorithm requires a high accuracy with a large range, fixed point hardware is thus not an appropriate choice. Within floating point, 32 and 64 bit are common widths. The Conjugate Gradient (CG) algorithm converges faster when higher accuracy is used [1]. The difference between the number of iterations CG needs to converge when using 32 or 64 bit floating point numbers is quite significant. Simulations have shown that the difference is roughly a factor two. The difference in the converge rate is caused by rounding off results. Rounding off numbers to 32 bit floating point numbers results in precision loss compared to 64 bit floating point numbers. The speedup in the number of iterations might justify the extra hardware cost of 64 bit floating point numbers compared to 32 bit floating point numbers see [1].

In [7] a 64 bit floating point MAC unit for an FPGA is presented. This MAC unit exploits the dedicated 18x18 bit multipliers that are present in the order of hundreds on current FPGAs. The 64-bit MAC unit presented in [7] uses nine 18x18 multipliers and has twelve pipeline stages to achieve high performances. The largest FPGA of the Virtex-II pro family from Xilinx, the XC2VP100 (in this project the target FPGA), can hold 31 of these 64-bit floating point MAC units running at 170 MHz (speed grade -6).

### 2.5.2. Processing Element

As the name already does suggests, a Processing Element (PE) has to process something. It has to perform an operation on data. In case of SMVM the only operations are multiplications and additions. From this property it follows that a PE at least has to be able to compute a multiplication or an addition, but much more complex designs are possible. A PE might for example also perform a combined multiply-accumulate instruction. Other variations are the number of inputs. There are at least two operands required for both the multiply and accumulate instructions, but this might be extended to for example eight operands. It depends completely on the algorithm what kind of combination of PEs gives the best performance. The choice is to have either a lot of simple PEs, a few complex PEs or a combination of simple and complex PEs.

Usually a design can be split into a number of PEs and a common part. The common parts are for example memories shared by PEs, busses shared by PEs, communication between PEs, etcetera. Some parts are only used by one PE. These parts are thus related to a specific PE. Often it is beneficial to have a memory block that is only used by one PE. The same holds for communication busses between memory and the MAC unit.

At this moment the PEs are specified to have at least a MAC unit as presented in [7]. This MAC unit has three operands, is fully pipelined (four multiplication and eight adder pipeline stages) and every clock cycle a MAC result can be computed. These assumptions result in a relatively simple PE which might result in a relatively high number of PEs per FPGA. The size of the memories of a PE depends on the algorithm and will be specified in the following chapters

# 3. Design requirements

In all known SMVM implementations the limiting factor is the available memory bandwidth. The complete matrix cannot be stored on the FPGA itself. The matrix has to be stored in external memory. Thus to compute the SMVM, the matrix has to be transferred from external memory to the FPGA at least once. The main target of the design is to use the available memory bandwidth as efficiently as possible.

The implementation of the SMVM thus has the following requirements:

- The design has to keep up with the memory interface; it should not become the bottleneck.

- The overhead that might be needed to schedule the SMVM must be kept to a minimum.

- Most of the memory bandwidth must be used to transfer the matrix and not to transfer overhead.The design has to be scalable in the available memory bandwidth.

- More bandwidth should mean a faster transfer and thus a faster computation. This implies that the utilization of the Processing Elements has to be reasonably high.

- The design has to compute the SMVM of regular and irregular system matrices evenly well.

## 4. Previous work

There are many papers written on the implementation of Sparse Matrix-Vector Multiplication. Within the research field of SMVM there are two main directions. One direction tries to make a fast implementation on processors (GPP, Cell processor, VLIW processors); the other direction tries to make a fast implementation on FPGAs. This chapter addresses three FPGA implementations with their strong and weak points.

### 4.1. Striping based implementation

A recent paper about a SMVM implementation is [10]. Their implementation uses a stripe method which was introduced by R. Melhem in [9]. The stripe method is discussed in chapter 4.4.

Strong points:

• Streaming based implementation

Weak points:

- Utilization of implementation differs a lot because of the differences of the FEM matrices.

- They never address the problems their method has and how they solved it.

- The performance of their implementation is not linear in the available memory bandwidth as can be seen in [12].

- They used benchmark matrices from [11], but forgot to index them.

#### 4.2. Preprocessor implementation

Another recent paper is [13], this implementation uses a preprocessing stage to compute the SMVM with a high utilization of the PEs. A major part of their implementation is discussed in chapter 5.

Strong points:

• High utilization of the PEs

Weak points:

- Complete matrix stored on the FPGA. Matrices that do not fit on one FPGA need multiple FPGAs.

- Complete result vector stored on FPGA.

- Implementation computes  $\mathbf{y} = \mathbf{A}^p * \mathbf{x}, p \ge 1$ .

### 4.3. Straight forward implementation

A straight forward implementation is introduced in [14]. This method computes the SMVM directly with the standard CSR format.

Strong points:

- No preprocessing required

- Simple partial results adder implementation

- No overhead

- Works evenly well for regular and irregular system matrices

Weak points:

- High utilization difference between multiplier and partial result adder (eight adders and only one multiplier)

- The performance of their implementation is not linear in the available memory bandwidth (because of the use of only one multiplier).

## 4.4. Stripe method

The use of a systolic array to compute the matrix vector multiplication where the matrix has a dense band has proved its use in [8]. In [9] a method is described to compute the matrix vector multiplication where the matrix has a sparse band. The method described in [9] achieves higher efficiencies for sparse band matrices compared to [8].

Consider a sparse matrix vector multiplication  $A^*x = y$ . A is a sparse matrix with bandwidth b, x is a dense vector and y is the dense result vector.

In [8] to compute the matrix vector multiplication, b processing elements (PEs) are required. Each PE multiplies a straight-diagonal of A with the vector  $\mathbf{x}$ . The efficiency of this approach is determined by the sparsity of the band b. A dense band means a high efficiency and a sparse band will result in a low efficiency. As explained in chapter 2.4 the band of sparse matrices is often sparse.

R. Melhem explained in [9] a method to improve the low efficiency for Sparse Matrix-Vector Multiplication (SMVM) if the band is sparse by lowering the number of PEs. This is done by covering the non-zero elements of the matrix by stripes. The collection of all the stripes required to cover all the non-zero elements is called a stripe cover. The number of PEs is equal to the number of stripes needed to cover all the non-zero elements.

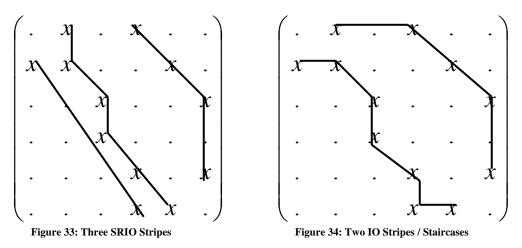

### 4.4.1. Stripes

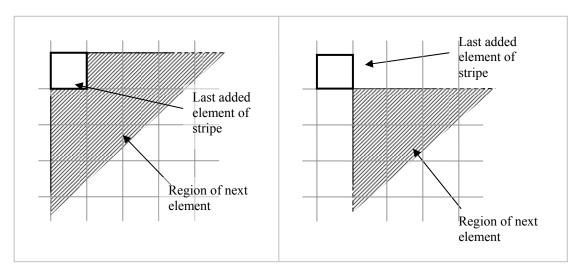

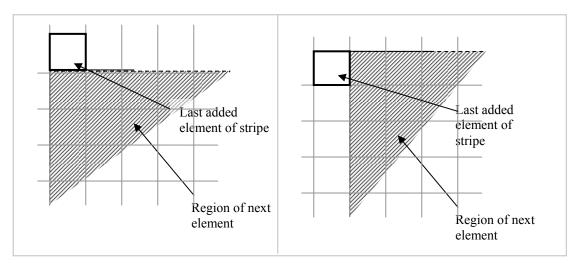

There are various ways to construct a stripe through a matrix for the coverage of the non-zero elements. In [10] a classification is given, increasing order (IO), strictly increasing order (SIO), strict-column increasing order (SCIO) and strict-row increasing order (SRIO). These classifications can be explained with regions. Each stripe is constructed in an iterative way, every iteration an element is added to the stripe.

Figure 18: Region of IO Stripes

Figure 19: Region of SIO stripes

Figure 20: Region of SRIO stripes

Figure 21: Region of SCIO stripes

R. Melhem uses SIO stripes in [9], SRIO stripes are used in [10] and IO stripes are used in [6]. SCIO stripes are not used because they do not have advantages over the other striping schemes.

The stripes in [9] are SIO and have thus the following properties:

- A stripe contains at most one element of every row.

- A stripe contains at most one element of every column.

- From the first property it follows that the longest stripe covers at most n elements.

- Because of property one the elements on the same row are covered by different stripes.

The last property gives a lower bound on the number of stripes. The lower bound of the number of stripes is equal to the maximum number of non-zero elements on a row of the matrix.

In [10] a small modification on the region to construct stripes is proposed. The region is extended to be able to cover non-zero elements in the same column. This leads to SRIO stripes, which have almost the same properties as SIO stripes. The only difference is that a SRIO stripe can contain multiple elements of the same column.

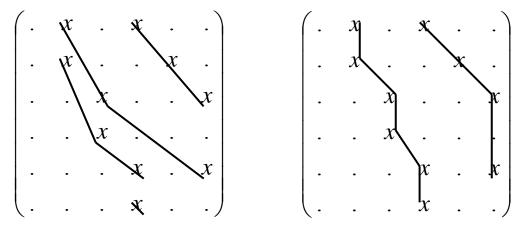

Examples:

Figure 22: Four SIO Stripes

Figure 23: Two SRIO Stripes

The number of SRIO stripes is less or equal to the number of SIO stripes to cover all the non-zero elements [10] although they have the same lower bound on the number of stripes. Only SRIO stripes will be covered in the next chapters because they can give better results, see [10].

#### 4.4.2. Construction of SRIO stripes

There are several ways to construct SRIO stripes. In [10] two types are described, top-down striping (TDS) and bottom-up striping (BUS). Both methods return the same number of stripes thus it is sufficient to only explain TDS. On each row a number of non-zero elements need to be covered by a stripe. TDS starts at the last non-zero element of the first row. The last non-zero element of a row is the non-zero element with the highest column index of that row. The non-zero element of the starting point is assigned to the first stripe. The second last element of the first row is assigned to the second stripe. These steps are repeated until the first element of the first row is assigned to a stripe.

TDS continues at the last element of the second row. If the column index of the element is larger or equal to the column index of the first stripe, it is assigned to the first stripe else it tries to assign it to a stripe with a column index smaller or equal to the column index of the element. The same is done with the second last element of the second row, etcetera.

TDS assigns thus the non-zero elements to stripes from top to bottom and from right to left. Right to left means from the highest column index to the lowest. The stripes are thus constructed like a cheese-slicer would slice an apple.

Figure 24: Stripes constructed with TDS method

### 4.4.3. Systolic array

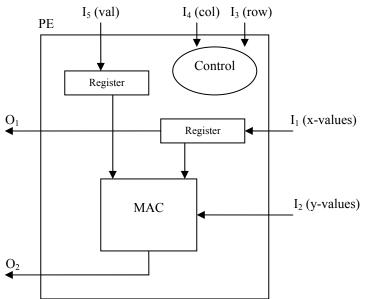

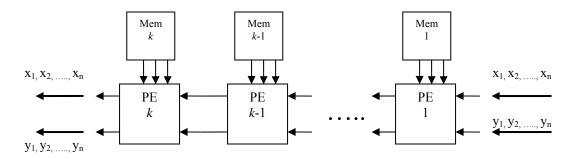

The method described in [10] uses a number of processing elements (PEs) together forming a systolic array. Each PE is able to compute a multiply accumulate.

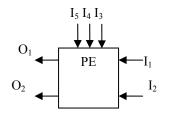

Figure 25: Processing element of the systolic array

Figure 26: Systolic array for SMVM

Each processing element has five inputs and two outputs.

The input  $I_1$  is for the x-values,  $I_2$  for the y-values and the group  $I_3$ ,  $I_4$ ,  $I_5$  for the stripe values (row index, column index and value). Each PE has a local memory to hold the values of the stripe it processes. Vector **x** and **y** stream through the system from right to left. In the initial case all the y-values are zero. Between PEs the y-values are partial results and after the last PE the actual values are available. Communication between PEs is done through FIFO queues.

Each processing element processes a stripe. The first stripe is processed by the first PE, the second stripe by the second PE, etcetera. Figure 24 indicates the numbering order for the stripes, figure 26 indicates the numbering order for the PEs. The number of PEs is thus equal to the number of stripes to cover all the non-zero elements. The complete result vector **y** streams through the system once. A PE can either compute a partial result and add it to an element of **y** or pass it to the FIFO of the next PE, this depends on the stripe the PE is processing. If for example a stripe covers an element on the first row, the PE that processes the stripe will compute a partial result and add it to the first element of the result vector **y** will be passed on without computing and adding a partial result. To compute a partial result a multiplication of two values is required, adding the partial result to an element of **y** takes an addition of two values. Each PE thus requires a MAC unit to be able to perform these operations.

#### 4.4.4. Utilization

To estimate the best case utilization of the MAC units the assumption is made that passing on an element to the next PE with or without computing and adding a partial result takes one clock cycle. This assumption implies that the MAC unit is fully pipelined. The result of the assumption is that the time to stream the result vector  $\mathbf{y}$  through the system in the best case is equal to the length of the result vector  $\mathbf{y}$ . In case of a matrix A with size n x n, n clock cycles are needed to stream the result vector  $\mathbf{y}$  through the system regardless of the amount of partial results.

Suppose k stripes are required for the coverage of all the non-zero elements of a matrix. The systolic array would contain k PEs. In the ideal case  $n^*k$  partial products could be computed and added to the result vector **y**. The number of partial products is equal to the number of non-zero elements. The utilization of the best case scenario of the system can be computed with the formula:  $nnz/(n^*k)$ .

nnz is the number of non-zero elements.

n is the size of the vector **y**.

k is the number of stripes and equal to the number of processing elements.

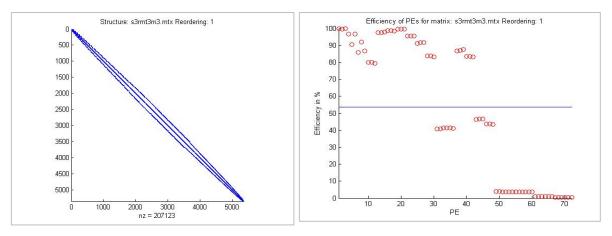

The best case utilization of the MAC units for the SMVM with a stripe cover varies greatly as can be seen in [10]. The overall utilization can be as high as 80% but also as low as 3%. This difference is caused by the sparsity and the irregularity of the band of the matrix. To support this, three examples are given. The first two examples can be downloaded from the Matrix Market website [11].

Example one:

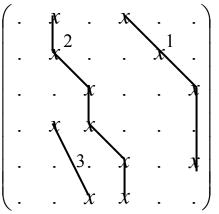

| Matrix name:       | s3rmt3m       |

|--------------------|---------------|

| Size:              | 5,357 x 5,357 |

| Non-zero elements: | 207,123 0.72% |

| Stripes:           | 72            |

Figure 27: Structure plot of matrix s3rmt3m

Figure 28: Utilization of PEs for matrix s3rmt3m

The solid line drawn in figure 28 represents the efficiency of the total design. In this case the overall efficiency is thus 54%.

#### Example two:

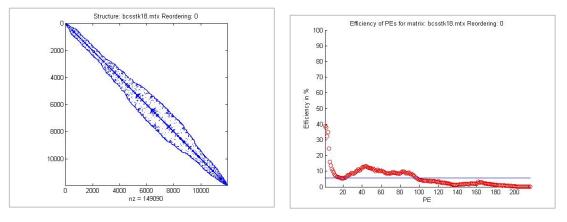

| Matrix name:       | bcsstk18.mtx    |

|--------------------|-----------------|

| Size:              | 11,948 x 11,948 |

| Non-zero elements: | 149,090 0.1%    |

| Stripes:           | 216             |

#### Figure 29: Structure plot of matrix bcsstk18

Figure 30: Utilization of PEs for matrix bcsstk18

Because of the irregularity and sparsity within the band of matrix bcsstk18, the overall efficiency is only 5%.

Example three:

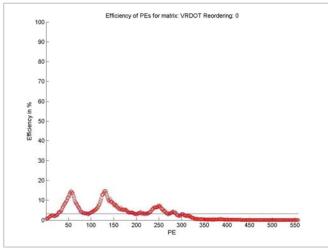

| Matrix name:       | Volume Reconstruction matrix |

|--------------------|------------------------------|

| Size:              | 138,324 x 138,324            |

| Non-zero elements: | 2,460,562 0.013%             |

| Stripes:           | 555                          |

Figure 31: Utilization of PEs for Volume reconstruction matrix

The overall utilization for the Volume Reconstruction matrix is about 4%.

#### 4.4.5. Cause of low utilization

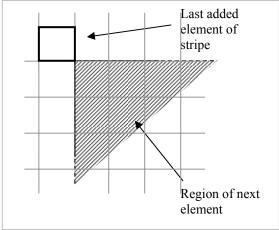

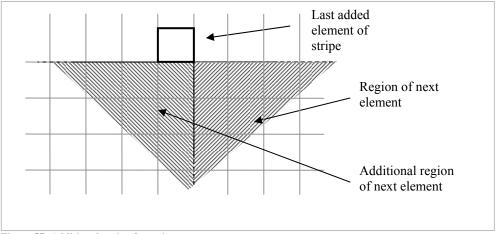

The number of non-zeros a stripe covers directly influences the utilization of the PEs. To understand why the stripe method results in a low utilization for certain matrices, the construction process of a stripe has to be reviewed.

The following situation occurs frequently in the construction of stripes.

$$\begin{pmatrix} \cdots & \cdots & e_1 \\ \cdots & e_2 & \cdots \\ \cdots & e_3 & \cdots \\ \cdots & e_4 & \cdots \\ \cdots & \cdots & e_5 \end{pmatrix}$$

Figure 32: Part of a matrix

Figure 32 represents a part of a matrix,  $e_1$  till  $e_5$  represent non-zero elements. At a certain point stripe  $s_1$  is constructed. The construction of a stripe is iterative; every iteration a non-zero element is added. Suppose the last added non-zero element added to  $s_1$  is  $e_1$ . Because of the "construction rules" (region of next element)  $e_2$  till  $e_4$  cannot be covered anymore by  $s_1$ . After covering  $e_1$  the only element that could be covered by the same stripe is  $e_5$ . This yields in a low utilization of the PE that processes stripe  $s_1$ , utilization of  $s_1 = 2/5 = 0.4$ .

The situation explained above occurs often with matrices of real problems. In the example above there are only three rows between  $e_1$  and  $e_5$ . With matrices of real problems the distance between two elements covered by a stripe are a lot larger (between 100 and 1000 rows). The utilization of these stripes is often less then 1%.

#### 4.4.6. Conclusion

The problem with a SMVM is to exploit the sparsity of the matrix. In this research field a number of methods are proposed to accomplish this. The use of a systolic array combined with a stripe cover is one of these methods. In [10] and in this report, analysis on the utilization of a stripe cover is done for several matrices. For sparse band matrices with a regular structure the method can achieve a high utilization but for irregular sparse band matrices the utilization is significantly lower. As seen in chapter 2.4.3, the band of the Volume Reconstruction matrix is also sparse and irregular. Analysis showed a best case utilization of 4% using SRIO stripes.

### 4.5. Parallel Matrix Communication Network

In [6] a modification on the ideas in [9] is proposed. This modification leads to Parallel Matrix Computation Network (PMCN). This method also uses a systolic array to compute the SMVM. In chapter 4.4.1 of this report a classification for stripes is given.

In the original idea of R. Melhem in [9], SIO stripes are used. In chapter 4.4 the modification of using SRIO stripes proposed in [10] is discussed. This modification leads to better results.

PCMN is also a modification of the stripe scheme. Instead of using SIO stripes, IO stripes are used. These IO stripes are also known as staircases. Instead of a stripe cover a staircase cover is used.

Examples:

In PCMN, the number of PEs is equal to the number of staircases. In general the number of staircases is lower than the number of SRIO stripes. The maximum length of a SRIO stripe is n (maximum number of non-zero it can cover), the maximum length of a staircase is 2\*n-1.

In [6] an analysis is done to compare the original idea of R. Melhem to PMCN. In their analysis they defined a "global cycle" to measure the number of "time steps". With these definitions they prove that PCMN is "superior to the algorithm of Melhem in terms of hardware requirements, while using exactly the same number of time steps". The quote is taken from their abstract and brings every reader in excitement. Unfortunately the definitions "global cycle" and "time steps" are very vague and are not related to any possible hardware implementation. One of the questions that immediately arise is why the increased maximum length of a staircase (twice the maximum length of a SRIO stripe) does not have any impact on the time needed to compute the SMVM. The efficiency of a PE, processing a stripe with maximum length n, is 100%. This implies that processing a staircase with maximum length of 2\*n-1 cannot be processed in the same time as processing a SIO stripe of maximum length n. The dependencies that arise when a staircase covers more than one non-zero element on a row introduces extra cycles. This effect is explained with an example in chapter 4.5.1.

#### 4.5.1. Parallel Matrix Computation Network - Example

Consider the SMVM of matrix A with vector **x**. Vector **x** contains the values A, B and C. The computation is represented in the following picture.

$$\begin{pmatrix} 1-2 & . \\ . & 3-4 \\ . & . & 5 \end{pmatrix} \begin{pmatrix} A \\ B \\ C \end{pmatrix} = \begin{pmatrix} y_1 \\ y_2 \\ y_3 \end{pmatrix} = \begin{pmatrix} 1A+2B \\ 3B+4C \\ 5C \end{pmatrix}$$

Figure 35: Example of SMVM with staircases

The application considered in this report requires floating point representation. To achieve high performance, floating point MAC units are usually pipelined. In [7] a possible design of a 12 stage pipelined MAC unit is presented. The use of 12 pipeline stages results in a delay of 12 cycles. Without dependencies the delay does not play a role in the performance of the system.

To compute the SMVM of figure 35, one staircase is needed. In the first stage the PE starts the computation of a partial result of  $y_1$ .

Cycle 1:  $y_1^2 = 1A + 0$

In the second stage it computes the second partial product of  $y_1$ . The partial product has to be added to the value of  $y_1$ . Thus the second stage can only start when the result of the first stage is available. Because the MAC unit has 12 pipeline stages, the second stage can not start before cycle 13.

Cycle 13:  $y_1 = 2B + y_1^2$

The same analysis can be done for then rest of the computations. Stage three can immediately start because there are no dependencies.

Cycle 14:

$$y'_2 = 3B + 0$$

Cycle 26:  $y_2 = 4C + y'_2$

Cycle 27:  $y_3 = 5C + 0$

In cycle 1 the first multiply accumulate is started and in cycle 27 the last one. In the same time the MAC unit could have started 27 multiply accumulates. For this example the efficiency of the MAC unit is only 18.5%.

#### 4.5.2. SIO Example

$$\begin{pmatrix} 1 & 2 & . \\ . & 3 & 4 \\ . & . & 5 \end{pmatrix} \begin{pmatrix} A \\ B \\ C \end{pmatrix} = \begin{pmatrix} y_1 = 1A + 2B \\ y_2 = 3B + 4C \\ y_3 = 5C \end{pmatrix}$$

Figure 36: Example of SMVM with SIO stripes

Stripe one is defined as the solid line, stripe two is defined as the dashed line. Processing element one processes stripe one and PE two processes stripe two. A detailed description of the systolic array can be found in chapter 4.4.3.

Timing analysis of the example for PE one: In the first clock cycle, PE one passes value A to PE two. Cycle 1: Pass value A to next PE. In the second clock cycle it starts the computation of a partial result of y<sub>1</sub>.

Cycle 2:  $y_1 = 2B + 0$

In the third clock cycle it starts the computation of a partial result of  $y_2$ .

Cycle 3:  $y_2^{,} = 4C + 0$

In the fourth clock cycle it passes on value  $y_3$ . Cycle 4: Pass value  $y_3$  to next PE.

Timing analysis of the example for PE two:

In the first stage of PE two it has to compute a partial result of  $y_1$ . PE two can only start this computation after it has received the partial result  $y_1$  from PE one. Thus PE two cannot start before cycle 14 (2+12).

Cycle 14:  $y_1 = 1A + y_1^2$

The second stage a partial result of  $y_2$  is computed. Because of the dependencies, this computation cannot start before cycle 15 (3+12).

Cycle 15:  $y_2 = 3B + y_2^{\prime}$ The last stage starts at cycle 16. Cycle 16:  $y_3 = 5C + 0$

To obtain the highest possible efficiency, the system continuously has to calculate SMVMs. This can be done by multiplying the matrix with multiple vectors. This optimization can be used in the overall algorithm because multiple columns have to be computed. Thus at cycle 5 PE one can start a new round to compute the SMVM with a new vector. This means that every four clock cycles a result vector is available. Within four clock cycles eight multiply accumulates could be computed by means of two PEs. For this example only five are computed. The efficiency for this example is thus 62.5%, which is a lot better than the staircase solution.

#### 4.5.3. Conclusion

PMCN is introduced by the inventors as a better method to compute SMVM than the method of Melhem. The analysis in [6] to support their claim is very abstract and does not relate to a possible hardware implementation. PMCN and the method of Melhem are both projected onto an example in this report. PMCN needed less hardware but more clock cycles to compute the SMVM. The efficiency of PMCN was only 18.5% for this example while the solution of Melhem achieved an efficiency of 62.5%. From the example it is illustrated that PMCN can have a lower efficiency then the method of Melhem if floating point hardware is used because of the pipelined MAC unit. In case of fixed point hardware without a pipelined MAC unit, PMCN might achieve higher efficiencies compared to the method of Melhem.

# 5. Alternative 1: Plans

# 5.1. Computing the SMVM on one PE

In chapter 2.5.1 it is already indicated that the number of MAC units that the target FPGA can hold is 31. This chapter explains the implementation of a PE and possible optimizations to give a base for a multiple PE design.

# 5.1.1. Plans

As explained in chapter 2.5.2 a PE is able to perform MAC instructions. This means that the complete SMVM can be executed on one PE. The following pseudo code represents a normal (not sparse) matrix vector multiplication of matrix A times vector  $\mathbf{x}$  and the result is vector  $\mathbf{y}$ . Matrix A has n \* n elements. for (int i = 1; i < n; i++) {

```

y(i) = 0;

for (int j = 1; j < n; j++) {

y(i) = A(i,j)*x(j) + y(i);

}

}

```

The outer for loop loops over the rows and the inner for loop loops over the columns. In case of a sparse matrix the inner loop is modified such that the loop is only over the non-zero elements. The problem with this schedule is that the pipeline stages of the MAC unit will result in a delay because of the dependencies of value y(i). For the following example the number of pipeline stages of the MAC unit is assumed to be one.

$$\begin{pmatrix} 1 & 2 & . \\ . & 3 & 4 \\ . & . & 5 \end{pmatrix} \begin{pmatrix} A \\ B \\ C \end{pmatrix} = \begin{pmatrix} y_1 \\ y_2 \\ y_3 \end{pmatrix} = \begin{pmatrix} 1A+2B \\ 3B+4C \\ 5C \end{pmatrix}$$

Figure 37: Example SMVM

In cycle one the PE can start the computation of  $y_1=1A+0$ . The problem is that the PE cannot start the computation of  $y_1=2B+y_1$  at cycle two because  $y_1$  is not yet available because of the pipeline latency. The PE can only start at cycle three. Thus for the first row, one MAC slot is not used. In [13] a method is described to use the MAC unit more efficiently. This is done by computing multiple results at the same time. For this particular example at cycle one the PE can start the computation of  $y_1=1A+0$ , at cycle two  $y_2=3B+y_2$ , at cycle three  $y_1=2B+y_1$ , at cycle four  $y_2=4C+y_2$  and at cycle five  $y_3=5C+y_3$ . With this schedule the utilization of the MAC unit is 100%. This optimization is also known as loop unrolling. The following pseudo code represents this scheme for dense matrices:

```

for (int i = 1; i < n; i=i+2) {

y(i) = 0; y(i+1) = 0;

for (int j = 1; j < n; j++) {

y(i) = A(i,j)*x(j) + y(i); //Cycle one of MAC unit

y(i+1) = A(i+1,j)*x(j) + y(i+1); //Cycle two of MAC unit

}

}</pre>

```

Incase of sparse matrices not every row has the same number of non-zeros. Computing consecutive rows in parallel will not result in an efficient schedule. A near optimal schedule can be achieved by computing the

longest rows (most non-zero elements) first. In case of the MAC unit proposed in [7] the adder pipeline has eight stages. This means that eight rows will be processed in parallel.

As explained before a near optimal schedule can be achieved by processing the longest rows (with the most non-zero elements) first. Further each non-zero element has a column index which must be used to index the vector and an additional boolean to indicate the completion of the computation of a row. All these variables can be seen as a plan to compute the SMVM in a near optimal way. In the FPGA this "plan" is stored in a memory. Further a PE also needs a memory with the vector **x** and a memory to store the result vector **y**.

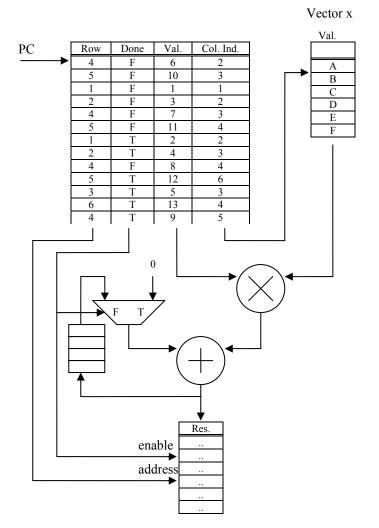

Consider the following more complex example with an adder pipeline of four stages.

$$\begin{pmatrix} 1 & 2 & \dots & \dots & \\ & 3 & 4 & \dots & & \\ & & 5 & \dots & & \\ & & 6 & 7 & 8 & 9 & \dots \\ & & & 10 & 11 & \dots & 12 \\ & & & & & 13 & \dots \end{pmatrix} \begin{pmatrix} A \\ B \\ C \\ D \\ E \\ F \end{pmatrix} = \begin{pmatrix} y_1 \\ y_2 \\ y_3 \\ y_4 \\ y_5 \\ y_6 \end{pmatrix} = \begin{pmatrix} 1A + 2B \\ 3B + 4C \\ 5C \\ 6B + 7C + 8D + 9E \\ 10C + 11D + 12F \\ 13D \end{pmatrix}$$

#### Figure 38: Example SMVM

From the matrix and the number of pipeline stages the following plan can be constructed.

| I | Row | Done | Val. | Col. Ind. | PC |

|---|-----|------|------|-----------|----|

| Γ | 4   | F    | 6    | 2         | ◀  |

|   | 5   | F    | 10   | 3         |    |

|   | 1   | F    | 1    | 1         |    |

|   | 2   | F    | 3    | 2         |    |

|   | 4   | F    | 7    | 3         |    |

| l | 5   | F    | 11   | 4         |    |

| l | 1   | Т    | 2    | 2         |    |

| L | 2   | Т    | 4    | 3         |    |

|   | 4   | F    | 8    | 4         |    |

|   | 5   | Т    | 12   | 6         |    |

|   | 3   | Т    | 5    | 3         |    |

|   | 6   | Т    | 13   | 4         |    |

| ſ | 4   | Т    | 9    | 5         |    |

Figure 39: "Plan" for the computation of SMVM of the example

For simplicity the column row is added to the plan. A near optimal schedule can be constructed by starting with the longest row. In this example row number four is the longest (most non-zero elements) so it is scheduled first. It does not matter which non-zero element is processed first. It makes sense to just start with the left most non-zero element; in this case it has the value six. The column index of the non-zero element is two. Because this is not the last non-zero element of the row, the value of done is false. Summarized, the first row of the plan has the values 4, false, 6 and 2. Because of the adder pipeline the second non-zero element of the second largest row, etcetera. Incase of equally long rows (same number of non-zero elements) it does not matter which one is scheduled first. Thus before the actual SMVM is executed a preprocessing phase is needed to make "plans".

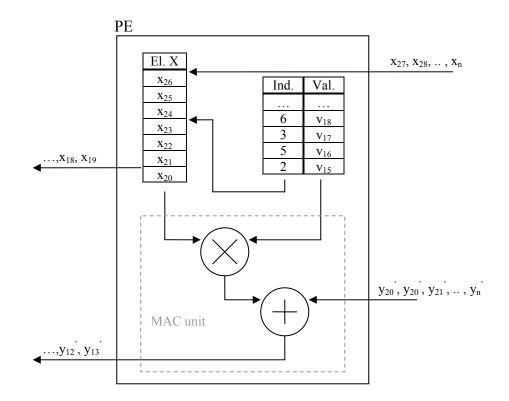

## 5.1.2. PE Design

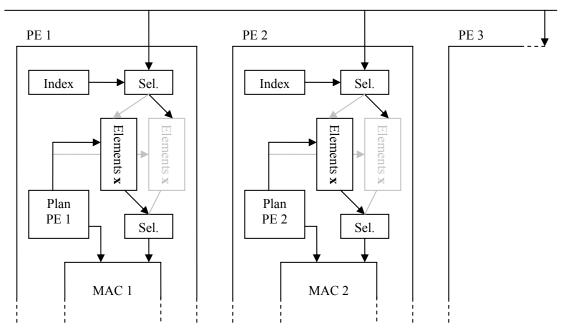

Figure 40 represents the design of the PE for execution of plans as suggested in [13].

For simplicity the four pipeline stages are placed outside the adder and implemented as four registers. The column Col. Ind. is used to index the vector  $\mathbf{x}$ . The column Row is used to index the result memory.

# 5.1.3. Mapping of the system matrix

In the previous examples the number of adder pipeline stages was small compared to the number of adder pipeline stages of the MAC unit proposed in [7] which is eight. Simulations have shown that this did not have a great impact for the Volume Reconstruction matrix. The utilization of the MAC unit was better than 99%.

The following enumeration recapitulates the properties of the application matrix. The numbers are approximations.

- Non-zero elements: 2,5M

- Size: 138k x 138k

- Bandwidth: 22k

- Average number of non-zero elements per row: 20

The application requires 64-bit values and the number of non-zeros of the matrix is about 2,5M, this means that the storage of one plan for the complete SMVM requires at least 2,5M \* 64 = 160 Mbit. The largest Virtex-II pro FPGA, the XC2VP100, has only 7,992 Kbit. Thus to compute the sparse matrix vector multiplication, the original plan has to be split into multiple smaller plans. On average there are twenty non-zero elements on each row. If the complete memory of the FPGA would be used to store only the values of a plan than approximately  $(7,992*1024)/(64*20) \approx 6400$  rows could be covered. The matrix has approximately 138k rows. To cover all the 138 rows of the matrix, at least (138k/6400) = 22 plans are required and hence 22 FPGAs. Besides the storage of the values of the matrix, the values of the vector must be stored, the result values and indices to index the memories. The value of 22 is a lower bound on the total number of plans.

The complete storage of the vector **x** would require  $138k*64 \approx 8,700$  Kbit, which is more than the largest Virtex-II pro has available as memory. A plan that covers the complete matrix requires the complete storage of the vector **x**. The conclusion from the previous paragraph was that the coverage with one plan is not possible because of the limited amount of memory of current FPGAs. Several smaller plans are required to cover the matrix. A plan can be defined as a strategy to compute a part of the SMVM by one PE such that the storage does not exceed the local memory of the PE.

Construction of a plan can be done is several ways. If the rows a plan covers can be any row of the matrix, every plan requires storage of the complete vector  $\mathbf{x}$ , which is not possible. A better idea is that a plan only covers consecutive rows. The advantage is that only a part of the vector  $\mathbf{x}$  has to be stored.

Figure 41: Dividing the matrix into "plans"

The bandwidth of the matrix is approximately 22k elements. Each plan can index the number of rows it covers plus the size of the bandwidth. The upper bound on the number of rows a plan covers is 6400. This would require  $(6400+22k)*64 \approx 1818$  Kbit of storage for the vector **x** for each plan.

Until this point all the computations where performed with an upper bound on the number of rows a plan could cover on average. The computations where only based on the storage of the values in the plan. To index the complete vector  $\mathbf{x}$ , 18 bits are required. But a plan only has to index a part of the vector  $\mathbf{x}$ . The upper bound on the number of elements to index is  $6400+22k \approx 28.4K$ , which can be indexed with 15 bits.

For the boolean value Done, one bit is required. In a real implementation the column row is not present. Instead an additional memory is used to index the results, which is discussed later. For each non-zero element 64+15+1 = 80 bits are required. The number of results is equal to the number of rows a plan covers. The upper bound is  $6400*13 \approx 82$  Kbits.

The memory to index the results will be kept constant; the other parts will be variable with the number of rows. Solving the following formula gives a more realistic idea on the average number of rows a plan covers.

On average each row has twenty non-zero elements, for each non-zero element 80 bits are needed. The size of a plan is thus the number of rows times the average number of non-zeros times 80 bits.

$$S_{plan} = N_{rows} \times \mu_{elements} \times r_{bits}$$

$$S_{plan} = N_{rows} \times 20 \times 80$$

The number of elements for the storage of a part of vector x is the number of rows a plan covers plus the bandwidth.

$$S_{vec\_x} = (N_{rows} + 22k) \times 64$$

$$S_{result} \approx 82 \times 1024$$

$$S_{FPGA} = 7,992 \times 1024$$

$$S_{FPGA} \ge S_{plan} + S_{vec\_x} + S_{result}$$

$$S_{FPGA} - S_{result} \ge 64N_{rows} + 1600N_{rows} + 22k \times 64$$

$$N_{rows} \approx 4000$$

$$N_{plans} = \lceil 138k / N_{rows} \rceil = 35$$

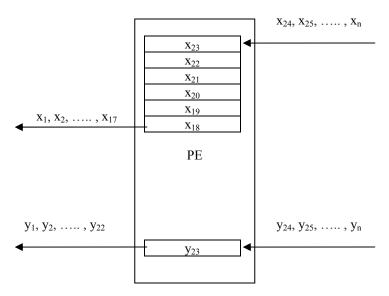

To compute the complete SMVM on one PE multiple plans are needed. The memories in FPGAs are often implemented as true dual port. This means that there can be two processes reading or writing at the same time if not on the same address. The PE executes a plan in order, thus after it has processed a non-zero element it can be overwritten by a non-zero element of the next plan. Suppose a PE processes a non-zero element every clock cycle and every clock cycle a new non-zero element can be loaded into memory. If this is the case than loading a plan takes the same amount of time as executing a plan. Switching from one plan to another does not require extra clock cycles.

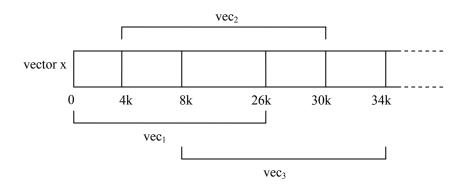

A plan requires a certain part of the vector  $\mathbf{x}$  available in memory. Suppose a PE is executing plan  $p_d$ . To execute this plan part vec<sub>d</sub> of the vector  $\mathbf{x}$  has to be in memory. After the PE has executed the last non-zero element of plan  $p_d$  it switches to plan  $p_{d+1}$ . Plan  $p_{d+1}$  requires part vec<sub>d+1</sub> of the vector  $\mathbf{x}$  to be in memory. To guarantee that switching to another plan does not take any additional clock cycles the parts vec<sub>d</sub> and vec<sub>d+1</sub> must be in memory at the same time. The size of vec<sub>d</sub> is about 26k elements. The total length of the vector  $\mathbf{x}$  is 138k elements.

The size  $vec_d$  is thus 10% of the size of the vector **x**. The total number of parts of the vector **x** is equal to the number of plans which is 35. The conclusion is that the part  $vec_d$  has overlap with the previous part  $(vec_{d-1})$  and the next part  $(vec_{d+1})$ .

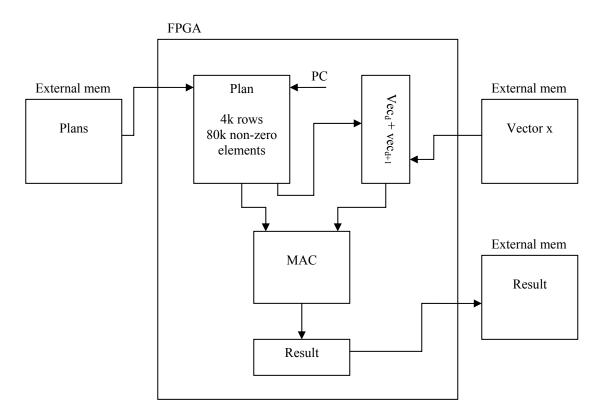

For this example the number of rows a plan covers is 4k with on average 20 non-zero elements on each row. Further there are three external memories, one holding the plans, another holding the vector  $\mathbf{x}$  and one to store the result vector. There are three memory interfaces to the three external memories. One memory interface is used to load plans into the internal memory of the FPGA by overwriting the already loaded plan. Another memory interface will be used to store the results into external memory and the last memory interface is used to load parts of the vector  $\mathbf{x}$ .

Suppose the first plan  $p_1$  and vec<sub>1</sub> are loaded into memory. The PE starts executing the first plan. While the PE is processing plan  $p_1$  plan  $p_2$  will be loaded by overwriting the non-zero elements that already have been processed. At the same time vec<sub>2</sub> has to be loaded into memory. Because of the overlap with vec<sub>1</sub> it is sufficient to only load the part that isn't already in memory.

Figure 42: Dividing vector x into parts

In the time the PE is executing plan  $p_1$ , 4k elements of vec<sub>2</sub> have to be loaded into memory. The number of non-zeros of a plan is equal to 20\*4k = 80k. Thus the memory interface for loading new plans must have a higher bandwidth than the memory interface used for loading parts of vector **x**. The difference is a factor twenty.

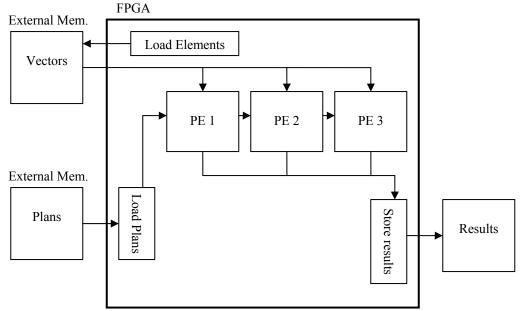

#### Figure 43: FPGA implementation

The memory bandwidth requirements for this system are very high. The question is if this system could be optimized such that the utilization of the PE stays at 100% while using less memory bandwidth.

# 5.1.5. Possible optimization

In the above examples the SMVM used only one vector. Each non-zero element is processed only once. A plan consisted of 80k non-zero elements that could index 26k elements of the vector  $\mathbf{x}$ . This implies that elements of the vector  $\mathbf{x}$  are indexed more than once.

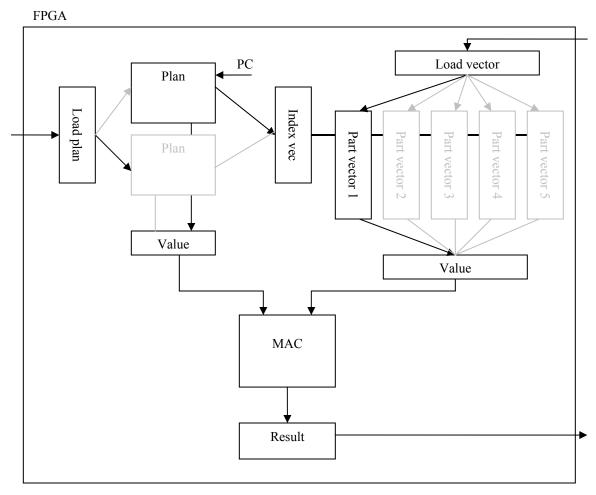

Loading data from external memory is very costly. The idea is thus to use the data that is already on chip as much as possible. The size of a plan is very large compared to the size of the vector. Executing a plan multiple times would decrease memory bandwidth requirements. This can be done if there are multiple vectors that must be multiplied with the same matrix.

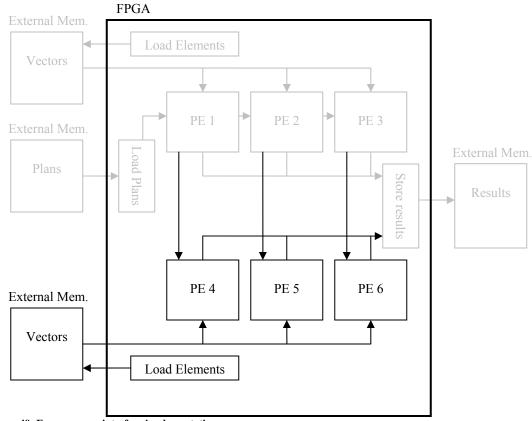

Suppose there are five vectors that must be multiplied with the same matrix. In the first run the PE executes plan  $p_1$  with vector one, in the second run it executes  $p_1$  with vector two, in the third run it executes  $p_1$  with vector three, etcetera. Every non-zero element is now used five times. The memory bandwidth requirement for loading a new plan is now an fifth of the original memory bandwidth requirement, while the other memory bandwidth requirements remain the same. Figure 44 gives a schematic view of such system.

#### Figure 44: FPGA implementation with multiple vectors

In the original scheme where the SMVM was only executed with only one vector, there was only one memory to hold the plan. This was possible because the new plan could directly overwrite the old plan with the same speed the PE executed. This requires a high memory bandwidth. The advantage of multiplying with multiple vectors in parallel is that the bandwidth requirements are lower. For this particular example the time to load a new plan may be five times longer than the time the PE would execute the plan. However a new plan cannot overwrite the plan the PE is executing. A solution is to use two memories of the same size that alternate their function. The memories can either be used by the PE to execute the plan or it can be used to store the new plan from external memory.

The gray boxes in figure 44 are not active for the execution of the plan.

The consequence of the additional memories is that there is less memory available for a plan. The number of plans will increase and the number of rows a plan covers will decrease.

$$S_{2 \times plan} = 2 \times N_{rows} \times 20 \times 80$$

$$S_{vec_x} = (2 \times N_{rows} + 22k) \times 64$$

$$S_{5 \times vec_x} = 5 \times S_{vec_x}$$

$$S_{result} \approx 82 \times 1024$$

$$S_{FPGA} = 7,992 \times 1024$$

$$S_{FPGA} \ge S_{2 \times plan} + S_{5 \times vec_x} + S_{result}$$

$$\begin{split} S_{FPGA} - S_{result} &\geq 640N_{rows} + 3200N_{rows} + 110k \times 64\\ N_{rows} &\approx 276\\ N_{plans} &= \left\lceil 138k / N_{rows} \right\rceil = 500 \end{split}$$

This chapter explained an algorithm to compute the SMVM on one PE. The PE was defined as a unit which had only one MAC unit to perform computations. From this definition an algorithm was proposed which achieved a very high utilization of the MAC unit with a limited requirement on the memory bandwidth. The utilization of the MAC unit was not addressed formally because simulations have shown that with a relative high number of rows (in the order of 1000) the lower bound of the utilization was 99%.

This chapter explains how a PE computes parts of the SMVM, the memory bandwidth interfaces required and an optimization for the memory bandwidth. This is done to give a base for a design with multiple PEs.

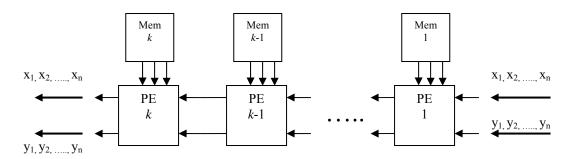

# 5.2. Computing the SMVM on Multiple PEs

The largest Virtex-II pro FPGA can hold 31 MAC units, which run at 170 MHz [7]. The peak performance of this FPGA with this type of MAC unit is 31\*170M\*2 = 10,5 MFLOPS (double precision). In the previous chapter only one MAC-unit was used which means that at most 1/31 of the peak performance of the FPGA was used. Using more MAC units might achieve better results. In this chapter as well as the previous, the PEs are specified to only have one MAC unit to perform computations.

## 5.2.1. Introduction

In the previous chapter the idea of plans was explained. A PE executes a plan on a vector or multiple vectors, loads new plans and loads elements of vectors. Figure 43 is taken as a base for a multiple PE design.

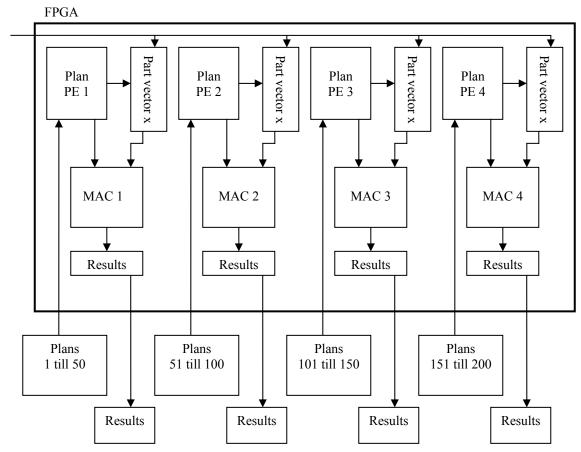

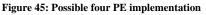

Assume a design with four PEs that all execute plans and there are 200 plans to compute the SMVM. The first fifty plans could be assigned to the first PE, plans 51 till 100 can be assigned to the second PE, etcetera.

For every additional PE, two additional memory interfaces are required. But this isn't the largest disadvantage. To store a part of the vector x, at least 22k elements must be stored because of the bandwidth of the matrix. These elements are represented with 64 bits,  $22k*64 \approx 1400$  Kbits. This is already 20% of the available memory of the FPGA. Thus at most five PEs could be used with this scheme. An optimization would be to only store the elements of the vector x that are really going to be used by a plan. Table 4 shows that not all the elements of a part of the vector are really used.

| Number of rows a plan covers | Number of elements<br>of vector <b>x</b> for a<br>plan | Avg. Number of<br>elements of<br>vector <b>x</b> really<br>used | Percentage | Max number of<br>elements really used<br>by a plan |

|------------------------------|--------------------------------------------------------|-----------------------------------------------------------------|------------|----------------------------------------------------|

| 32                           | 32+22k                                                 | 232                                                             | 1.1%       | 1080                                               |

| 64                           | 64+22k                                                 | 402                                                             | 1.8%       | 1698                                               |

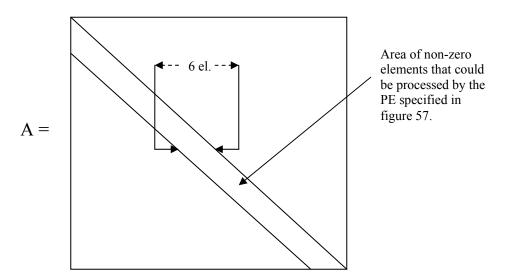

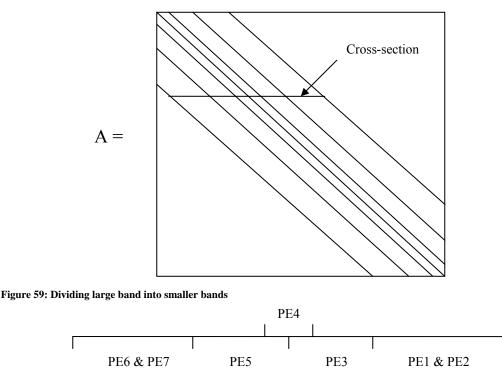

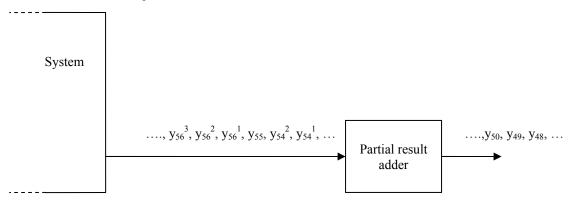

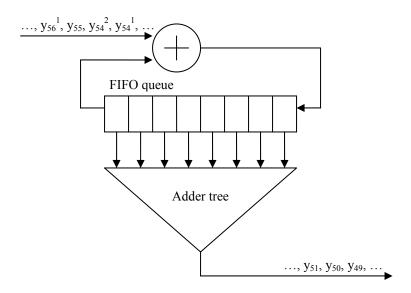

| 128                          | 128+22k                                                | 707                                                             | 3.2%       | 2468                                               |