# DATAFLOW-BASED MODEL-DRIVEN ENGINEERING OF CONTROL SYSTEMS

K.A.E. (Koen) Zandberg

MSC ASSIGNMENT

**Committee:** dr. ir. J.F. Broenink dr. ir. D. Dresscher ir. J. Scholten

January, 2020

003RaM2020 **Robotics and Mechatronics** EEMCS University of Twente P.O. Box 217 7500 AE Enschede The Netherlands

UNIVERSITY | **DIGITAL SOCIETY** OF TWENTE. INSTITUTE

TECHMED

## Contents

| 1 | Intro                   | duction | 1                                                 | 1  |  |  |  |

|---|-------------------------|---------|---------------------------------------------------|----|--|--|--|

|   | 1.1                     | Conte   | xt of This Thesis                                 | 1  |  |  |  |

|   | 1.2                     | Applic  | ation Workflow                                    | 1  |  |  |  |

|   | 1.3                     | Resea   | rch questions                                     | 3  |  |  |  |

|   |                         | 1.3.1   | Which dataflow models of computation are suit-    |    |  |  |  |

|   |                         |         | able as basis for model-driven development?       | 3  |  |  |  |

|   |                         | 1.3.2   | Which simulation features are required to verify  |    |  |  |  |

|   |                         |         | the supplied models?                              | 3  |  |  |  |

|   |                         | 1.3.3   | Which platform specific information is required   |    |  |  |  |

|   |                         |         | to transform the dataflow based model into a PSM? | 4  |  |  |  |

|   | 1.4                     | Thesis  | Structure                                         | 4  |  |  |  |

|   |                         |         |                                                   | ·  |  |  |  |

| 2 | Bacl                    | kground | ł                                                 | 6  |  |  |  |

|   | 2.1                     | model   | -driven development Methodologies                 | 6  |  |  |  |

|   | 2.2                     |         | Dataflow Models of Computation                    |    |  |  |  |

|   |                         | 2.2.1   | Dataflow Theory                                   | 8  |  |  |  |

|   |                         | 2.2.2   | Synchronous Dataflow                              | 8  |  |  |  |

|   |                         | 2.2.3   | Homogeneous Synchronous Dataflow                  | 9  |  |  |  |

|   |                         | 2.2.4   | CSDF                                              | 9  |  |  |  |

|   |                         | 2.2.5   | VRDF/VPDF                                         | 9  |  |  |  |

|   |                         | 2.2.6   | BDF                                               | 9  |  |  |  |

|   |                         | 2.2.7   | SADF                                              | 9  |  |  |  |

|   |                         | 2.2.7   | FSM-SADF                                          | 10 |  |  |  |

|   |                         | 2.2.0   | Dataflow analysis                                 | 10 |  |  |  |

|   | 2.3                     |         | rm Meta Model Designs                             | 10 |  |  |  |

|   | 2.5                     | i latio |                                                   | 10 |  |  |  |

| 3 | Ana                     | vsis    |                                                   | 12 |  |  |  |

| - | 3.1                     |         | ol System requirements                            | 12 |  |  |  |

|   | 0.1                     | 311     | Modelling Requirements                            | 12 |  |  |  |

|   |                         | 3.1.2   |                                                   | 12 |  |  |  |

|   |                         | 3.1.3   | Simulation Requirements                           | 13 |  |  |  |

|   | 3.2                     |         | ow Model of Computation                           | 13 |  |  |  |

|   | 3.3                     |         | rm Meta Model                                     | 14 |  |  |  |

|   | 0.0                     | 3.3.1   | Platform Meta-Model Components                    | 14 |  |  |  |

|   |                         | 0.0.1   |                                                   | 14 |  |  |  |

| 4 | 4 Design Requirements 1 |         |                                                   |    |  |  |  |

|   | 4.1                     | Applic  | ation design                                      | 16 |  |  |  |

|   |                         | 4.1.1   |                                                   | 16 |  |  |  |

|   |                         | 4.1.2   | Model analysis                                    | 16 |  |  |  |

|   |                         | 4.1.3   | Model Simulation                                  | 17 |  |  |  |

|   |                         | 4.1.4   | Model-to-model conversion                         | 18 |  |  |  |

|   | 4.2                     | Langu   | age design                                        | 18 |  |  |  |

|   |                         | 4.2.1   | Model description                                 | 19 |  |  |  |

|   |                         | 4.2.2   | Hardware description design                       | 19 |  |  |  |

|   |                         |         | ······································            |    |  |  |  |

| 5 | Impl                    | ementa  | ation                                             | 21 |  |  |  |

|   | 5.1                     | Functi  | on blocks                                         | 21 |  |  |  |

|   |                         | 5.1.1   | Communication                                     | 21 |  |  |  |

|   |                         | 5.1.2   | Configuration                                     | 22 |  |  |  |

|   |                         | 5.1.3   | Computational functionality                       | 22 |  |  |  |

|   | 5.2                     | Syster  | n meta-model                                      | 22 |  |  |  |

|   | 5.3                     |         | ntegration                                        | 23 |  |  |  |

|   |                         | 5.3.1   | Model rendering                                   | 24 |  |  |  |

|   | 5.4                     |         | analysis                                          | 24 |  |  |  |

|   |                         | 5.4.1   | SDF based models                                  | 25 |  |  |  |

|   | 5.5                     |         | simulation                                        | 25 |  |  |  |

|   |                         |         | Co-simulation synchronization scheme              | 26 |  |  |  |

|    | 5.6<br>5.7<br>5.8                                      | Simulation Results                                                                                                                                                                                        | 26<br>27<br>28<br>29                                           |

|----|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 6  | Testi<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | ng<br>Model handling                                                                                                                                                                                      | 31<br>31<br>34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>39 |

| 7  | Case<br>7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6         | StudyModelPlatform Independent ModelPIM analysis7.3.1 Delay effectsPlatform Design7.4.1 RaMstix board7.4.2 Arduino UnoPSM Conversion7.5.1 RaMstix Target7.5.2 Arduino Uno TargetEvaluation                | 41<br>42<br>42<br>43<br>43<br>45<br>45<br>45<br>45<br>46<br>46 |

| 8  | Disc                                                   | ussion                                                                                                                                                                                                    | 48                                                             |

| 9  | Conc<br>9.1                                            | lusion and Recommendations<br>Recommendations                                                                                                                                                             | 50<br>51                                                       |

| Ар | pendi                                                  | ces                                                                                                                                                                                                       | 52                                                             |

| A  | Mod<br>A.1<br>A.2<br>A.3<br>A.4<br>A.5                 | el examples<br>SDF and SADF examples<br>PID example<br>Unit example<br>Linix demonstrator<br>Platform model files<br>A.5.1 Platforms<br>A.5.2 Boards<br>A.5.3 Compute<br>A.5.4 Actuators<br>A.5.5 Sensors | 52<br>54<br>56<br>57<br>61<br>62<br>64<br>66<br>67             |

| 10 | Refe                                                   | rences                                                                                                                                                                                                    | 68                                                             |

## 1 Introduction

With the need for more advanced control systems, tools and applications to aid the design of these control systems help to reduce the number of design iterations required. One of the often used design paradigms is model-driven development (MDD) (Selic, 2003). These paradigms allow the engineer to focus on the control system by offering abstraction layers for both the hardware platform and the software implementation details.

The increasing demand and increasing complexity of embedded control systems demands strong requirements on the design paradigms. The systems, often distributed, are limited in resources while still having to adhere to strict execution deadlines. With these limitations and added requirements to the interaction between the software and the hardware components, designing a full embedded control systems becomes a challenging exercise.

While it is clear from earlier work that a model driven structured approach with accompanying tools is a suitable approach, there is no single correct solution. Multiple approaches each with their advantages and disadvantages are available. Often these approaches focus on a hierarchical structural approach to the software based on object oriented design principles. From a control engineer working with an algorithmic approach, this is not an optimal approach.

## 1.1 Context of This Thesis

This thesis shows a stepwise-refinement approach based on dataflow representations of the models as an alternative to the previous work at the research group. The workflow is geared towards an incremental approach to control system design, each step increasing the level of detail available in the models.

The approach uses a dataflow representation internally for analysis and simulation of the models. The dataflow-based approach offers analysis into the latency of the models.

The main use of dataflow models is in the analysis of DSP applications, but is used here for modelling control systems. In contrast to control systems, for DSP systems throughput is often more important than latency. Within this paper, throughput analysis is going to be neglected in favor of latency analysis.

An analysis and simulation application is presented and used as proof of principle of the approach. This is used for verification of the ideas and for validation of the proposed workflow. At last it will be used to provide answers to the research questions.

## 1.2 Application Workflow

A top down approach to the design of these control systems is given here with an accompanying application to enhance the development. The workflow used for the system design flow is based on Broenink, Ni, and Groothuis (2010) and Broenink and Ni (2012). The multi-step refinement approach allows for a modular and incremental way to the challenges of the control system design.

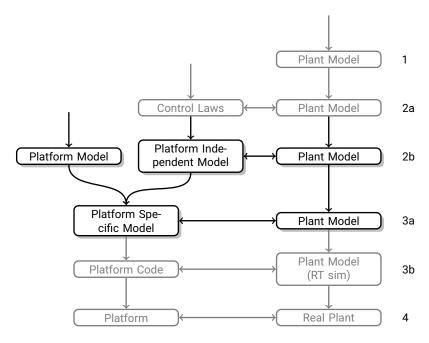

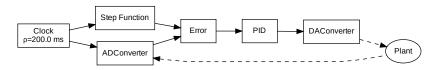

The different steps of the workflow are shown in Figure 1.1. For an end user (control engineer) this application workflow consists of a multistep approach where each step increases the level of refinement of the model of the control system descriptions until the result is the generated application code. This workflow allows the engineer to supply a high-level model based on the component interaction as a start. The application should allow for verifcation of functional properties, with emphasis on non-functional properties such as deadline analysis. After the final step, platform-specific application code is presented as implementation of the control system on the selected platform.

**Figure 1.1:** Stepwise refinement workflow for control systems, the bold steps are the main focus of this thesis.

The first step of the workflow is to have a set of control laws engineered for the plant model designed. The design of the control laws itself is out of scope for the application proposed here, but must be in a format suitable for conversion to a block diagram-like structure. This step is shown as stage 2a of the workflow described in Figure 1.1.

The next step as shown in stage 2b of the workflow is to convert the control laws into a platform-independent model (PIM), converting the control laws into a suitable format for the application. The PIM allows for early formal verification of the model using modelling analysis features, and for functional verification of the model by co-simulation with the plant model. The PIM allows for analysis and simulation with arbitrary accuracy, with infinite accuracy assumed by default. Function blocks are assumed to have no delay, but can be configured with a non-zero worst-case execution time.

Parallel to this stage models of the available hardware platforms are created. These models contain the specifications of the hardware components on the platform. The separate platform models can be used as a library and they are aimed to be reusable by multiple different control systems.

In the third step, the model is adapted to a chosen target platform system, an automated conversion from the PIM to a platform-specific model (PSM). The specification from the platform models is used to augment the PIM with details from the platform model to a PSM. The goal is to have a model that closely matches the worst-case behaviour on the target hardware platform, enabling analysis and verification of the behaviour of the system on the target hardware.

Step 3b from Figure 1.1 consists of a translation of the PSM to platform code. Based on the hardware description from the second step, platform- and application-specific code is generated. The resulting code can be deployed on the hardware and should function comparable to the earlier analysis. This step is out of scope for this thesis.

### 1.3 Research questions

The workflow described above offers a number of challenges when using dataflow-based models. This thesis attempts to provide answers to the challenges involved in step 2b and 3a of the workflow. The set of research questions presented here are used to explore these challenges and come to a set of requirements for the application.

1.3.1 Which dataflow models of computation are suitable as basis for modeldriven development?

Within dataflow different models of computation (Stuijk et al., 2011) are available. Comparisons of these models often results in a trade-off between available formal model analysis techniques and modelling expressiveness. Not all models provide the analysis techniques or the expressiveness to model control systems. The focus of this question is to determine which models of computation are suitable for modelling control systems, resulting in a list of models of computation which offer enough expressiveness while offering enough analysis techniques to still allow for sufficient model verification.

- How is the system limited by the choice of dataflow model of computation? When a control system is modelled as dataflow model, sufficient modelling expressiveness is required to represent the control system as the dataflow model. Some models of computation are too restricted to properly model all possible aspects of a control system.

- Which analysis techniques from the dataflow models of computations can be applied for control-model analysis? Each model of computation provides a set of analysis methods. The analysis required for formal verification of the control system must be mapped to these analysis methods. The expressiveness of the Model of Computation (MoC) can be limited to satisfy requirements of required analysis techniques, placing restrictions on the expressiveness available for the control system models.

Together these subquestions limit the available models of computation by either a minimum amount of required expressiveness or the required analysis provided.

#### 1.3.2 Which simulation features are required to verify the supplied models?

While dataflow based models allow for some analysis by themselves, it does not include functional aspects of the system in the models. To extend the models in such as way to allow functional simulation, a dataflow simulator must be extended to include these features.

• Which additional details are required for improving the design and analysis of models? Model design can benefit greatly from additional details and features added to the models. This includes features to clarify the model and limit the interpretation ambiguity of the models. A simulator must provide the level of detail required for a sufficient model verification required by the end user. How should external models be integrated in the simulator? Accurate model simulation is only possible with an accompanying plant model integrated in the simulator. Without this model, it is not possible to verify the model against the real-world usage of the system.

The goal is to end up with an extended feature set on top of the dataflow models to allow for functional simulation of models. Without these features the analysis is restricted to timing analysis, but without verification of the model functionality it is not possible to show how the model behaves under the timing restrictions. These questions attempt to seek for answers on which features must be implemented to add sufficient analysis options to the simulator to allow the end user to verify the functionality of their models.

1.3.3 Which platform specific information is required to transform the dataflow based model into a PSM?

Translating the dataflow based model to a platform specific model requires refinements to the initial model adding platform information. The platform meta model (PMM) provides the necessary platform abstraction for the control model to enable this transformation. This abstraction must strike a balance between providing enough detail for the control model to adapt without increasing the complexity necessarily

- Which properties of the PMM are strictly necessary for the modelto-model conversion? The PMM must properly propagate platformspecific limitations to the model. Based on these limitations, the model-to-model conversion can be adapted to adhere to the requirements of the platform.

- How should the PMM be structured to allow for reuse of different components? Multiple target platforms can share components between them, such as different platforms sharing an identical sensor or actuator. This reuse can exist at multiple levels, Different SoCs could share processor architectures or peripheral IP implementations. For efficient use of the PMM, enabling the reuse of information is a must have.

- Which extended analysis options are available with the additional information from the PMM for the dataflow model? Adding the extra information from the PMM results in a more detailed and more specific model. Information such as allowed parallel execution or peripheral access modes can add additional refinement to the model. This extra information can then be used to affirm whether the model is realisable on the specified platform.

The resulting PMM, when adhering to the results of these questions, offers the required features for the model-to-model conversion and allows the refinement of the PIM into the PSM. Furthermore it offers a basis for the code generation required for a final model-to-text conversion.

#### 1.4 Thesis Structure

The rest of this thesis is structured as follows. First the previous work relevant for this thesis is described (Chapter 2), including an concise exploration of the different dataflow models of computation and a description of a number of different existing model-driven engineering solutions. Based on this, a dataflow model of computation is selected in the analysis (Chapter 3). The extensions required to the simulator

are also discussed in the analysis. From this analysis and the research questions a set of requirements for the proof-of-principle application are formulated in the design decisions (Chapter 4). These design requirements are used as a basis for the application of which the design principles are described in the execution in Chapter 5. The resulting features are extensively tested and verified in Chapter 6: Testing. In Chapter 7, a further case study showing the design steps, expectations and results for a model is presented in the case study. Finally the results from the verification and the case study are discussed in Chapter 9.

## 2 Background

### 2.1 model-driven development Methodologies

Code generation based on model-driven development (MDD) as modelling system is not a new area. Already a number of solutions exist with multiple different approaches to MDD. These approaches distinguish themselves based on modelling language, component representation and offered features.

*RobotML* (Dhouib et al., 2012) is a DSL for design, simulation and deployment of robotic application. The model consists of architecture, communication, behaviour and deployment meta-models. Each meta-model has their own function defining different aspects of the robotic application. The architectural model defines the high level aspects of the robotic application. This includes the robotic system, describing the structural composition of the application using the CPC model. The communications aspect handles formalized data exchange using ports. Behaviour allows defining high level instructions using algorithms or finite state machines. Deployment specifies the target robotic platform, assisting in the code generation for the application A full eclipse based toolchain provided with the workflow. RobotML allows for defining non-functional properties such as timing information. This can be fed into schedulability analysis tools e.g. Cheddar (Singhoff et al., 2004).

The BRICS component model (Bruyninckx et al., 2013) describes two paradigms - Model-driven approach and separation of concerns. The separation of concerns paradigm is mapped to the 5Cs: Communication Computation, Configuration, Coordination and Composition. The model-driven approach follows a Component-Port-Connector (CPC) metamodel. The components represent computations and can be hierarchically composed to represent composite components. Ports represent communication where connectors combine two compatible ports, Configuration allows for influencing the system behaviour by configuration parameters Coordination determines the behaviour of the components and how the different components must function together. Composition brings the model together as a instance of a particular system, allowing decoupling and reuse where necessary. The workflow as defined by the BRICS model is roughly as follow: A structural architecture is defined using components, ports and connectors. Each complex component includes a coördinator based on state machines. A model to text transformation is applied to generate the code.

*SmartSoft* (Schlegel and Worz, 1999) has a model based approach based on a multilayered component approach. SmartSoft provides primitives as building blocks to create robotic systems. The internal component implementation is abstracted away by a skeleton representation. Modelling is based on UML based diagrams to facilitate reuse of components. The component itself define strict interfaces to provide reliable reuse of components. Models do not contain any timing information, although one of the target platforms is a real time operating system.

The  $V^3CMM$  components meta-model (Diego et al., 2010) uses three complementary views: Structural, coordination and algorithmic to achieve a component based model. The structureal view provides the static structure of the required components. The coordination view describes the event-driven behaviour of each component. Lastly the algorithmic view provides a way to express algorithms implemented by the components. Components are reusable in multiple ways. The modelling tools use UML to represent the models using both class diagrams and state transition diagrams.

The model-driven approach as described for TERRA (Bezemer, 2013) separates the design workflow into a multi stage approach; each stage refining the model. The TERRA models are based on the Communicating Sequential Processes (CSP) language. Hardware design and loop control components are separated into two branches. It allows for a strong separation of components and hardware. Furthermore the incremental approach of TERRA allows for increasing the complexity model in a stepwise manner.

While not containing a code generator, the *Ptolemy II software framework* (Liu et al., 2001) contains functionality to experiment with actororiented design. It supports multiple different models of computation, synchronous dataflow among others. It allows for hierarchically designed models and is able to model heterogeneous systems. The aim is to be able to study timing properties of different hybrid systems.

*ThingML*(Harrand et al., 2016) is a framework for code generation targeting heterogeneous platforms aimed at sensor network applications. Multiple different target languages and platforms are targeted and a lot of work went into tuning the approach for high customizability. It supports multiple different architectures and frameworks as targets. Each language has their own set of code generator targets. Furthermore, functionality is split into a number of categories. For each category, behaviour can be overridden by using inheritance. Support for so called channels and connectors is used to implement either inter-actor communication possibly spanning multiple physical systems. This also includes functionality to communicate directly to peripherals, for example I<sup>2</sup>C connected peripherals. Behavioural implementations are generated by generating state machine structures. It can generate either full code for a component or rely on middleware API's to support the required functionality.

Among the advantages of ThingML is the use of a single language with multiple supported platforms as target backend, resulting in a platform independent specification. To allow for a practical system, the system must allow for extending and integrating the generated code with existing code. This to allow for a gradual adoption of model-driven engineering (MDE) and allowing interfacing legacy code.

Summarizing, most of the approaches describe the models using an UML-like structural approach where the relation between different components is specified. This allows for detailed descriptions of the models, focussing on describing the functional aspects of the models. However they lack simulation and analysis options required for verification of the system models.

In contrast to most of the approaches listed here, the proposed workflow will focus on letting the end user create a model from a chain of computational functions. The approach used here allows for providing analysis and functional simulation during the modelling process.

## 2.2 Dataflow Models of Computation

Dataflow is a modelling technique to describe operations on a stream of data. Closely related to Kahn Process Networks (Kahn, 1974), dataflow diagrams can be used to describe concurrent real-time systems, and data processing applications. Different MoCs are available within dataflow, each with different limitations on expressiveness and analysis. Figure 2.1 shows a hasse diagram of different dataflow MoCs. Each MoC in the diagram is able to model all MoCs below itself.

#### 2.2.1 Dataflow Theory

A concise description of dataflow operation theory is required as background information. Dataflow diagrams are expressed as a set of actors. Each actor has an associated predefined firing duration. An actor fires as soon as it's firing condition is satisfied. For most dataflow MoCs the firing condition is satisfied as soon as each input edge contains at least the number of required tokens for that input. Tokens are used to represent data within the model, representing abstract data. An actor consumes the required number of tokens from each inbound edge when starting and releases the indicated number of tokens on each outbound edge when done.

Actors are connected using edges. An edge can be modelled as a buffered directional unbounded communication channel. Edges can contain an initial set of tokens.

An actor is only limited by the firing condition before it is executed. There is no limitation on concurrent execution of a single actor. However it can be limited by adding a self edge with only a single token

The MoC selected for this system should allow for enough expressiveness to describe control systems with, while allowing for enough analysis possibilities to validate the control system.

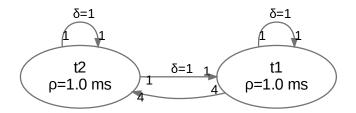

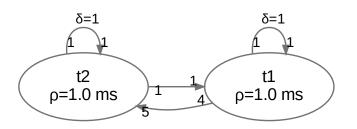

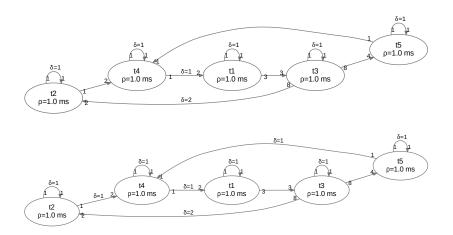

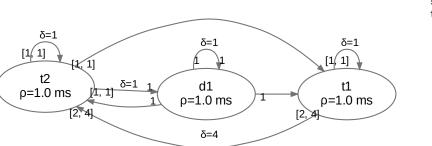

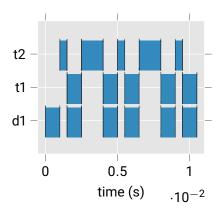

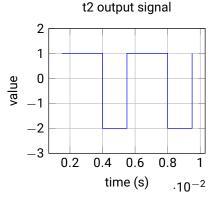

An example dataflow graph is shown in Figure 2.2. The dataflow graph contains two actors, named t1 and t2, each with an execution time of 1 ms, indicated by the  $\rho$  symbol. t1 Has a production of 4 tokens on the edge to t2 and consumption of 1 token on the edge from t2. Actor t2 has opposite but matching consumption rates. Furthermore 1 initial token are available on the edge from t2 to t1, indicated with  $\delta$  symbol. Each actor also has a self edge with one initial token and consumption and production equal to 1. This limits parallel execution of each actor by requiring a token to be available on the self edge. This token is consumed when the actor execution starts and produced when the execution of the actor finishes.

A limited set of dataflow MoCs relevant for this work is presented here. Not all properties of the different MoCs are described. Features required for this work are emphasised.

#### 2.2.2 Synchronous Dataflow

Synchronous dataflow (SDF) allow for modelling statically scheduled applications. Dynamic behaviour however is not possible. Within an SDF model, actors can have a arbitrary but fixed number of consumed or produced tokens for each edge, and firing times are constant. Analysis options contain schedule, deadlock and buffer size analysis. Due to the static nature of the SDF schedule, the firing pattern will form a repetitive pattern, or iteration, after each iteration, a deadlock-free SDF model is at the same state. With these properties, an SDF-based model

**Figure 2.1:** Hasse diagram of different dataflow models of computation

**Figure 2.2:** Example synchronous dataflow model with two actors.

allows for synthesis based on a static schedule. When data-dependent choice is not required in the model, SDF-based models are sufficient to model the applications.

#### 2.2.3 Homogeneous Synchronous Dataflow

Homogeneous Synchronous Dataflow models are a subset of SDF models. Within an HSDF model, all token production and consumption rates are equal to one. While this simplifies the analysis, the expressiveness is severely limited with this.

#### 2.2.4 CSDF

Cyclo static dataflow (Bilsen et al., 1996) allows for variable schedule based on a predefined repeating sequence. No data dependent pattern is possible, keeping the system statically schedulable. Some additional expressiveness is available due to this pattern based variations in the actors.

#### 2.2.5 VRDF/VPDF

Variable Rate Dataflow (Wiggers et al., 2008) allows for actors with predefined variable production and consumption rates. This allows for data dependent data rates. VPDF extends this in a CSDF-like way with different phases for each actors. Multiple different predefined variable production and consumption rates can be defined for each actor, with the actor state being in one of these predefined rate settings.

#### 2.2.6 BDF

Boolean Dataflow (Buck and Lee, 1993) allows for an additional actor type implementing an boolean choice between two output actors. Tokens are produced on one of the two edges. The output edge depends on the value of the control token consumed by the boolean-controlled actors. This provides the model with a limited way to influence the behaviour of the models.

#### 2.2.7 SADF

Scenario-aware dataflow (Theelen et al., 2006) allows for a fully dynamic schedule, with switching based on special detector actors. The additional detector type actor allows for changing state based on a combination of a state machine and the received token. Special control edges, originating from the detector actors, allow for propagating a state change to different actors. The control tokens from these edges are consumed by the actors befor processing the regular tokens. Both token consumption and execution time is determined by the control token consumed.

While analysis is limited by the dynamic scheduling nature, it is possible to reduce the model to a set of different SDF-type models, based on the different states reachable. When the models are limited to strong consistency and strong dependency, similar analysis to SDF-based models is applicable.

An important aspect of scenario-aware dataflow (SADF) based graphs is the explicit sequence of scenarios possible represented by the state machines associated with the decoder actors. This is not available with other data dependent dataflow MoCs such as VPDF and DDF.

#### 2.2.8 FSM-SADF

Finite State Machine Scenario Aware Dataflow (Stuijk et al., 2011) are less expressive compared to SADF in that data rates can be varied once per iteration. It is based on the SADF MoC with the limitation that the system is only allowed to switch states at the beginning of the SDF iteration. Each iteration, a state switch happens, influencing token rates and firing times. While technically data dependent choice is available, state transitions are modelled with a probabilitstic model.

#### 2.2.9 Dataflow analysis

The dataflow analysis as used here focuses on consistency checks, deadlock checks and latency analysis.

- *Consistency*: A dataflow graph is consistent if on each edge, in an infinite firing, the same number of tokens are consumed as produced.

- *Repetition vector*: The vector describing the number of repetitions for each actor that will cause the number of tokens produced and consumed on an edge to be equal.

- *Deadlock Free*: An dataflow is deadlock free if sufficient tokens are available such that all actors are able to fire a number of times equal to their repetition vector entry.

Consistency checks are important to prevent either deadlocks or token accumulations in long-running models. Depending on the dataflow MoC, different techniques are available to verify whether a graph is consistent, based on a set of balance equations (Lee, 1991), (Buck and Lee, 1993), (Theelen et al., 2006) The null space of the balance equations has a nontrivial solution when the graph is consistent. This nontrivial solution is the repetition vector of the graph.

A model is deadlock free when sufficient tokens are available on every cycle of actors in the graph to let every actor execute a number of times equal to their repetition vector. A consistent dataflow graph is not necessarily deadlock free, a consistent graph does not necessarily have sufficient tokens available to prevent deadlocks. After each execution cycle, the token distribution is at the initial distribution. A deadlock-free graph is not necessarily consistent as a graph accumulating tokens can be deadlock free but is not consistent.

## 2.3 Platform Meta Model Designs

Platform models are already extensively used on computer systems where no enumeration of connected components is available, often the case with embedded systems.

Device Tree (Likely and Boyer, 2008) is used on the Linux operating system when the hardware does not support enumeration. While enumeration is available on platforms containing a BIOS, platforms such as PowerPC require a description of the hardware to provide the kernel with the hardware configuration. Device Tree offers a tree based system containing the layout of the hardware with all properties required to initialize the proper drivers. It offers a human readable format supporting a hierarchical and reusable format which is compiled into a binary representation when deployed.

*Mbed OS* (Arm Limited, 2019) follows an hierarchical structure separating the SoC from the platform config code. Configuration can be

specified at multiple levels with the target board as the highest level. Boards can contain configuration for peripherals and supported features.

Both of these frameworks succesfully separate function and configuration from eachother. They also succesfully use a hierarchical description of reusable components. However, their application is strictly geared towards a single application and their definitions are not aimed at reusability by other projects.

## 3 Analysis

Identification of the required features for modelling control systems must be explored before application requirements can be formulated. First modelling and analysis requirements for control systems must be explored. This provides the groundwork for the requirements of the application. Based on the same requirements, the explored dataflow models of computation are compared and one is selected as model backend for the application.

## 3.1 Control System requirements

For the system to be of use to the control engineer, some requirements have to be explored first. These requirements are necessary to allow the control engineer to use the software for control system design. Requirements can be categorized:

- *Modelling*: The expressiveness required for modelling control systems.

- Analysis: The set of analysis features required for verification of the non-functional parts of the control system.

- *Simulation*: The features required in the simulator for verification of the functional aspects of the control system.

#### 3.1.1 Modelling Requirements

Some degree of expressiveness is required in the modelling system to allow the control engineer enough expressive freedom to design the control system. Limiting this too much obstructs the control engineer making the software unusable. First the requirements from control system perspective are enumerated. These are then translated to requirements for the modelling language in Chapter 4.

Identified control system modelling expressiveness requirements are:

- *Function blocks*: It must be possible to model function blocks such as multipliers or integrators or more com. The components are the basic building blocks of the control system and provide the computational aspect of the models

- Component interaction: As a basic requirement it must be possible to model interaction between different components of the system. This allows for making complex networks of components interacting to create a control system and model the communication aspect of the control system.

- *Runtime reconfiguration*: Control systems could require multiple operation regions or configurations. Having a way to model behavioural change based on model values allows for expressing choice. The co-ordination can be used to model multi-agent systems, safety layers or startup and shutdown effects. Two types of runtime reconfiguration can be distinguished, influencing configuration parameters of a function block during execution and influencing the active processing path within multiple parallel processing paths. Both are required for modelling control systems.

#### 3.1.2 Model Analysis Requirements

Verification of the supplied model is required on non-functional aspects to confirm that the control system will not stall during execution.

Latency analysis allows the end user to investigate the influence on the dynamic behaviour of the plant (Jensen et al., 2011).

- *Deadlock*: It must be possible to analyze the system for deadlock problems. No guarantees are possible with a system where a deadlock situation is possible in the control flow.

- Latency: As latency determines for a large part whether the system is stable, it must be possible to view and analyze the latency between different components of the control system. This requires that an actor execution schedule for the system must be constructed. Sufficient knowledge of the target platform by the software is required for the construction of the schedule and the following analysis.

#### 3.1.3 Simulation Requirements

Part of the model verification requires simulations of the model. This allows for determining the response of the model to different situations and determine the functional performance of the control system (Jensen et al., 2011). A number of aspects are required to facilitate the verification of the models for the end user:

- *Plant integration*: Integration of continuous-time plant models via a co-simulation interface provides the end user with a way to support the design flow. Without this integration, the models can not be verified against scenarios representative for real-world usage and will hamper a first-time right realisation (Broenink and Ni, 2012).

- Unit aware: The simulator must allow the end user to take advantage of defining units for different signals (Broenink and Broenink, 2018). This provides additional details to the models to verify signal relations.

Simulation should be possible with multiple levels of detail, depending on the amount of information provided by the platform model. This allows for a trade-off between simulation speed and accuracy for the selected platform.

## 3.2 Dataflow Model of Computation

The selected dataflow MoC must provide the required expressiveness and analysis options suitable for modelling control systems. The requirements described earlier must be satisfied by the MoC. All dataflow models of computation model systems based on a collection of actors and edges between the actors, effectively satisfying the function block and interaction requirements. Runtime choice, deadlock analysis and latency analysis differ for the different models of computation.

| Model of<br>Computation | Deadlock<br>analysis | Latency<br>analysis | Runtime path selection | Runtime reconfiguration |

|-------------------------|----------------------|---------------------|------------------------|-------------------------|

| SDF                     | 1                    | 1                   | ×                      | ×                       |

| CSDF                    | ✓                    | ✓                   | ×                      | ×                       |

| VRDF                    | ×                    | ×                   | ×                      | ✓                       |

| VPDF                    | ×                    | ×                   | ×                      | ✓                       |

| BDF                     | ✓                    | ✓                   | ✓                      | ×                       |

| FSM-SADF                | 1                    | ✓                   | ×                      | ×                       |

| SADF                    | 1                    | 1                   | 1                      | ✓                       |

**Table 3.1:** Requirements versus thedifferent dataflow MoC options

Shown in Table 3.1 are the different dataflow models of computation. Two dataflow models of computation can be selected from the table. The first case when no runtime choice is required, SDF as MoC satisfies the requirements. While CSDF appears to be suitable for this case, it allows for variable consumption and production rates, adding complexity where it is not necessarily required.

When runtime choice is required, SADF satisfies all requirements. To allow for deadlock and latency analysis, the SADF models however need to be limited in their expressiveness. Notably any detector actor must fire only once every cycle. Still with this limitation in place, SADF offers the flexibility required by the control system requirements while retaining the required analysis options.

When runtime choice is not required for the model, the SADF-based graphs can be simplified to SDF graphs without any effort. The main advantage of using SDF instead of SADF as MoC is that it allows for a static scheduler when realizing the model. Simplifying an SADF-based graph to SDF is possible when no detector actors are present in the model.

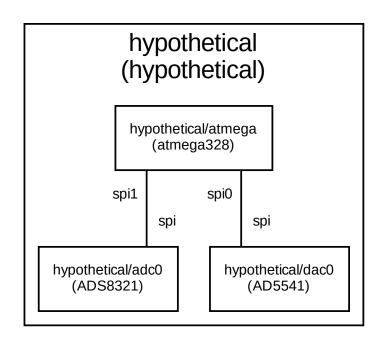

### 3.3 Platform Meta Model

The PMM gives a description complete enough to generate the PSM. It needs to describe the hardware platform in a code-independent way, and provide the information required for both the PSM and the generation of the final platform-specific code. The platform description domain-specific language (DSL) should allow for reuse of components, component timing, and performance specification, furthermore, it must specify a target execution architecture. The information can be categorized into code-generation related information and timing information. The code-generation related information allows for converting the PSM into the platform-specific code. Timing information is required for analysis and simulation of the PSM, while essential for analysis, it is not required for the code generation.

#### 3.3.1 Platform Meta-Model Components

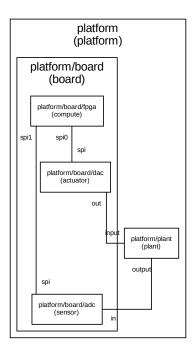

The PMM describes a contained and interconnected set of hardware providing sufficient details for a refinement of the PIM to a PSM. The PMM must allow for describing the required information to allow for sufficient timing analysis on the PSM. It provides a worst-case execution time and a value accuracy specification of the processing units. This allows for more detailed simulations using the additional hardware specification from the platform model on the system model.

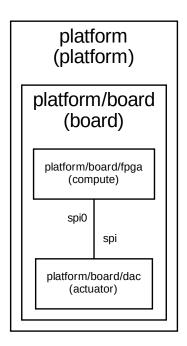

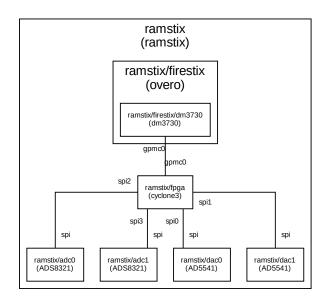

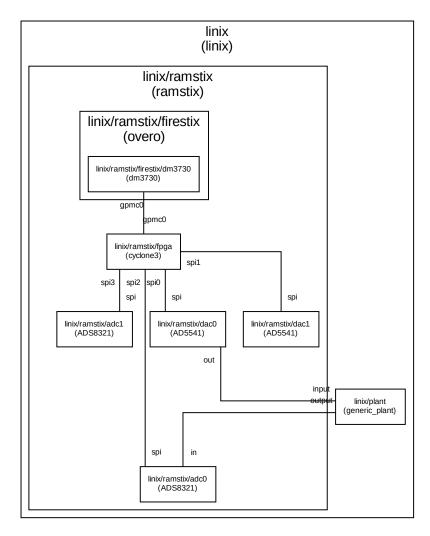

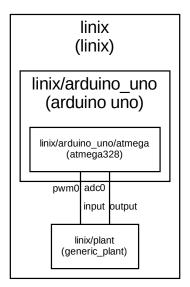

A hierarchical modelling structure describing the components of a hardware platform is required to model the complexities of hardware platforms. Hardware platforms consist of multiple components, the physical components on a platform acting on the data, interconnected to complex structures sometimes containing another different platform as subcomponent. For example, the RaMstix board<sup>1</sup> contains an FPGA and a Gumstix platform.

Different types of components can be identified to simplify the PMM into a set of component-type specific meta-models. Components can to be separated into execution models such as a SoC or FPGA and peripheral based components such as sensors, actuator and communication modules. A short description of each identified component type follows here: <sup>1</sup> https://git.ram.ewi.utwente.nl/ramstix/ramstix

Sensors: The sensor component type provides the properties of different available sensor types. The sensor acts as a boundary between the continuous-time plants and the event-driven function blocks. Main attributes of a sensor are measurement interval, accuracy, and delay. A sensor requires at least one event-driven input to trigger the sensor and one analog input to sample values from.

Actuators: The actuator component type provides the properties required for modelling different actuator types. It acts as a boundary between the event-driven function blocks to the plant models. Attributes used here consist of update interval, accuracy and delay. Actuators require at least one analog output and at least one event-driven value input.

*Compute modules*: These modules consist of components such as microcontrollers and FPGAs. They allow for allocating multiple function blocks on them to be scheduled within the same processing unit.

*Plants*: A component representing the dynamic system of which the behaviour is steered by the control system. The plant models can include additional components to aid the plant connectors such as built-in actuators or sensors.

From the components described above two structures can be derived:

*Boards*: Boards represent components containing multiple interfaces and one or more compute modules. A board can inherit (contain) different other boards, modules and components. The structure of a board allows for a hierarchical description of the components.

*Platform*: A platform is the final structure consisting of at least a single board. The platform defines the full configuration for a single model and is to be used as a target for a model. A platform can include plants.

Interfaces provide the meta-model framework for describing ports on different modules. The interface provides the additional information required to model the properties of the interconnection between the components. Different types of interfaces provide different properties here and the type of interface is dictated by the physical implementation of the component.

An example platform model is shown in Figure 3.1. It consists of a platform containing connecting a board component with a plant component. The board contains a compute module, a sensor and an actuator. In the example, the different components are named (shown between parentheses) after their specific component types. Interfaces provided by the components are used to connect the components with each other.

**Figure 3.1:** Platform model containing a plant and a board. The board contains a compute module, an actuator and a sensor connected to each other via their interfaces.

## 4 Design Requirements

A large part of the work consist of a tool design as a proof of principle for the proposed workflow and design paradigms. Both the application itself and the input files required for the application must adhere to a set of requirements. The requirements formulated here are based on the research questions and analysis results.

## 4.1 Application design

The application requirements are split into a number of different categories.

- The model backend specifies the requirements for the dataflow based model processing.

- The model analysis builds upon this and specifies which analysis is required for the models for verification of the models.

- The simulation requirements specify the requirements on the simulation of the models and which results are expected from the simulations by the engineer.

#### 4.1.1 Model backend

# **Requirement 1:** The application must use scenario-aware dataflow as dataflow MoC

The choice in model backend dictates the restrictions on the modelling freedom and which analysis is available for the models. Based on the exploration of the different dataflow MoCs, SADF fits the current approach. As discussed in Chapter 3, It allows a limited notion of choice within the model. With the limitations preventing Turing-completeness, it allows for sufficient analysis of the models. Having this in the application allows for supervisory control by modifying the state of actors during run-time. The consistency and deadlock analysis from SADF can be used on the models for formal verification of these aspects. While it does not put any guarantees on the functionality of the model, it allows for proving that the model will not deadlock at some point in time.

# **Requirement 2:** The application must be able to operate on physical quantities

It must be aware of the relation between different quantities and units of measure. The advantage is that it allows for expressing models with the physical quantities included, increasing the ease of use for the end user by removing the need for converting measurements and setpoints to opaque values. The addition of physical quantities to the model adds another layer of verification by restricting operations to adhere to the rules of dimensional analysis.

#### 4.1.2 Model analysis

The goal of the model analysis is to verify a number of essential properties of the model. This to ensure that the modelled system is able to execute indefinitely without running into memory constraints.

**Requirement 3:** The application must be able to formally verify whether the dataflow equivalent of the model is consistent

Without this verification, a cyclic dependency will either deadlock or use unbounded FIFO space. If this is the case, the model can not be run indefinitely and will crash the execution platform either by deadlocking or by consuming too much memory.

# **Requirement 4:** The application must be able to prove that the supplied model is deadlock free.

The second requirement is that every cycle must be proven to have enough tokens available to be deadlock free. Together with the proof that the model is consistent, this ensures that the model can run indefinitely without deadlock. This is essential for long running applications.

**Requirement 5:** The application should be able to prove whether clock elements are the limiting factor in throughput for a model

This requirement allows the application to formally verify that token throughput of the system is limited by tasks representing periodic clocks in the models, in other words, all components in the system have at most an execution time equal to a clock element. When the token throughput of the dataflow model is not limited at the clock, it is limited at a component too slow for the configured clock frequency.

#### 4.1.3 Model Simulation

**Requirement 6:** The simulation must allow for verification of the functional aspects of the model

One of the goals of the application is to allow the engineer not only analysis of the models, but also verification of the functionality of the models. This is essential for a performance-based comparison between the PIM and the PSM. To allow for this, the simulator must be able to produce results based on an execution.

**Requirement 6.1:** A computational model must be supported by the simulator for function blocks

For the model to simulate signals and events, a computational aspect is required to calculate values of the produced tokens. Detector function blocks depend on the token values for the selection of the emitted state token. This adds a hard requirement for including computational models in the dataflow-based actors.

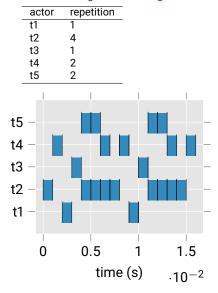

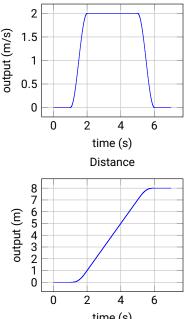

# **Requirement 6.2:** A time-series output of one or more signals from a simulation must be available as output.

Visualization of time-series allows for a convenient way to show the engineer signal traces from the simulation run. This helps with comparisons between different configurations of the model and allows for verification of the model functionality.

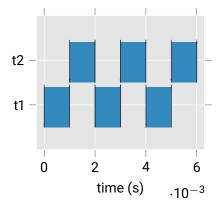

# **Requirement 6.3:** A graph of execution times of the different model components must be available as output.

Within a complex model, it might not be directly clear how component dependencies are structured. An overview of actor execution times allow for visualization of component dependencies and timing schedules. It allows for identifying components with a significant impact on the performance.

**Requirement 6.4:** It should be possible to include computational models for plants in the system

Including support for plant-representing models in the tool adds significant value. It allows for more in depth confirmation of the functionality of the model by including the plant in the simulation. However, plant models do not convert properly to SADF semantics. Foremost as continuous-time models are not suitable for conversion due to the event-based nature of Dataflow. To allow for simulation including these continuous-time models, either the edges to and from plants require adaptation to facilitate the conversion, or the plant models themselves require to be adapted to event-based models.

#### 4.1.4 Model-to-model conversion

The goal of the model-to-model conversions is to refine the supplied PIM to PSM.

**Requirement 7:** It must be possible to specify a component for each system-model function block as target for conversion

Converting platform-independent function blocks to a model representing the physical component on a system requires information on this conversion. One of the steps is to have a specification of function blocks to component mappings, otherwise the engineer has no control over the distribution of functionality over the physical system. Depending on the type of the function block, the specified component must be restricted to a compute component, a sensor, or an actuator.

**Requirement 8:** The conversion must be able to adapt the execution times and the resolution of the function blocks to a value representative for the matching physical components.

By adapting the execution times the function blocks match the worstcase execution time on the specified hardware. This can be an estimated worst-case execution time, in the case the component is only able to guarantee a maximum execution time, or a precise duration when the platform is able to guarantee an exact execution time.

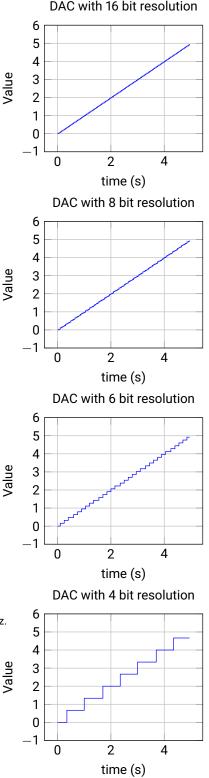

**Requirement 9:** The conversion must be able to adapt the resolution and bounds of output values of a function block.

Depending on the hardware specification, output values of the function must be limited in resolution and/or bounded between minimum and maximum values. This to represent conversion hardware with limited resolution such as D/A- and A/D-converters

**Requirement 10:** The modelled connection between the mapped hardware components must be included in the model.

Depending on the specified hardware communication interface, the communication latency between two components is significant enough to influence the system behaviour and must be included in the PSM. The non-zero delays caused by communication systems can significantly influence the performance of the system.

The generated PSM must allow for identical analysis as the PIM, to allow for performance comparison between the PIM and different PSMs This includes a generated dataflow representation of the PSM to show the generated data dependencies between different components and identify performance limiting components.

## 4.2 Language design

The input of the tool consists of descriptions of the system models and the platform models. These model files contain detailed specifications of the models, with specifications such as component specification and interconnections. This can be implemented by a structured domain-specific language for describing the models.

# **Requirement 11:** Both the model language and the hardware description should be both human and machine readable

This allows for both writing models manually as well as generating or converting them from an external application. Extending the tool becomes an exercise in generating the model files. While it is shown that it is possible to have a human readable format compiled to a machine readable format, it is chosen to keep a single format for simplicity instead of requiring an additional conversion application. A middle ground between machine readable and human readable is thus required.

Requirements for the model description and the platform descriptions are similar in their requirements, both must specify blocks with identifiers, properties and connections.

#### 4.2.1 Model description

These requirements specify the functionality of the system modelling language required.

**Requirement 12:** The model description must allow for describing a collection of function blocks including configuration.

To satisfy the re-usability of components, the language must be able to specify a function block type. The model description must be able to specify configuration parameters of a function block, as function blocks must be reusable with only requiring modification of the configuration of the function block. Some of these configuration parameters can be optional, others mandatory, depending on the function block.

**Requirement 12.1:** The model description language must be able to specify connections between function blocks including properties of these connections.

Not only must it be possible to specify the relation between the function blocks, it must be possible to specify a set of initial values for an function block input, otherwise it is impossible to create a loop without deadlocks.

#### 4.2.2 Hardware description design

The hardware description is on a high level similar to the model description.

**Requirement 13:** The description language must allow for describing physical components with specifications and interfaces.

The hardware description must contain a specification of the components, describing the parameters of the components. The goal is to be able to directly copy them from the component vendor datasheets.

**Requirement 13.1:** Component interconnections must also be part of the specification.

Without this, the relation between different components of a platform can not be specified. To transfor a model, information about the relation between the different components and which communications interface is used must be part of the specification. **Requirement 13.2:** it must be possible to describe a component as a collection of components.

This requirement facilitates the reuse of component descriptions. For example, a board with an FPGA and a number of sensors and actuators must be specified as a component containing include-like statements for the separate FPGA, sensor and actuator specification.

## 5 Implementation

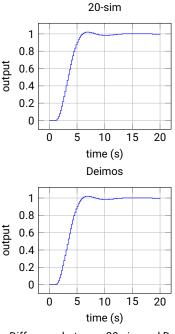

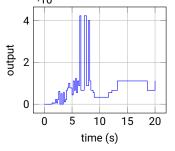

The tool created, Deimos, consists of a collection of functions to model, convert, analyze and simulate complex dataflow based systems. Deimos is named after the second moon of the planet Mars.

First the approach of how systems are modelled with Deimos is described, describing the function blocks and describing how the model files are designed and processed around these function blocks. Later the simulator itself is thoroughly explained. At last the conversion method from a PIM to a PSM is described.

## 5.1 Function blocks

Function blocks are the components of which the system is build upon based on the system model. Each function block, when instantiated, represent some functionality of the system. For example, this can be computational operations executed by the controller or some interface providing conversion between data formats. The building blocks of the models contain computational functionality to provide not only a timing analysis but also functional simulation of the modelled system.

When instantiating function blocks, Deimos can use multiple locations to look for the specified function block type. This ensures an extensible library where function blocks specific for a single model can be added separate from the main library. A function block can be represented by either a single dataflow actor, or as a composite block using multiple dataflow actors. Every dataflow actor representing function blocks is automatically created with a self edge to prevent unwanted concurrent execution of the actor.

A single function block requires the information contained in the supplied model and an implementation to function. A function block requires a number of properties:

- Inputs and outputs

- Data type

- Function block instantiation

- Computational functions

- Parameters

These property requirements can be split into communication, configuration and computational properties.

#### 5.1.1 Communication

The input and output ports of a function block dictate which connections the function block can have with other function blocks within a model. All input ports must be connected to an output port, but not all output ports within a function block have to be connected. Output ports that do not have a connected input port discard their produced tokens. Output ports that have multiple connected input ports duplicate their produced tokens to all connected input ports. It is valid for an input to be connected to the output of the same function block, however care must be taken to ensure that enough initial tokens are available on the connection as not to cause a deadlock. As an exception to this, the input for state tokens is only added and required when states are used with the function block. As to adhere to the dataflow model, function blocks are executed by the simulator as soon as all inputs have the required number of tokens.

#### 5.1.2 Configuration

Parameters provide the configurational aspect of the function block and provide the flexibility in the models. The parameters directly determine the required set of parameters in the system model, from which the values can be requested at run-time. Function blocks can parse a parameters both as plain value or with interpreted physical dimensions.

Parameters can be supplied with dimensionality included such as lengths, time, speed, current and voltage. Calculations using these parameters will propagate the units and will detect errors when the operands of an operations have incompatible units. For example, it is possible to sum different lengths such as meters, centimeters and inches. In this case conversion will happen automatically. However, adding units with different dimensionality will result in an error condition.

#### 5.1.3 Computational functionality

The computational functionality is added to a function block by implementing at least two functions of the python model class. This allows for the model to add computational aspects to the system model, allowing verification of the functional aspect of the system.

First is the initialization of the function block. While not strictly necessary, it allows for functional verification of the parameters and the instantiation of the initial values.

Second is the step function, handling the computational aspect of the model. It calculates the output of the function block based on the inputs and the state of the function block. The step function is supplied with the current start time and the input tokens. Based on these arguments, a finish time and a new set of output tokens is produced and returned to the simulator.

For example, the multiply-accumulate function gathers the input tokens from each input, multiplies them with the respective factors and sums the results. The finish time of the function is calculated by adding the worst-case execution time to the start time. This result is returned to the simulator. For this to work, the input tokens multiplied with their factors must all have the same dimensionality, otherwise summing them is not possible.

## 5.2 System meta-model

The system meta-model (SMM) provides a structure to describe system models as a system of interconnected function blocks. It must provide a framework to desribe the function blocks as described above with all required options. The meta-model designed for the systems is based on the both machine and human readable YAML Ain't Markup Language (YAML) specification (Ben-Kiki et al., 2005). This allows for models written directly by the engineer or generated by external tools. The YAML specification satisfies requirement 11.

A full model is based on a description of a set of interconnected function blocks. These function blocks define the different components of the system. Based on the input model description, the tool instantiates the function blocks configured and connected as specified by the model.

The SMM requires a number of values to instantiate a function block from:

- Name: An unique name to identify the function with. Used as an identifier to distinguish functions within the model.

- Type: The type of the block, used to identify and select the computational model for the function.

- Parameters: A dictionary of parameters to configure the function. The required parameters depend on the computational model of the function.

- Inputs: A dictionary of inputs, used to specify connections between the blocks. The inputs specify to which output port a specific input port of a function is connected. It also allows for specifying a set of initial tokens for the input port.

An example function specification of an proportional-integral-derivative (PID) controller is shown in listing 5.1. It shows a function block named PID using the computational model of the type pid. The parameters of the PID controller are specified, including the worst case execution time (the wcet parameter defined as 0ms).

| 1  | PID: #            | Name of the function block |

|----|-------------------|----------------------------|

| 2  | type: pid #       | Model identifier           |

| 3  | params: #         | Configuration parameters   |

| 4  | <b>kp</b> : 0.2   |                            |

| 5  | ti: 0.5           |                            |

| 6  | td: 0.1           |                            |

| 7  | beta: 0.2         |                            |

| 8  | wcet: 0ms         |                            |

| 9  | inputs: #         | Input port connections     |

| 10 | in:               |                            |

| 11 | source: Error.out |                            |

| 12 | states: #         | Control states             |

| 13 | safe: #           | `safe' state               |

| 14 | params: #         | Config parameters to       |

| 15 | ti: 0 #           | override with this         |

| 16 | td: 0.0001 #      | state                      |

Listing 5.1: Example function block specification of an PID controller

The behaviour of a function can be influenced at run-time by signalling states to the function. When used, every execution requires a token specifying the execution state of the function. This state is used to override the parameters of the function to the state-specific parameters. Special detector based function blocks emit these state tokens to influence the run-time behaviour of the model.

## 5.3 Plant integration

Plant models can be added to the system model as a functional block representing the plant. Similar to regular function blocks they have inputs and outputs, but opposed to the regular function blocks, plants can not be modelled with an SADF model.

Two types of plant models are available for use, a continuous-time transfer function based plant and an external plant importer. The trans-

fer function based plant allows for adding simple continuous-time functions. It does not have advanced capabilities, it allows however for rapid development to the plant during iteration cycles as it does not require an externally created plant model. The external import based plant model is using the Functional Mock-up Interface (FMI) specification (Blochwitz et al., 2012). Functional Mock-up Unit (FMU) based files can be specified and integrated into the model, their inputs and outputs can be connected to other function blocks.

The plant configuration requires specifying for each input and output the physical dimensions required by the port.

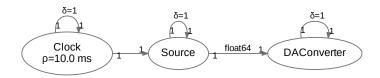

The main challenge with plant representing function blocks is that a plant does not adhere to SADF semantics. Analysis and simulation are adapted to take this into account. When modelling the pure SADF representation of the model, plants are omitted from the model.

#### 5.3.1 Model rendering

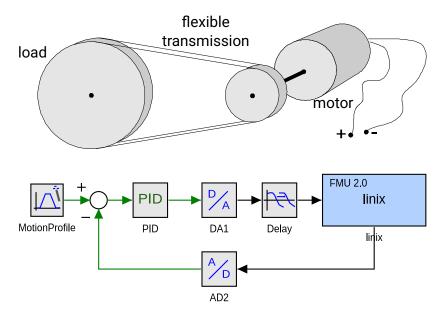

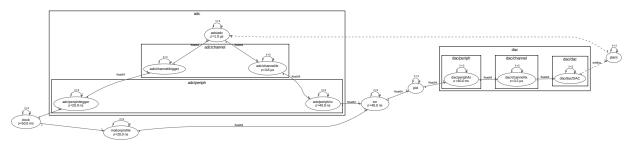

A full system model as described by the model files can be displayed as a collection of function blocks with connections. Deimos includes options for rendering a block representation of the model. This allows for initial testing of the system model description, by allowing the engineer compare the generated model properties and connections with the expected system. Figure 5.1 shows the output of such a render for a simple PID based control loop with a plant included.

**Figure 5.1:** Block diagram of a PID based control loop

## 5.4 Model analysis

The SADF model as constructed internally by Deimos allows for verification of a number of properties. Before any simulation is done on the model, it is first checked whether the model is consistent and deadlockfree.

The analysis is done using an implementation of the definitions and theorems applicable to SADF graphs (Theelen et al., 2006). Required for this analysis is that the dataflow representation of the model is both strongly dependent and strongly consistent. This requirement allows for formal verification of the absence of deadlocks within the model.

The implementation first determines the non-trivial repetition vector of the SADF graph. For this, the full matrix of token consumption and production for every tuple of actors and the states of that actor is build. With this matrix, the repetition vector of the graph can be solved from the matrix.

For this to hold it is required that the production and consumption rates of tokens only depends on the parameters of a function block. The rates must not be time-dependent or dependent on an internal state of the function block.

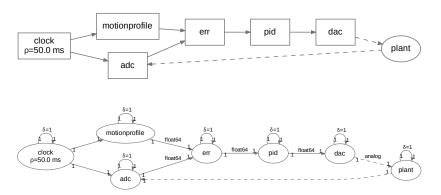

Within this analysis, plants are excluded, this as they do not follow dataflow-based simulation rules, but also do not influence the activation condition of the dataflow-based actors. They can be excluded

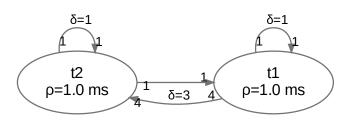

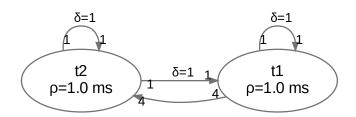

from the model analysis, a plant will never block the execution of a actor connected to a plant. Within the analysis, the model from figure 5.2 is converted to the model from figure 5.3.

**Figure 5.2:** SDF model of a PID based control loop extended with analog components

#### 5.4.1 SDF based models

**Figure 5.3:** SDF model of a PID based control loop

#### 5.5 Model simulation

Simulation of the system is based on SADF token interaction between the different function blocks. The simulator works as a discrete-event based system, executing function blocks from an execution queue. The main advantage is that this results in a fast simulator design with a flexible time step based on the granularity of the actors. Function blocks are always executed in sequence and causal in time.

The simulator maintains an internal time stamp which contains the simulator time stamp of the last started function block. To determine the next function block to simulate, the execution queue is sorted and the function block that has the lowest start time stamp among function blocks in the queue is executed.

After a function block is executed, every connected function block is checked for readyness. Every function block that is determined to be ready is added to the execution queue.

The start time of a function block is based on the production time of the token that caused the function block to become ready. At the simulation start, all function blocks are checked for readyness to set the initial execution queue.

The simulator works with a number of rules on which the simulation algorithm is based

- A function block is considered ready when all inputs contain at least the minimum amount of tokens required for the function block to execute.

- For every function block p, the simulator maintains a boolean indicating if the function block is ready to execute.

- 3. A function block that is executed has an associated execution start time  $t_{start}$  and an execution stop time  $t_{end}$

- 4. A function block *p* has a possible empty set of function blocks *R* such that there is an output from *p* to at least one input of every function block in *R*.

- 5. After a function block p has fired, for every function block p' in R it is checked if the function block is ready. Every function block

that became ready receives a start time  $t_{start}$  equal to  $t_{end}$  of p and is added to the execution queue.

6. The function block in the execution queue with the lowest value for *t*<sub>end</sub> is executed next.

While it is not required to simulate actor execution in order of their lowest starting time, it is required for the synchronization with an external simulation.

#### 5.5.1 Co-simulation synchronization scheme

To allow for a simulation with a continuous time based plant, a cosimulation interface is available within Deimos. The interface, based on the FMI specification, requires synchronisation with the event-based simulation for proper interaction between the models.

Synchronization between the event-based system model and the plant is based on a lock-step simulation using token interaction to exchange state between the models(Nicolescu et al., 2007). The value of the token is always set to the output value of the plant at the time the function block consumes the token. This ensures that a function block consuming tokens from the plant always receives the output of the plant at the time the value is used, removing the FIFO-based nature of dataflow edges.

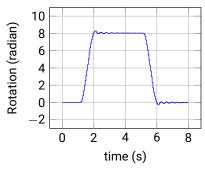

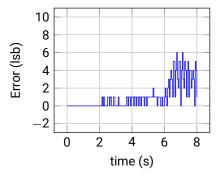

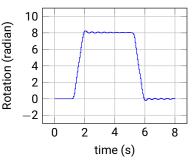

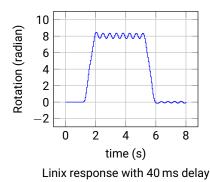

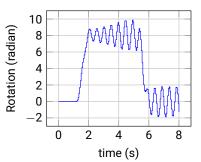

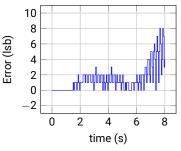

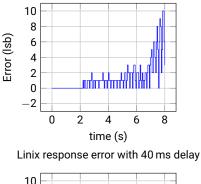

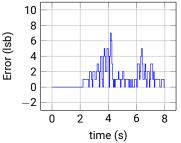

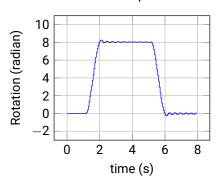

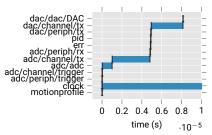

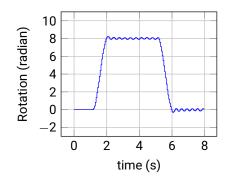

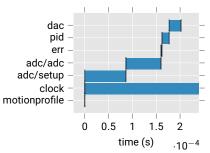

The token interaction between the system and the plant is not based on SADF, the non-blocking nature of a continuous time model does not fit the SADF modelling restrictions. A modified behaviour is used where the plant is always able to consume an infinite amount of tokens and always has tokens available for the component consuming from the plant. This way, a functional block representing a digital-toanalog converter is always allowed to specify input values to the plant. Furthermore, an analog-to-digital converter can always sample a value from the plant by consuming a token and reading the value from the token.