# Verification of a SysML Railway Specification with a Translation to UPPAAL

# Wijtse Rekker

Supervised by Djurre van der Wal

LaTeX Template "The Legrand Orange Book" by Mathias Legrand [21]

UNIVERSITY OF TWENTE

February 2021

# Contents

| 1     | Introduction             | 11 |

|-------|--------------------------|----|

| 2     | Research questions       | 15 |

| 2.1   | Clarification            | 15 |

| 3     | Related work             | 17 |

| 4     | Background               | 19 |

| 4.1   | EULYNX                   | 19 |

| 4.2   | UPPAAL                   | 23 |

| 4.2.1 | Input language           | 23 |

| 4.2.2 | Input files              | 24 |

| 4.2.3 | Requirement language     | 27 |

| 4.2.4 | Diagnostics              | 28 |

| 4.2.5 | Verification algorithm   | 28 |

| 4.3   | mCRL2                    | 30 |

| 4.3.1 | Input language           | 30 |

| 4.3.2 | Requirement language     | 32 |

| 4.3.3 | Diagnostics              | 33 |

| 4.4   | UPPAAL compared to mCRL2 | 35 |

| 4.4.1 | Modelling language       | 35 |

| 4.4.2 | Requirement language     | 35 |

| 4.4.3 | Diagnostics              | 36 |

| 5              | Translation                                                                                                                 | 37       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------|----------|

| 5.1            | Possible EULYNX interpretations                                                                                             | 37       |

| 5.1.1          | State machine interleavings                                                                                                 | 37       |

| 5.1.2          | Memory sharing                                                                                                              |          |

| 5.1.3          |                                                                                                                             |          |

| 5.2            | General design                                                                                                              | 39       |

| 5.2.1          | Existing solutions                                                                                                          | 40       |

| 5.3            | Structure                                                                                                                   | 40       |

| 5.3.1          | State machines as processes                                                                                                 | 41       |

| 5.3.2<br>5.3.3 | Event managers                                                                                                              | 43<br>46 |

| 5.3.4          | Orchestrator                                                                                                                |          |

| 5.3.5          | Data management                                                                                                             |          |

| 5.4            | Translation steps                                                                                                           | 48       |

| 5.5            | Translation of basic elements                                                                                               | 50       |

| 5.5.1          | Simple state                                                                                                                |          |

| 5.5.2          | Transition                                                                                                                  | 50       |

| 5.5.3          | Internal behaviour                                                                                                          |          |

| 5.5.4          | Composite state                                                                                                             | 51       |

| 5.6            | Element naming                                                                                                              | 55       |

| 6              | Validation                                                                                                                  | 57       |

| 6.1            | Test suite coverage                                                                                                         | 57       |

| 6.2            | Test cases                                                                                                                  | 57       |

| 6.2.1          | Transition Guards                                                                                                           |          |

| 6.2.2          |                                                                                                                             | 60       |

| 6.2.3<br>6.2.4 | Trigger events                                                                                                              |          |

| 6.2.5          | After events                                                                                                                |          |

| 6.2.6          | Entry and exit behaviour                                                                                                    |          |

| 6.2.7          | Composite states                                                                                                            | 69       |

| 6.2.8          | Junction vertices                                                                                                           | 73       |

| 7              | Usability                                                                                                                   | 75       |

| 7.1            | Point overview                                                                                                              | 75       |

| 7.2            | Requirement specification                                                                                                   | 76       |

| 7.3            | UPPAAL property specification                                                                                               | 78       |

| 7.4            | Results                                                                                                                     | 80       |

| 8              | Discussion                                                                                                                  | 87       |

| 8.1            | Sub research questions                                                                                                      | 87       |

| 8.1.1          | a) Which interpretations of EULYNX fit the goals of the translation to UPPAAL best?                                         | 87       |

| 8.1.2          | b) Is the translation to UPPAAL correct?                                                                                    | 88       |

| 8.1.3          | c) How well can the output models be used to verify model requirements?                                                     |          |

| 8.1.4          | d) How well can the input models of the translation scale in size and complexity such t UPPAAL is still able to check them? |          |

| 8.2<br>8.3<br>8.4 | Translation improvements<br>Main research question<br>General remarks                                                            | 90<br>91<br>91    |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 9                 | Conclusion                                                                                                                       | . 93              |

| 10                | Future work                                                                                                                      | . 95              |

|                   | Performance improvements Static location reduction Process synchronisation Separating cycles                                     | . 97              |

| 11                | References                                                                                                                       | 101               |

| 12<br>A<br>B      | Appendices<br>EULYNX functions of Torch<br>Output UPPAAL model for the guard test example                                        | 105<br>105<br>106 |

| C<br>D<br>E       | State machine diagrams of the Point model<br>Detailed Point requirement descriptions<br>Example simulation trace of SP in UPPAAL | 108<br>113<br>121 |

# **List of Tables**

| 4.1<br>4.2<br>4.3 | Moddeling in UPPAAL compared to mCRL2Requirement specification in UPPAAL compared to mCRL2Diagnostics in UPPAAL compared to mCRL2 | 36         |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------|

| 6.1<br>6.2        | Traceability matrix of feature validation                                                                                         |            |

| 7.1               | Requirements for the Point model                                                                                                  | 77         |

| 7.2               | Detailed description of R1                                                                                                        | 78         |

| 7.3               | UPPAAL version of the requirements for the Point model                                                                            | 79         |

| 7.4               | UPPAAL result summary of the requirements for the Point model.                                                                    | 86         |

| 12.1<br>12.2      |                                                                                                                                   | 113<br>114 |

| 12.3              | -                                                                                                                                 | 114        |

| 12.4              |                                                                                                                                   | 115        |

| 12.5              |                                                                                                                                   | 116        |

| 12.6              | •                                                                                                                                 | 116        |

| 12.7              |                                                                                                                                   | 117        |

| 12.8              | Detailed description of R8                                                                                                        | 118        |

| 12.9              | Detailed description of R9                                                                                                        | 118        |

| 12.1              | 0 Detailed description of R10                                                                                                     | 119        |

| 12.1              | 1 Detailed description of R11                                                                                                     | 119        |

| 12.1              | 2 Detailed description of R12                                                                                                     | 120        |

# **List of Figures**

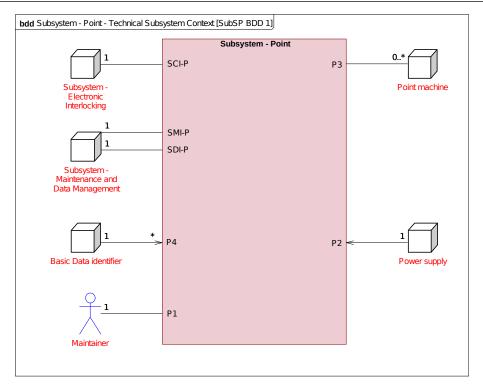

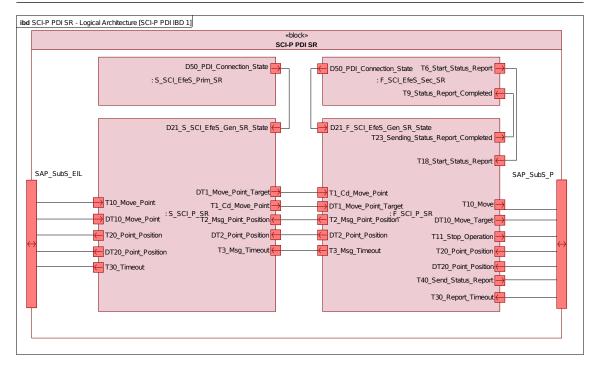

| 4.1  | EULYNX Viking IBD                                                     | 20 |

|------|-----------------------------------------------------------------------|----|

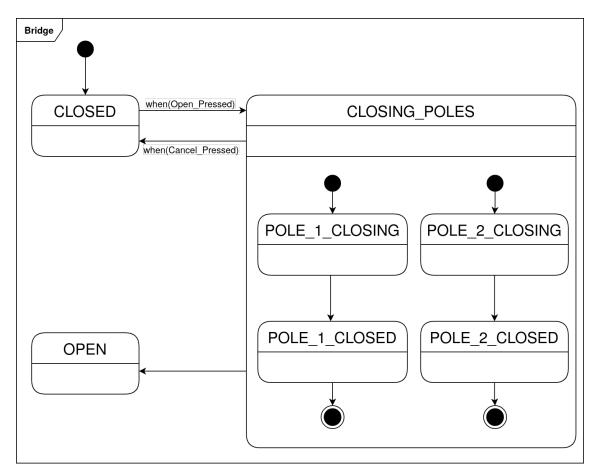

| 4.2  | Viking state machine in EULYNX                                        | 21 |

| 4.3  | EULYNX Torch IBD                                                      | 22 |

| 4.4  | Vikings and Torch IBD composition in EULYNX                           | 22 |

| 4.5  | Vikings and Torch IBD composition in EULYNX                           | 23 |

| 4.6  | UPPAAL model view of the bridge example                               | 24 |

| 4.7  | Trace view of the vikings example.                                    | 29 |

| 4.8  | Model view of the vending machine example in mCRL2                    | 33 |

| 4.9  | Diagnostic trace view of a requirement of the vending machine example | 34 |

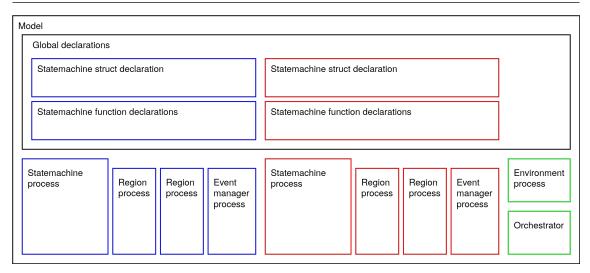

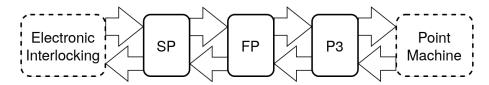

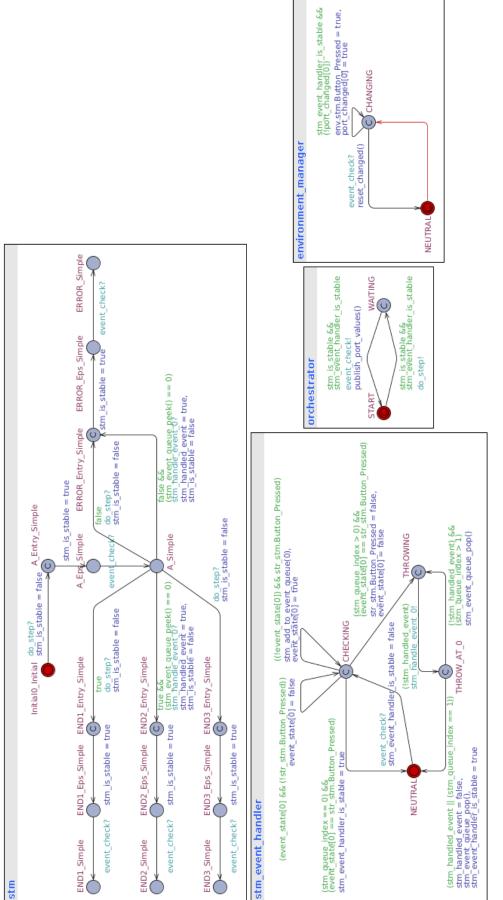

| 5.1  | Model architecture                                                    | 41 |

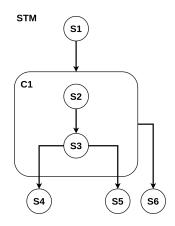

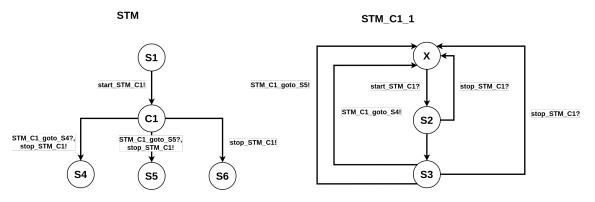

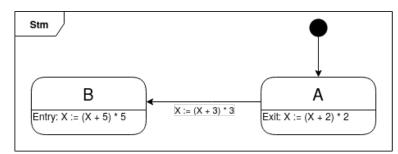

| 5.2  | Simple composite state example                                        | 42 |

| 5.3  | Simple composite state example in UPPAAL                              | 42 |

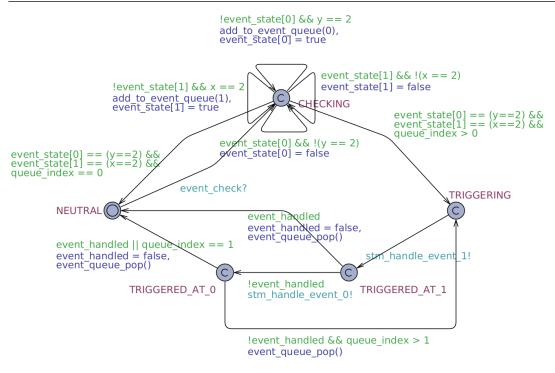

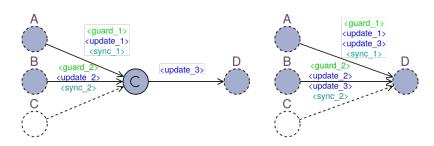

| 5.4  | Event manager example                                                 | 44 |

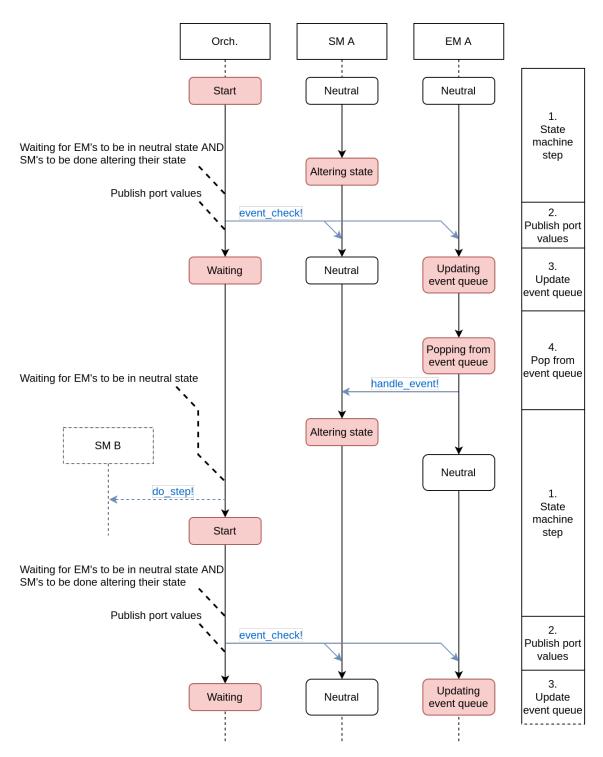

| 5.5  | State machine orchestration                                           | 45 |

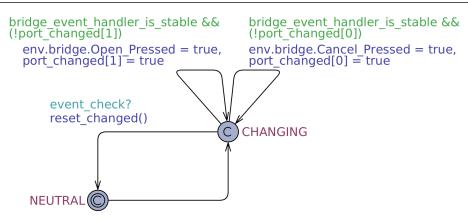

| 5.6  | Environment process                                                   | 46 |

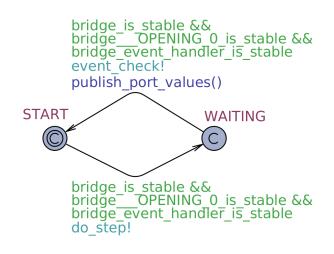

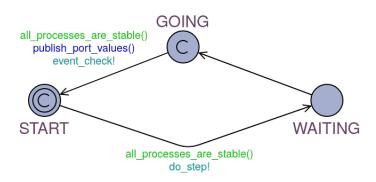

| 5.7  | Orchestrator process                                                  | 47 |

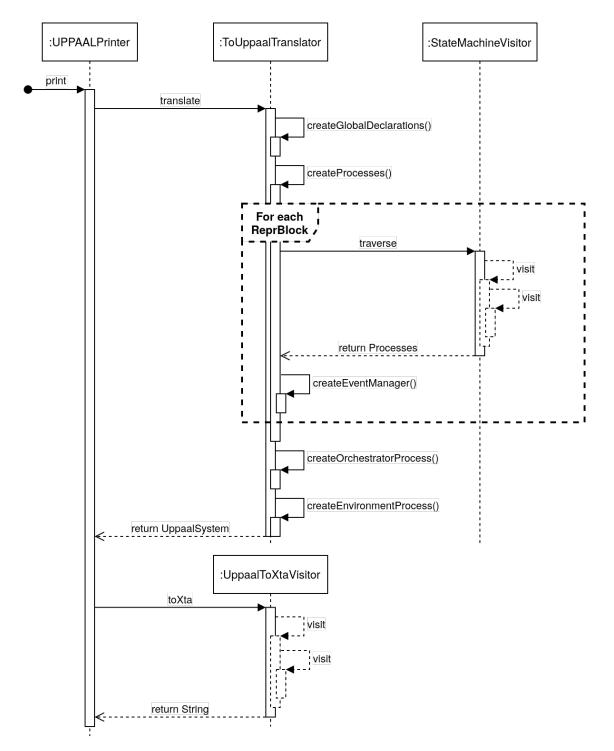

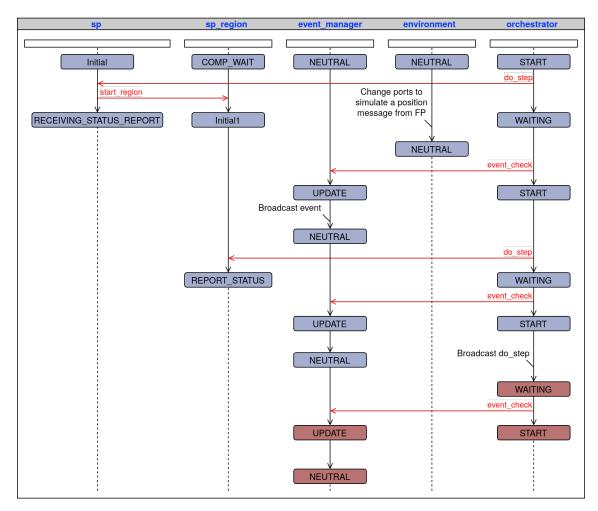

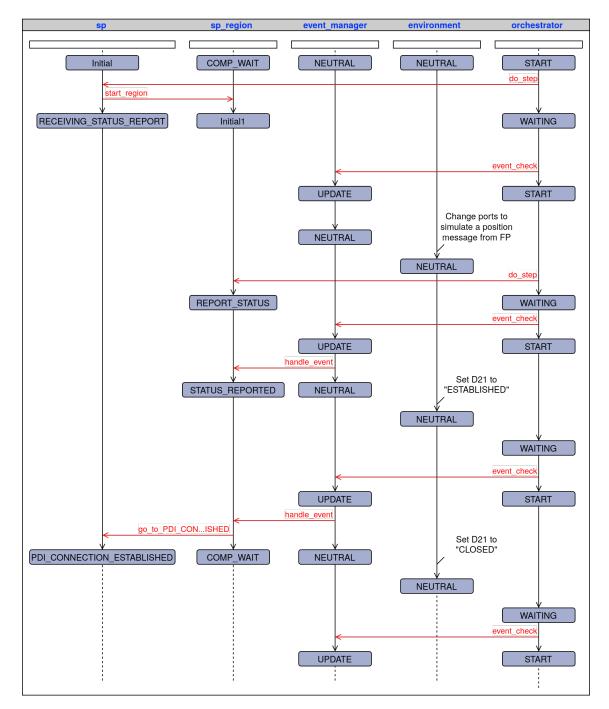

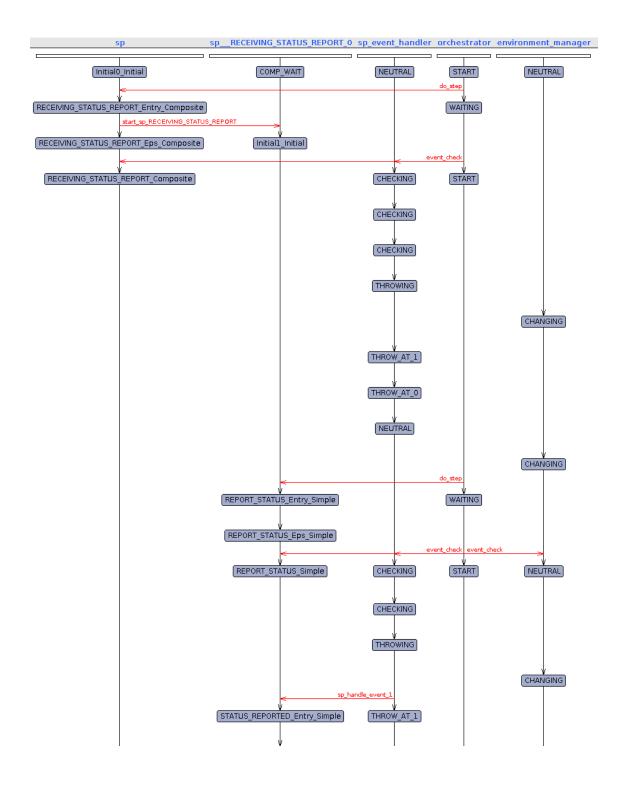

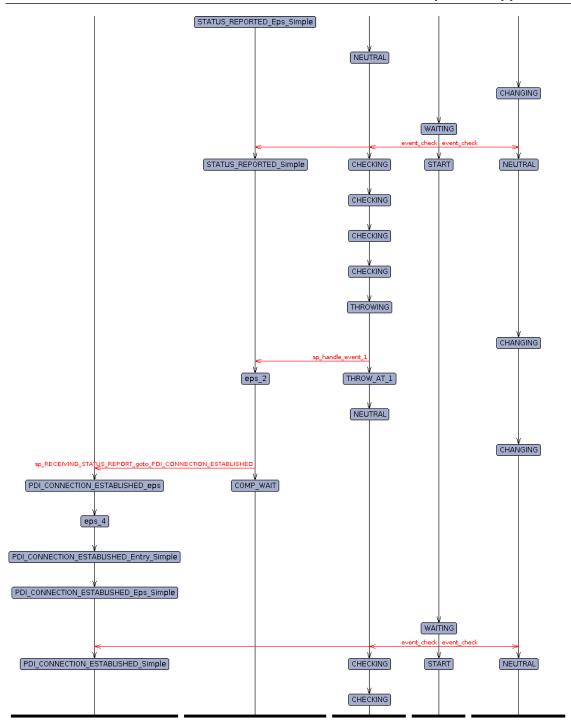

| 5.8  | Translator sequence diagram                                           |    |

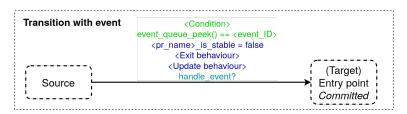

| 5.9  | Transition with event translation to UPPAAL                           | 52 |

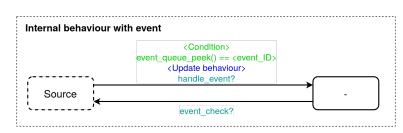

| 5.10 | Internal behaviour with event translation to UPPAAL                   |    |

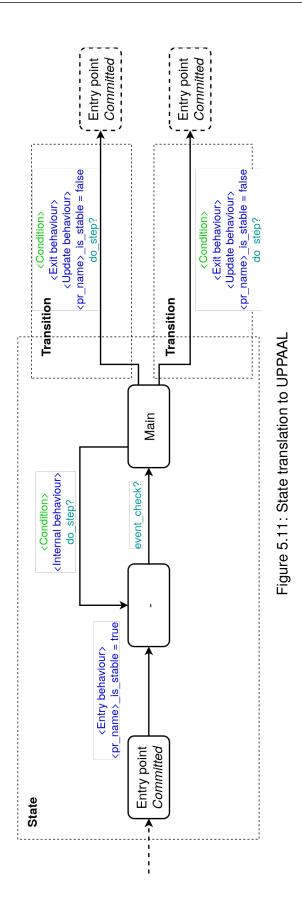

| 5.11 | State translation to UPPAAL                                           | 53 |

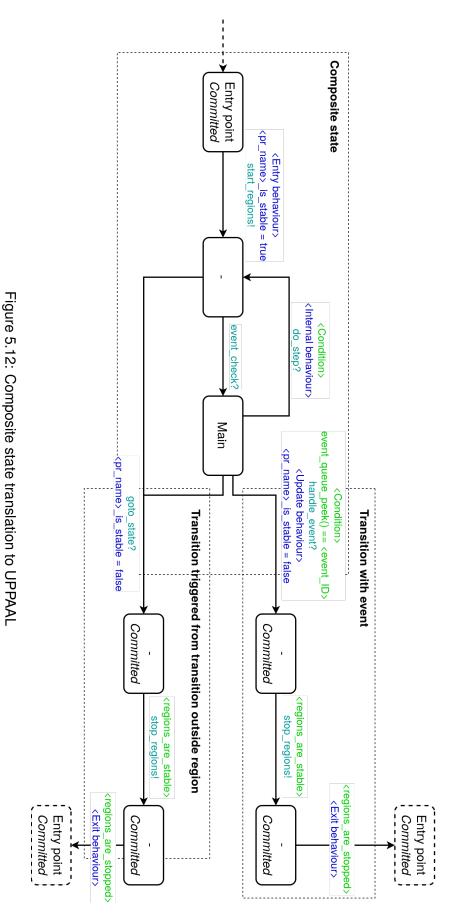

| 5.12 | Composite state translation to UPPAAL                                 | 54 |

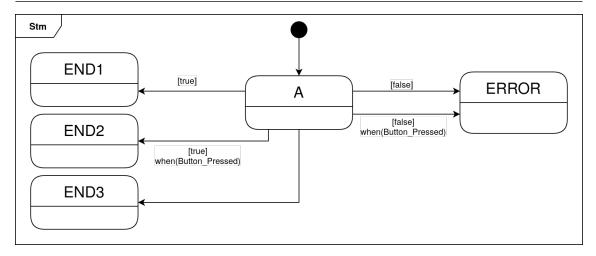

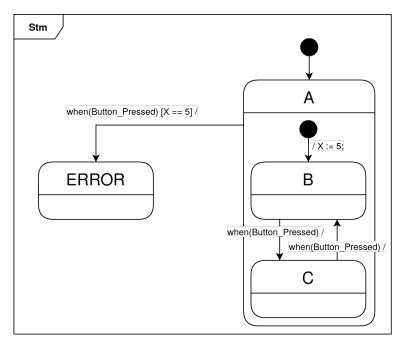

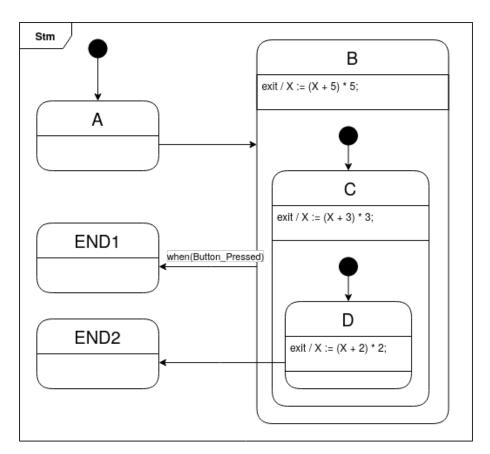

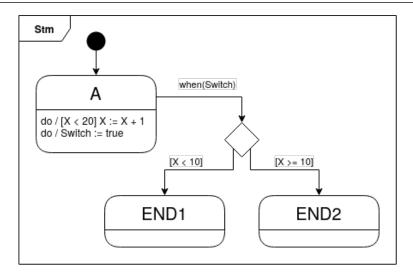

| 6.1  | Test model for guards                                                 | 59 |

| 6.2  | Results of guard test model properties                                |    |

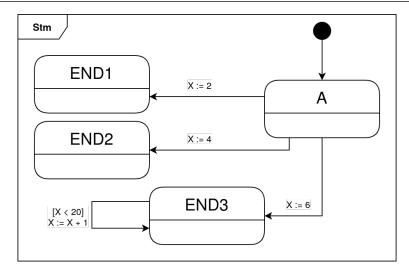

| 6.3  | Test model for transition effects                                     | 61 |

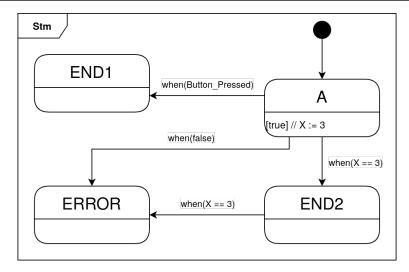

| 6.4  | Test model for events                                                 |    |

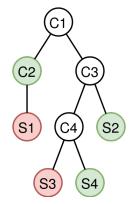

| 6.5  | Example active state configuration tree                               |    |

| 6.6  | Test model for handling events at different levels                    | 63 |

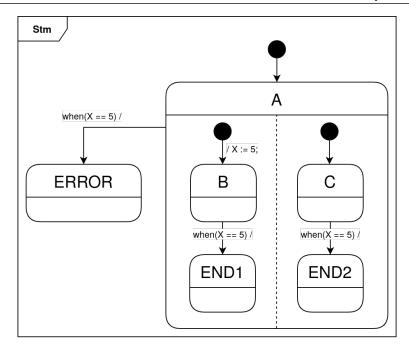

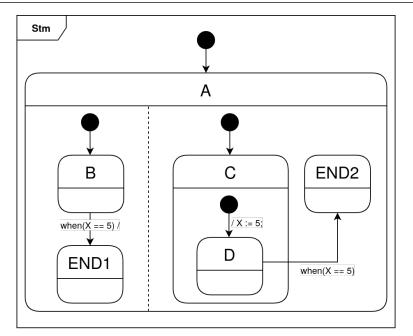

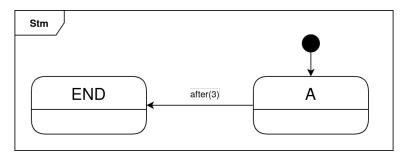

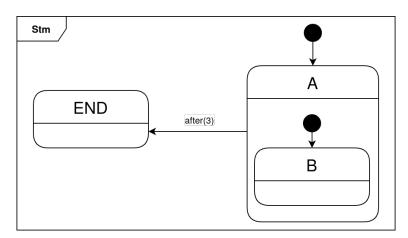

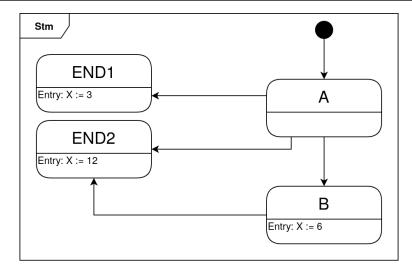

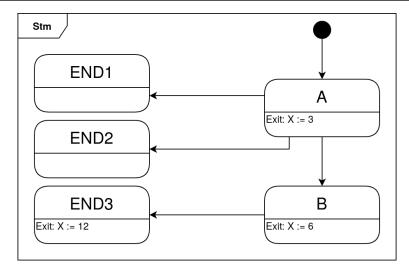

| <ul> <li>6.7</li> <li>6.8</li> <li>6.9</li> <li>6.10</li> <li>6.11</li> <li>6.12</li> <li>6.13</li> <li>6.14</li> <li>6.15</li> <li>72</li> </ul> | Test model for handling events at the same level       6         Test model for handling events in separate regions at different levels       6         Test model for after events in a simple scenario       6         Test model for after events with a composite state       6         Test model for entry behaviour       6         Test model for exit behaviour       6         Test model for exit behaviour       6         Test model for exit behaviour       6         Test model for composite state behaviour, entry behaviour, and transition effects 6         Test model for composite state behaviour with two regions       7         Test model for composite state behaviour with one region including nested region | 5<br>6<br>7<br>8<br>9<br>0 |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 6.16                                                                                                                                              | Test model for junction vertices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3                          |

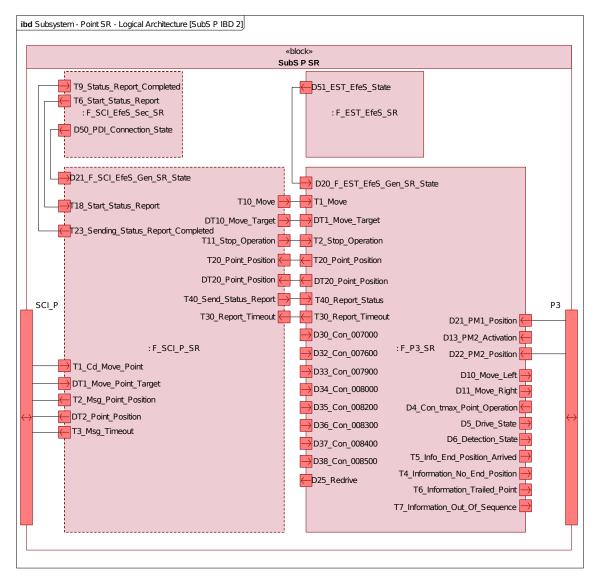

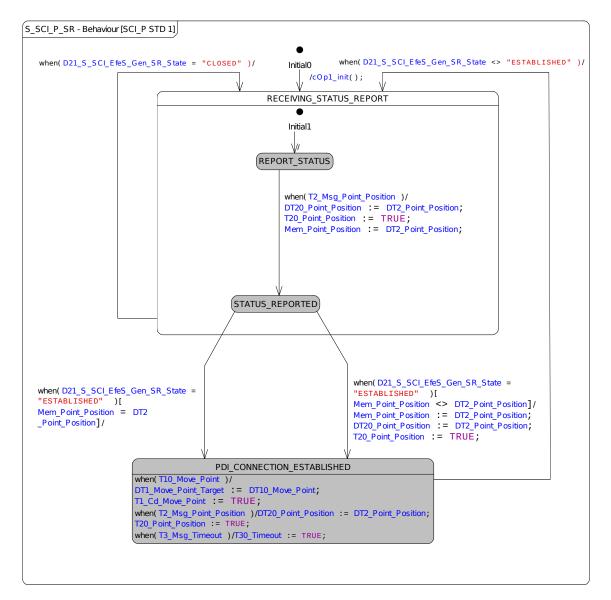

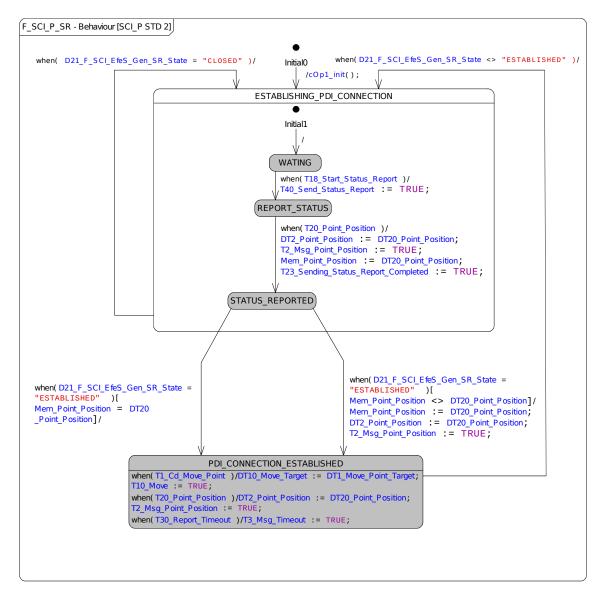

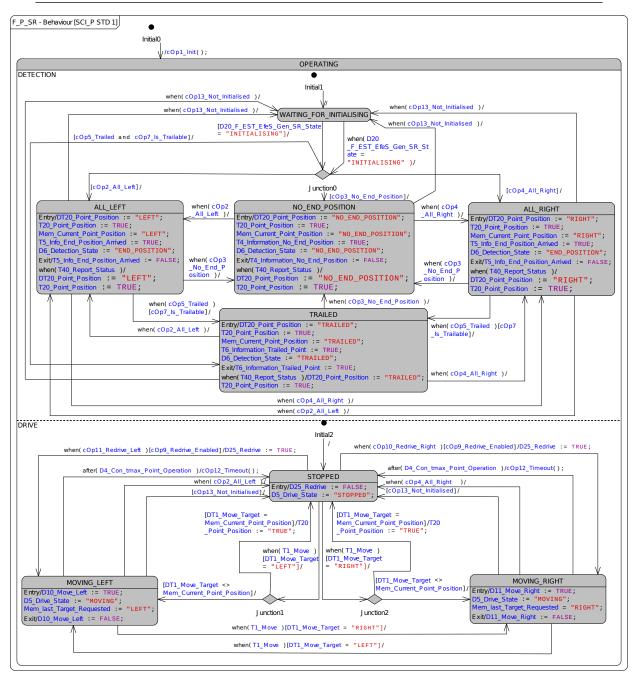

| 7.1<br>7.2<br>7.3<br>7.4                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |

| 10.1<br>10.2<br>10.3<br>10.4                                                                                                                      | Removal of a committed location with multiple incoming edges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16<br>17<br>18<br>19       |

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6                                                                                                      | State machine diagram of the FP component (Eu.P.4693) in Point [28] 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8<br>9<br>0<br>1           |

| 12.7                                                                                                                                              | Example simulation trace of SP in UPPAAL 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2                          |

\_\_\_\_\_

## 1. Introduction

When technological systems in for example the field of computer science or electrical engineering grow large it can become difficult to ensure that the behaviour of the system is correct. Especially if the system is not yet created and all that is available is documentation and design of the system. You can write many tests and try out every test case you can think of, but it is difficult to know for sure that a certain requirement of the system always holds. This is where model checking can help out.

In model checking you take an existing system and recreate its behaviour in a formal model. These models can have different forms. In this research we focus on automata. These are directed graphs where the vertices represent different states of the system and the edges represent transitions between these states which can be seen as actions. Due to the formal nature of the models, they can be simulated. Additionally, model checking tools provide property checking languages in which it is possible to write specific requirements that describe behaviour of the system. The model checking tool can then take that requirement and formally prove that the requirement is satisfied or give a counter example which proves that the requirement is not satisfied.

Examples of model checking tools are mCRL2 [12] and UPPAAL [19]. Both tools have their own way of specifying their models, but both modelling languages describe automata. While mCRL2 specifies models using process algebra in a textual form, UPPAAL has a graphical model editor in which you can create vertices and connect them via edges. To give an example application, mCRL2 and UPPAAL were used to help verify a pacemaker developed by Vitatron. This was done in the research of Wiggelinkhuizen et al. [32]. A pacemaker is a device that helps people who have a heart rate disorder called arrhythmia. It is surgically connected to the heart so it can send stimuli via pulses to help maintain an adequate heart rate. Because a pacemaker has to adapt to all possible heart rates and different cases of arrhythmia, the firmware consists of a complex combination of collaborating processes. Due to the fact that the device influences a vital organ of a

persons body it is crucial that its behaviour is correct. Therefore, it is incredibly useful if the behaviour of the pacemaker can be formally proven correct.

Another example of systems where the correct functioning of those systems is crucial for the safety of people are systems in railway engineering. In these include systems such as railway junctions and level crossings. The Dutch railway company ProRail and Germany's DB Netze are working together with the University of Twente and the Eindhoven University of Technology on the verification of an upcoming standard for railway signalling equipment interfaces [23]. This project is called FormaSig [11]. The standard is developed by the EU-level organisation EULYNX [9] that consists of the collaboration between 13 Infrastructure Managers. They created a dialect of SysML which we call EULYNX in the rest of the paper. This semi formal modelling language is used to specify the standard. To help with verifying these models the contributors of FormaSig proposed to create a translation [3] to the formal model checking tool mCRL2.

While the translation from EULYNX to mCRL2 is still currently in development, the developers found that the simulation trace explorer of mCRL2 is difficult to work with when applied to the models of EULYNX. It is mainly hard to trace back model elements to their corresponding EULYNX components when looking at the state history of a counter example to a requirement.

UPPAAL, on the other hand, provides a graphical simulation trace explorer, which gives a clear overview of the state of the model at every point in the history of the trace. Therefore, we found that an additional translation to UPPAAL could be useful. Additionally, the accessible property checking language of UPPAAL is beneficial for the project, so possibly railway engineers can specify and verify their own requirements in the future. Next to that we can potentially use the time system in UPPAAL for implementing the timed elements of EULYNX. These elements are not yet specifically implemented in the translation to mCRL2. Finally, an additional translation can also help verify the correctness of the other translation. However, this is not included in the scope of this project.

In this paper we create and evaluate a translation to facilitate the use of UPPAAL in the verification of models part of the EULYNX standard. First, we introduce EULYNX, UPPAAL, and mCRL2 to provide some background information. Here we also make a comparison between UPPAAL and mCRL2 to see what UPPAAL can provide that mCRL2 does not offer. Next in this research we determine which interpretation of SysML and EULYNX we should adhere to. Here we look at what fits best with respect to the goals for the translation, the interpretation used in the mCRL2 translation, and UPPAAL as target modelling language. Next, we create the translation, while taking inspiration from existing work on similar translations to UPPAAL. After that, we evaluate the translation in terms of correctness, usability, and performance. The correctness of the translation is tested by validating the behaviour of small test EULYNX models using UPPAAL requirements. These small models each cover a small feature of the EULYNX framework, and together they cover EULYNX as a whole. We test the usability of the output models by applying it to an existing EULYNX specification. Here we aim to check a variety of different requirements to determine what is possible to validate using the output models of the translation in UPPAAL. We do not intend to fully prove that the EULYNX model under test is correct. Lastly, we evaluate the performance of the output models in UPPAAL, and propose some ways in which the translation can be improved.

We found that an interpretation of SysML using cycles to synchronise the whole model is

the best option for our translation, as it enables the centralisation of the orchestration of the processes. This allows us to manage the processes that model the state machines with additional manager processes, which keeps the main processes more clear and readable as they do not contain a lot of synchronisation logic. The decision to use direct memory sharing for the communication between state machines followed from this, because the publication of port values to other state machines is part of the cycle. This can be implemented in UPPAAL by copying values from source variables to target variables, hence the direct memory sharing.

Next we created our own translation, using the existing input DSL of the mCRL2 translation as a base for the translation. We could also reuse some preprocessing steps that they created to eliminate for example overlapping internal block diagram definitions. We took inspiration from existing translations of UML and SysML state machines to UPPAAL, but we could not completely use existing work as the features of EULYNX differ from those of SysML and the interpretations of SysML state machines themselves are not the same everywhere.

In the validation of the translation we found it to be correct with the exception of a few elements that have been implemented in a simplified way that enables the translation to still be useful. While this is not a formal proof we are still confident in the correctness of the translation, but a formal proof is a useful addition that could be looked into in future work.

In terms of performance we found that it is not yet possible to check complete models that are part of the upcoming standards developed by EULYNX, because of performance issues. However, we are able to check some requirements on isolated components of these models. The expressiveness that the UPPAAL requirement language gives in combination with the output models of the translation is found to be sufficient for the verification of basic requirements on the models of EULYNX. To improve the performance and therefore increase the usefulness of the translation we propose three enhancements that can be implemented in future work. These improvements focus on how the state space of the output model can be reduced such that UPPAAL is better able to verify the requirements of the model.

All in all the translation proved to be useful from our usability study, and it was found to be correct with confidence. However, there is still room for improvement in the performance of the output model. Additionally, a formal correctness proof can help with validating the translation with stronger confidence.

## 2. Research questions

In order to gain additional insights in the models of EULYNX next to those that mCRL2 presents, we will also use UPPAAL to verify these models. To be able to do that reliably and frequently, we need to create an automatic translation tool which translates models from the EULYNX standard to the modelling language used by UPPAAL. From this goal we derive the following main research question:

How can we create a *jEULYNX* to UPPAAL translation which can be used on models of railway signalling equipment interfaces?

To help evaluate the outcome of the main research question we try to answer the following sub questions:

a) Which interpretations of EULYNX fit the goals of the translation to UPPAAL best, with regard to the usability, model complexity, and time constraints?

Next, we create the translation, after which we try to answer the following questions.

- b) Is the translation to UPPAAL correct?

- c) How well can the output models be used to verify model requirements?

- d) How well can the input models of the translation scale in size and complexity such that UPPAAL is still able to check them?

### 2.1 Clarification

With these extra questions we guide the research further by understanding how we can create a suitable translation for UPPAAL, and evaluating the quality of the translation.

## a) Which interpretations of EULYNX fit the goals of the translation to UPPAAL best, with regard to the usability, model complexity, and time constraints?

Here we look at different interpretations of EULYNX and the functionalities of UPPAAL. Translations of other UML state machine dialects to UPPAAL will also be evaluated for this purpose. We compare the benefits and possible drawbacks of the different interpretations, along with how it can be implemented in UPPAAL. Because the model simplicity is an important factor, we also look at how the different interpretations could effect the complexity of the output model. This is important because it makes the models and therefore the simulation traces easier to read. In short, the criteria for a good interpretation are that the intended model behaviour is achieved, and that the output models are easy to read. These points are discussed in the first part of Chapter 5.

#### b) Is the translation to UPPAAL correct?

The correctness of the translation is important, because the purpose of the translation is to test the behaviour of models. If the behaviour of a model is incorrectly translated, the translation loses its credibility. A formal proof would give a more complete indication of correctness, but this was too large of a task to also do in this project. Therefore we try to achieve some level of certainty by testing the different components in many scenarios. These test cases are developed after evaluating existing SysML specifications. Each scenario covers different edge cases of a specific EULYNX element in a model. This model is then verified with a number of properties that check for the correct behaviour or in some cases exclude incorrect behaviour. The application and results of this process can be found in in Chapter 6.

# c) How well can the UPPAAL requirement language be used in combination with the output models to verify model requirements?

With question c) we want to evaluate the usability of the output models by composing a list of different types of model requirements and checking if we can verify them using UPPAAL. With this this we want to test to what extent it satisfies the needs of railway engineers. This is important to know because it indicates if it can be used in practise. As case study we use components of the Point model [28], because it provides a realistic scenario for us to test on. We determine which properties and types of properties we want to check, and if and how they can be specified in UPPAAL. This process is discussed in Chapter 7.

# d) How well can the input models of the translation scale in size and complexity such that UPPAAL is still able to check them?

In answering question d) we want to find out how fast the state space of the output model expands beyond UPPAAL's exploring capabilities. This can be done by increasingly taking more components of a large example model like the Point model [28]. To get a more fine grained result we can create simple example models that can easily be expanded to create a larger state space. Producer consumer models could be used for this purpose. As a measure for how difficult the model is to check, we take the execution time for checking a certain property. This question is partly discussed in Chapter 7 and Section 10.1.

### 3. Related work

There exist some papers already out there that propose a translation from certain types of UML state machines to the model checking tool UPPAAL. Huang et al. propose an MDE-based translation algorithm that generates an UPPAAL model from a MARTE model [15]. MARTE models are SysML models with a few extensions like time and probability. In the paper they apply their translation to a Railway-Control System as a case study. In their approach they first createded a meta-model for MARTE state machine diagrams and created a meta-model for UPPAAL models. These meta-models can be seen as the input and output types of the translation. This general approach could also be useful in the creation of our translation. An important difference between MARTE models and EULYNX models is that the state machines in MARTE communicate via global variables and use events only in the form of named triggers, while in EULYNX they communicate via port connections and events can also be triggered from expressions evaluating to true.

Muniz et al. created the tool TANGRAM (Tool for Analysis of Diagrams) which can translate UML diagrams to UPPAAL models [26]. The main design of the tool revolves around the CORBA Component Model. This model adds extra functionality to UML that takes care of managing components during their execution time. The tool is demonstrated on a small case study used in train control systems. While they also do not use boolean expression based events, their centralised event system in the UPPAAL model can be partially applied in our translation. Instead of boolean expression based events, they have events that are defined solely with a label. These events can be seen as external events triggered by the environment of the model, and are handled as such.

In the research of Knapp and Merz [18], they create a tool called HUGO which mainly generates code from UML state machines. As an extra functionality it can also export to UPPAAL. In this export feature it flattens the whole model into a single process. This was done because their focus is on maximising performance rather than model readability.

There are also some papers which cover other facets of UML. For example in the research of Cui et al. [7] they propose a translation from UML timing diagrams to UPPAAL, and

apply it to a small coffee machine example.

The paper 'Verifying Liveness in Supervised Systems Using UPPAAL and mCRL2' [24] by Markovski and Reniers uses the tool Supremica to translate their source model to both UPPAAL and mCRL2. The source models are not close to UML. The model that they use models a supervisory controller. With the generated models they compare the two tools, and give a translation of requirements written in the specification language of UPPAAL to the one of mCRL2. They find that UPPAAL fits better as target for their translation than mCRL2. The reason for this is the way UPPAAL deals with state information opposed to mCRL2. In UPPAAL you can easily access state variables in both the modelling language and the property checking language. In mCRL2 you have to put the state information on events in order to be able to work with it.

UPPAAL has been applied to many case studies. We list a few of the case studies mentioned in the source paper of UPPAAL by Larsen et al as examples. [19]. Many of these case studies take a look at some form of protocols, since these can contain time critical elements.

The Audio/Video Protocol developed by Bang and Olufsen has been studied using UPPAAL. This protocol is used to allow multiple audio/video devices to communicate with each other over a single bus by sending messages. In this case [14] they found an error in the protocol, and proposed a solution to fix this problem.

A Collision Avoidance Protocol implemented on an Ethernet like framework was also studied using UPPAAL [16]. The protocol aims to prevent collisions of messages while minimising the delay of the messages. Using UPPAAL they were able to prove that the protocol completely prevents collisions and that the minimum message delay has been reached.

Another case study is the Gear-Box Controller made by the company Mecel AB for modern cars [22]. It waits for signals given by the surrounding system that request a gear change. The controller then makes the gear change. UPPAAL was used to prove 46 properties that were derived from the design requirements of the system. All properties were satisfied.

As relevant previous work part of this project we consider the two published papers regarding the verification of models from the EULYNX standard in mCRL2. The first paper by Luttik [23] discusses a proof of concept of the translation to mCRL2 in the form of a case study on the Point [28] model of the EULYNX standard. The model is translated manually, and the usability is evaluated by deriving nine safety requirements and verifying them in with mCRL2.

Continuing this research, Bouwman et al. propose an automatic translation to mCRL2 in a following paper [3]. They find that mCRL2 provides the right functionality to model the behaviour of SysML state machines in an elegant way. Which means that they could model the behaviour of SysML state machines without a lot of extra boiler plate model code.

# 4. Background

In this chapter we introduce and provide a basic understanding of the relevant tools and specifications of this research. First we discuss the features and semantics of the modelling language used in the EULYNX standard. Then, we describe the tools UPPAAL and mCRL2. After that we evaluate the differences between the two tools, and establish the points where they complement each other. Lastly, we look at how we could translate

### 4.1 EULYNX

EULYNX [9] is a modelling language made for designing and specifying systems in railway engineering. Development of this standard started in 2014, initialised by railway infrastructure managers of 6 European countries. It is a visual standard to create graphical models. These models contain for example use-case diagrams, sequence diagrams, object relationship diagrams, and state machine diagrams. Because EULYNX is used to design and specify systems in a graphical way, it is not possible to formally verify them with existing tools. Therefore we want to translate these models to models that can be read and verified by formal model checking tools.

The parts of EULYNX that are relevant to this project are the state machines, and how they can be combined to form complex multi process systems. The state machines are built with basic components like vertices and transitions between those vertices. These are extended with features such as guards and effects. To help describe the modelling features of EULYNX we take a look at an example. This same example will also be used in the description of the other modelling tools. The example models 4 Vikings that are on one side of a bridge. The goal is to all get on the other side of the bridge, but they can only cross the bridge while holding a torch. There is only one torch available and it can be held by a maximum of two vikings. Lastly, every viking has its own maximum speed at

Figure 4.1: EULYNX Viking IBD

which they can cross the bridge.

We first take a look at the general definition of the Viking diagram. It is shown in Figure 4.1. The Viking diagram has three variables of which the torch\_time is an input variable, and the other two are output variables. This represents the data flow between the different state machines. The torch\_time is the amount of time the viking is allowed to hold the torch for at the moment. The location variable lets other block diagrams know on which side of the bridge the viking is at the moment, and the request\_torch variable makes sure other processes know if the viking wants the torch or not.

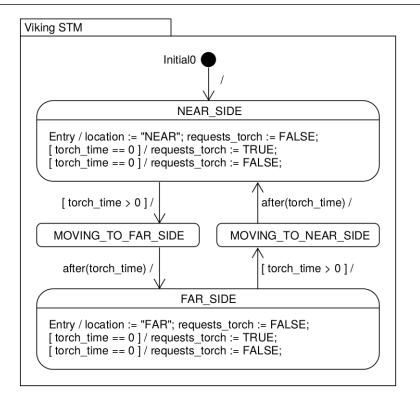

Now for the internal logic of the viking, we look at the state machine specification. This is shown in Figure 4.2. The viking starts in the NEAR\_SIDE state. The first line of the contents of this state represents the code that is executed on entry of the state. This sets its output variables to their initial values. On the next two lines the internal behaviour of the state is described. When the torch\_time equals zero, it makes a non-deterministic choice between setting the request\_torch variable to true or false. The transition between the NEAR\_SIDE state and the MOVING\_TO\_FAR\_SIDE state has a guard that checks if the torch time is more than zero. When this is the case it can take that transition. The next transition contains a timeout event. It first needs to wait for the amount of time it takes to cross the bridge, as specified with after(torch\_time). The same but the other way around happens to get from the FAR\_SIDE state to the NEAR\_SIDE state.

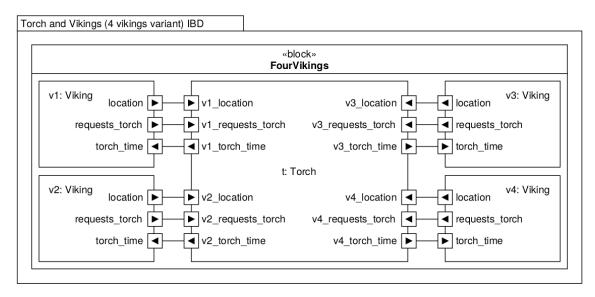

The block diagram definition of the torch state machine is shown in Figure 4.3. It has as properties the torch\_location, torch\_time, and requestCount. The property torch\_location keeps track of on which side of the bridge the torch is.torch\_time is zero if no viking is holding the torch or the maximum speed of the vikings that are currently holding the torch. Lastly, requestCount keeps track of how many vikings currently want the torch. The internal helper functions the Torch uses in its state machine are listed below the properties. The definition for these can be found in Appendix A. The input and output variables are listed below the list of internal operations. For each viking the torch IBD has as input variable the location of the viking and if they request the torch or not. As output variables it has for each viking the amount of time for which they are allowed to hold the torch.

The composition of all the IBDs are shown in Figure 4.4. This shows the dependencies between the different processes, and the general flow of data.

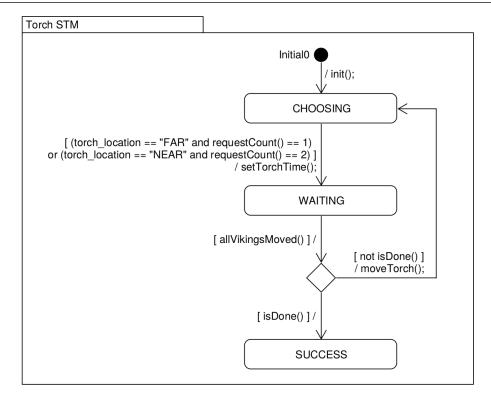

The full state machine of the torch process is shown in Figure 4.5. The transition between

Figure 4.2: Viking state machine in EULYNX

CHOOSING and WAITING has both a guard, and an effect. The guard checks for how many vikings on the same side as the torch currently request the torch. The needed amount if the torch is on the near side is two, and one for the other side. It is limited to these amounts, because traveling with only one person from the near side to the far side does not help with solving the problem of getting all the vikings to the other side. The same holds for traveling with two vikings from the far side to the near side. When the guard evaluates to true, it can take the transition, and the effect will set the torch time output variables for each viking that is currently allowed to have the torch. After that it waits until all the vikings have moved. The diamond like state represents a choice vertex. When all the vikings are on the far side, it transitions to the SUCCESS state, and otherwise it goes back to the CHOOSING state and the whole process is repeated.

The programming language used in the guards, effects, and internal operations is the ASAL language [2]. ASAL stands for Atego Structured Action Language. It contains only basic statement types:

- Assignment

- Return

- Operation calls

- If statements

- Multi statements

The expression types contain two interesting types. The PulsedIn and PulsedOut types are equivalent to the boolean expression, but indicate a different physical signal type. In EULYNX they mean that once a value is published as a pulse, it can only be consumed/read once.

Figure 4.3: EULYNX Torch IBD

Figure 4.4: Vikings and Torch IBD composition in EULYNX

Figure 4.5: Vikings and Torch IBD composition in EULYNX

#### 4.2 UPPAAL

UPPAAL [19] is a model checker which allows the verification of complex systems. It supports non-deterministic timed state machines which can consist of multiple separate processes. These can communicate through variables and channels. In order to check properties of its models UPPAAL has its own specification language. The two main design criteria of the model checker are efficiency and ease of use. To achieve efficiency, UPPAAL implements several optimisation techniques. The detailed debug functionalities show their commitment to usability. All these points are discussed in further detail in the following sections.

#### 4.2.1 Input language

When creating a model manually, the graphical user interface of UPPAAL gives better at-a-glance information than the textual model representation. The models are shown as directed graphs, and you can edit the graphs directly.

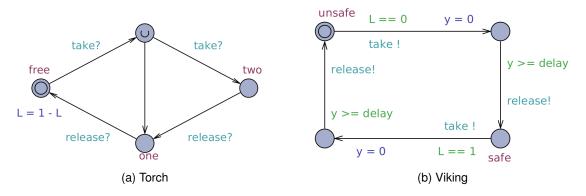

To demonstrate this we take a look at the same example used in Section 4.1. The code for this example was already present in the UPPAAL installation folder, and it is used in this section. In Figure 4.6 the two process templates of the system are shown. It models vikings that can only cross a bridge to the safe side while holding the torch. The torch can only be held by two vikings at the same time, and there are four instances of the viking process, each with its own delay (how long it takes to cross the bridge).

The processes communicate with each other through the channels take and release.

Figure 4.6: UPPAAL model view of the bridge example

These channels and the variable L are declared in the global scope. A light blue take! synchronisation label triggers an action with the light blue take? label. These edges can only be taken together. The green edge labels are guards, so that edge can only be taken if the guard evaluates to true. The dark blue labels are assign statements that are executed when the edge is taken.

The location of the torch is tracked with the global variable L, so that in the viking model a guard can ascertain if a viking is in the same place as the torch, and only take the torch if that is the case. The value of L is changed once the torch is released by the last viking holding the torch. So if a viking wants to travel to the other side and back again, they have to take the torch, release it, and then take it again. This is also visible in the way the process of the viking loops.

To model the different speeds at which the vikings cross the bridge a clock is used. The variable y is a clock which is declared (not visible in Figure 4.6) in the scope of a viking. Once a viking takes the torch, the clock is set to zero. The viking can then only release the torch after the clock reaches a value greater or equal than the delay property of the viking.

#### 4.2.2 Input files

UPPAAL supports three file formats [8] as input:

- XML

- XTA

- TA

Models created using the graphical user interface of UPPAAL are stored in the XML format. This format supports all the features of UPPAAL 4.0, including the graphical positioning of model elements. The XTA file format is a more readable format if you want to model in a textual way. This format does not include the graphical positioning of model elements, but they can be added with a UGI [10] file. The TA format is the older version of the XTA format. It does not support some newer features like process templates.

As an example we show the bridge example in XTA file format [31] in Listing 4.1.

Listing 4.1: Bridge example in 'XTA' file format.

```

1 chan take, release;

2 int [0,1] L;

3

4 process Viking(const int delay) {

5 clock y;

6 state SO, safe, S1, unsafe;

7 init unsafe;

8

trans

S0 -> safe {

9

guard y >= delay;

10

sync release!;

11

},

12

13

safe -> S1 {

14

guard L == 1;

15

sync take!;

16

assign y = 0;

17

},

S1 -> unsafe {

18

guard y >= delay;

19

sync release!;

20

},

21

unsafe -> SO {

22

guard L == 0;

23

sync take!;

24

assign y = 0;

25

26

};

27 }

28

29 process Torch() {

30 state one, SO, free, two;

31 urgent S0;

32

init free;

33

trans

free -> S0 {

34

35

sync take?;

36

},

37

S0 -> one { },

S0 -> two {

38

39

sync take?;

},

40

one -> free {

41

sync release?;

42

assign L = 1 - L;

43

},

44

two -> one {

45

sync release?;

46

47

};

48 }

49

50 const int fastest = 5;

51 const int fast = 10;

52 const int slow = 20;

53 const int slowest = 25;

54

55 Viking1 = Viking(fastest);

56 Viking2 = Viking(fast);

57 Viking3 = Viking(slow);

58 Viking4 = Viking(slowest);

59

60 system Viking1, Viking2, Viking3, Viking4, Torch;

```

The XML file format has the same structure as the XTA format. All the model elements are declared in scopes denoted by curly brackets. This means that a variable declared in a certain scope can be accessed by elements that are descendants of this scope, while elements in parent scopes cannot access these variables. For example the channels take and release, the location variable L, the delay constants, and the model composition are declared in the global scope. Inside the process declarations it is possible to declare process independent variables like in this case the clock variable y. Next to that the states are listed, the init state is defined, and the transitions are specified. The transition labels are declared within the scope of the transitions.

When editing an XTA file in the graphical user interface of UPPAAL it automatically creates a '.ugi' file. An example file is shown in Listing 4.2. It uses the same names as in the XTA file and provides x and y coordinates for each element.

| Listing 4.2:  | Example | 'HGI' | file for the | - bridae | XTA file |

|---------------|---------|-------|--------------|----------|----------|

| Listing + .2. |         | oui   |              | 5 Driuge |          |

```

1

2 process Viking graphinfo {

3

location S0 (195,76);

4

locationName S0(-10,-30);

location safe (-17,76);

5

6

locationName safe(-10,-30);

location S1 (-17,229);

7

locationName S1(-10,-30);

8

location unsafe (195,229);

9

10 locationName unsafe(-10,-30);

11 guard S0 safe 1 (-30,-42);

12 sync S0 safe 1 (-30,-27);

13 guard safe S1 1 (9,-31);

14 sync safe S1 1 (9,-16);

15 assign safe S1 1 (9,-1);

16 guard S1 unsafe 1 (-30,0);

17 sync S1 unsafe 1 (-30,15);

18 guard unsafe S0 1 (9,-31);

19 sync unsafe S0 1 (9,-16);

assign unsafe S0 1 (9,-1);

20

21 }

22

23 process Torch graphinfo {

24 location one (76,195);

locationName one(-8,9);

25

location S0 (76,51);

26

locationName S0(-10,-30);

27

location free (-51,127);

28

locationName free(-10,-30);

29

30 location two (212,127);

31 locationName two(-10,-30);

32 sync free S0 1 (-29,-30);

33 sync S0 two 1 (-8,-30);

34 sync one free 1 (-46,0);

35 assign one free 1 (-42,19);

sync two one 1 (-17,0);

36

37 }

```

Because requirement specification is also not supported in the XTA file format, UPPAAL saves the queries to a '.q' file. An example of this is shown in Listing 4.3.

Listing 4.3: Example query file for the bridge XTA file.

```

1 //This file was generated from (Academic) UPPAAL 4.1.24 (rev. 29

A3ECA4E5FB0808), November 2019

2

3 /*

4 The system does not contain deadlocks.

5 */

6 A[] not deadlock

7

8 /*

9 There exists a path which results in all vikings being on the safe side

10 */

11 E<> Viking1.safe and Viking2.safe and Viking3.safe and Viking4.safe

```

#### 4.2.3 Requirement language

To be able to formally express properties of models created in UPPAAL, it provides a custom property checking language. The language is similar to the commonly used CTL language, but it does not support nested path formulas, which limits the expressiveness. This does make the language easier to understand. The path formulas it does support are:

• Possibly: E<> p

Evaluates to true if there exists a path where in some state p holds.

CTL formula: EF p

• Invariantly: A[] p

Evaluates to true if p holds for all reachable states.

CTL formula: AG p

• Potentially always: E[] p

Evaluates to true if there exists a path which results in an infinite loop of in which p always holds.

CTL formula: EG p

• Eventually: A<> p

Evaluates to true if all possible paths eventually reach a state in which p holds.

CTL formula: AF p

• Leads to: p -> q

Evaluates to true if for every state in which p holds all paths starting from that state eventually reach a state in which q holds.

CTL formula: AG p => AF q

Next to that, UPPAAL also offers some syntax for querying statistical properties of the model. This includes constructs that give the probability of a certain state expression evaluating to true, compare probabilities to a specified bound, the comparison of two probabilities, and value estimation.

Both the path formulas and the statistical formulas make use of state expressions. With these it is possible to query anything in the state. They are basic formulas, also called predicates, that cannot have side effects. This could be the value of a clock, a global variable, or even properties defined in the scopes of locations. Common operators like +, ==, and && can be used here. In addition to that, UPPAAL provides some helper functions like forall, exists, sum, and deadlock. Especially deadlock is a very strong expression which can be used only in the requirement language. It specifies a state in which all processes do not have any transitions they can take, and therefore are stuck in the current location. The other helper functions can also be used in the programming language of UPPAAL, so they can appear in the guard and update labels.

As an example we can specify a requirement for the viking example. If we wanted to know if there exists a path where all the vikings end up on the safe side of the bridge we would write the following:

'E<> Viking1.safe and Viking2.safe and Viking3.safe and Viking4.safe'

The E <> bit is the 'Potentially' operator, and it evaluates to true if the formula after it holds in a state in at least one of the possible paths. With Viking1.safe we specify that 'Viking1' is in the safe state.

#### 4.2.4 Diagnostics

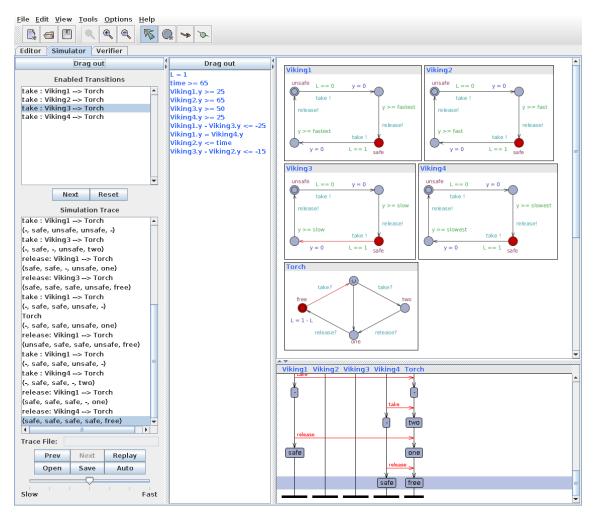

To demonstrate the diagnostics of UPPAAL, we tell it to check the requirement described above. As additional option we specify that UPPAAL should look for the shortest trace, satisfying this requirement. The resulting trace is shown partly in Figure 4.7 as it is too big to fit entirely in one screen.

In the top right window we see the model instances of the system and in which location each process is at the moment. To the left of that all the local and global variables are shown. And in the top left corner we see which transitions can be taken at this point, and they can even be selected and taken. Below that window in the bottom left corner, we see the simulation trace. A graphical representation of the trace is shown in the bottom right window.

#### 4.2.5 Verification algorithm

In its core the verification algorithm of UPPAAL is a reachability algorithm, which looks for states in which the given constraints evaluate to true. At the same time, the algorithm tracks how such states can be reached. In their implementation they make use of symbolic states. This pairs states with the given requirements which hold in that state. UPPAAL gains much performance by preprocessing the model using the following techniques.

Most of the computation time is spent doing checks on the symbolic states and comparing them with each other. Because of this, the overall performance can be greatly improved by optimising these operations. Data structures which support such operations in an efficient way are Difference Bounded Matrices. They were implemented with some alterations [20], which resulted in a big performance boost.

Figure 4.7: Trace view of the vikings example.

Next to that, UPPAAL does some static analysis on the symbolic states to check if some are redundant and therefore can be removed. This reduction of the symbolic state space will also make the algorithm more efficient.

On a final note, UPPAAL caches the generated symbolic state space so it can be reused to check other properties, if more than one requirement has been given to evaluate.

### 4.3 mCRL2

To determine the benefit of an additional translation to UPPAAL next to the one of mCRL2 we also take a closer look at the tool mCRL2 [13] and see where the two tools complement each other. This section therefore contains a short description [12] of the tool. It is a newer version of the tool  $\mu$ CRL, which was designed to be minimal. With mCRL2 it is possible to analyse abstract models of concurrent processes that can communicate with each other. It utilizes process algebra to describe its input models. These models can be tested with properties specified in the language of the modal mu-calculus.

#### 4.3.1 Input language

The input models of mCRL2 are specified in a textual way. The definition of the system is split up into separate sections of the file, where each section starts with a specific keyword. In its simplest form the model definition contains three sections:

- The definition of all the actions possible by the system. This section is prefixed by the keyword act.

- The definition of the processes of the system. This section is prefixed by the keyword proc.

- The definition of the initial state or the initialization of the system. This section is prefixed by the keyword init.

The actions section contains a simple list of all the action labels of the system. In the process section, the processes are described using process algebra. A simple simple example would be x = a. b. X. This process would accept an a action, then a b action, and then it would repeat itself again recursively.

An extra feature mCRL2 supports is that the action labels and process declarations can take parameters, for which constraints can be written to express more complicated systems.

To further get an understanding of the modelling language, we take a look at how the viking example, discussed in Section 4.1, can be modelled in mCRL2. This model is used as an example in the online tutorial for the tool [30]. The model is shown in listing Listing 4.4.

Listing 4.4: Vikings example in mCRL2.

```

1 % Specification for the rope bridge problem

2 % Written by Bas Ploeger, June 2008.

3

4 sort Position = struct start | finish;

5

```

```

6 act forward_viking,

7

forward_torch,

8

forward_referee,

forward: Int # Int;

9

10

back_viking,

11

back_torch,

12

13

back_referee,

back: Int;

14

15

16

report: Int;

17

18 % Models the torch which can move to the other side of the bridge

19 proc Torch(pos:Position) =

20

(pos == start) ->

21

sum s,s':Int . forward_torch(s,s') . Torch(finish)

22

<>

sum s:Int . back_torch(s) . Torch(start);

23

24

25

26 % Models an viking who can move to the other side of the bridge with

27 % its designated speed

28 proc Viking(speed:Int, pos:Position) =

(pos == start) ->

29

30

( sum s:Int .

(s > speed) -> forward_viking(speed,s) . Viking(speed,finish)

31

<> forward_viking(s, speed) . Viking(speed, finish)

32

33

)

34

<>

35

back_viking(speed) . Viking(speed, start);

36

37

38 % Models the referee who counts the number of minutes passed and the

39 % number of vikings that have reached the far side of the bridge

40 proc Referee(minutes:Int, num_finished:Int) =

sum s,s':Int . forward_referee(s,s')

41

. Referee(minutes + max(s,s'), num_finished + 2)

42

43

+

44

(num_finished < 4) \rightarrow

sum s:Int . back_referee(s)

45

. Referee(minutes + s, num_finished - 1)

46

47

<>

report(minutes) . Referee(minutes, num_finished);

48

49

50

51 init allow( { forward, back, report },

52 comm( { forward_viking | forward_viking |

forward_torch | forward_referee -> forward,

53

54

back_viking | back_torch | back_referee -> back },

55

Viking(1, start) || Viking(2, start) ||

Viking(5,start) || Viking(10,start) ||

56

Torch(start) || Referee(0,0)

57

58 ));

```

On line 4 the datatype Position is defined. It can be seen as some kind of enumeration, which can have the value start or finish. These resemble the two positions the vikings and the torch can have, relative to the bridge. Next, the possible actions are defined. Each entity has a forward and backward action with the same parameter types. Both parameters contain the time an viking who is holding the torch needs in order to cross the bridge. The

first one is always the one that takes the longest time. This is achieved with a constraint written in the Viking process. The backward motions however only have one argument, as it does not benefit the vikings to travel back with two people.

The definition of the Torch process on line 19 is very straightforward. It can do a forward motion or a backward motion depending on its current location.

The Viking process is a little more complicated. It takes two arguments, its speed (minutes it takes to cross the bridge), and its current position. Depending on its position it can do a forward motion. On line 31 it checks if its speed is greater than s, which is a free variable that represents the speed of the other viking crossing the bridge together with this viking.

Lastly the Referee process is defined to keep track of the time that has passed, and to see if all the vikings have crossed the bridge. It takes as arguments the number of minutes that have passed, and the total number of vikings on the right side of the bridge. It can record a forward and backward motion of the torch, and if all the vikings are on the right side of the bridge it will take the report action with as parameter the number of minutes that have passed. On line 46 it is visible how the referee keeps track of the time and the number of vikings on the right side by recursively calling itself and incrementing its parameters.

On line 51 it starts the definition of the system composition by stating that only the actions forward, back, and report are allowed. The forward and back actions are defined in the first part of the comm block. It specifies that for example the forward action consists of two forward\_viking actions, a forward\_torch action, and a forward\_referee action occurring simultaneously. In the second part of the comm it specifies that the system consists of four viking processes, a torch process, and a referee process running in parallel. Within the definition the initial parameters of the individual processes are also given.

### 4.3.2 Requirement language

As requirement language, mCRL2 supports the modal mu-calculus [4] with their own syntax [25]. It is split up into State formulas, Regular formulas, and Action formulas.

With the action formulas you can specify action labels used in a process of the model, or data expressions. Data expressions can access state variables and may contain common arithmetic operators. These formulas are extended with useful functions like forall and exists to help with specifying a state condition.

The regular formulas wrap around the action formulas to combine Action formulas or quantify them. It contains 4 operators:

- formula + formula specifies a choice between the two formulas.

- formula . formula specifies a concatenation of the two formulas.

- formula \* repeats the formula zero or more times.

- formula + repeats the formula one or more times.

The regular formulas are used inside the State formulas. The State formulas we are mainly interested in are the ones related to the modal mu-calculus:

• mu <code>StateVar</code> . <code>StateForm</code> maps to the mu-calculus formula:  $\mu X.\phi$

Figure 4.8: Model view of the vending machine example in mCRL2

- nu StateVar . StateForm maps to the mu-calculus formula:  $vX.\phi$

- [ RegForm ] StateForm maps to the mu-calculus formula:  $[a]\phi$

- < RegForm > StateForm maps to the mu-calculus formula:  $\langle a \rangle \phi$

StateVar contains a declaration of a state variable, StateForm is recursively a State formula again, and RegForm is a Regular formula containing Action formulas.

#### 4.3.3 Diagnostics

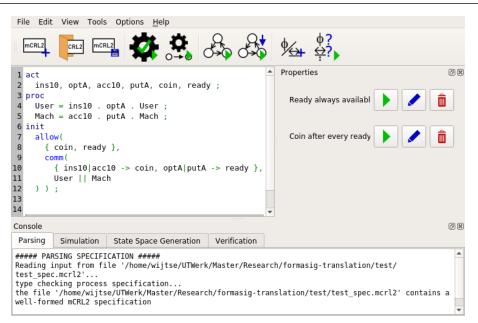

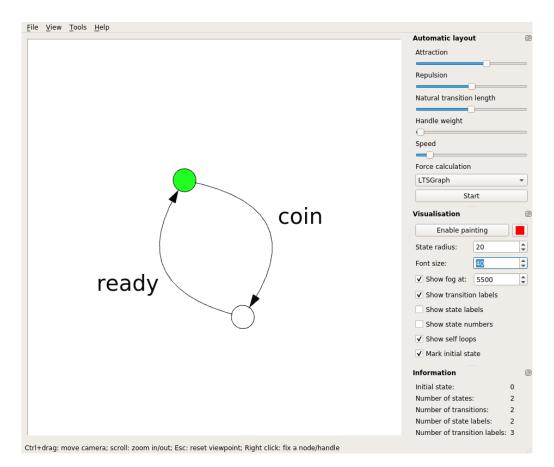

As a simple example we take the vending machine [1] from the mCRL2 website. The model description and the mCRL2 modeling interface are shown in Figure 4.8.

Here we can see the separate model sections act, proc, and init as described before. The User process can only do the action ins10 (which means insert 10 currency inside the vending machine), and after that an action optA (which means select the apple in the vending machine). Next, the user can repeat those actions in the same order. The vending machine's actions are 'accept 10 currency', and then put/give an apple. These actions can also be repeated infinitely in that order. In the innit section, the ins10|acc10 -> coin, optA|putA -> ready part means that the actions ins10 and acc10 synchronize and emit a coin action. The same for the optA and putA actions respectively. The User || Mach part specifies that the two processes User and Mach run in parallel.

In Figure 4.9 an example diagnostic trace is shown for the property [ true\* . ready . !coin ] false, which means that after every ready action a coin action takes place.

Figure 4.9: Diagnostic trace view of a requirement of the vending machine example.

| Aspect  | UPPAAL                                                                                                                                                                                                                          | mCRL2                                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| GUI     | <ul> <li>Graphical representation is possible.</li> <li>Easy at a glance information.</li> </ul>                                                                                                                                | <ul> <li>Only graphical snapshots<br/>can be generated of the<br/>model.</li> <li>The model cannot be edited<br/>in a graphical way.</li> </ul> |

| Textual | <ul> <li>The structure of the model uses scopes.</li> <li>Contains a C like language for update actions, guards, and invariants on locations and edges.</li> <li>Language describes the structure of state machines.</li> </ul> | <ul> <li>Data is scoped, but function-<br/>s/processes are not.</li> <li>Language uses process alge-<br/>bra to specify processes.</li> </ul>   |

Table 4.1: Moddeling in UPPAAL compared to mCRL2

### 4.4 UPPAAL compared to mCRL2

To further support the choice of using UPPAAL to verify EULYNX models in addition to mCRL2 we need to take a look at the advantages and disadvantages of UPPAAL compared to mCRL2. In the paper 'Verifying liveness in supervised systems using UPPAAL and mCRL2', Markovski and Reniers [24] compare the two tools by applying both to a case study. Their findings are used as well as my findings in the comparison below. The aspects of the two tools can each be separated into three, the modelling language, the requirement language, and the diagnostics.

#### 4.4.1 Modelling language

In UPPAAL you can create models in two ways, with a textual representation of the model, or through a graphical user interface. Here the models are created in an object oriented way. mCRL2 only supports textual representations of models. These models are described in a more formal way, focusing on the specifying the behaviour of a system and its processes.

#### 4.4.2 Requirement language

UPPAAL provides its own requirement language. The formulas that can be created with this language is a subset of CTL. mCRL2 contains a syntax with which it is possible to create modal mu calculus formulas that can be used for checking the model.

| Aspect            | UPPAAL                                                                                                                                                         | mCRL2                                                                                                   |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| Path expressions  | <ul> <li>Is a subset of CTL.</li> <li>Nested path expressions are<br/>not possible.</li> <li>Limited expressiveness.</li> <li>Easier to understand.</li> </ul> | <ul> <li>Supports the modal mu-<br/>calculus.</li> <li>Superior expressiveness.</li> </ul>              |

| State expressions | <ul> <li>State based expressions.</li> <li>Full access to all the variables of the state.</li> </ul>                                                           | <ul> <li>Action based expressions.</li> <li>Not possible to access state variables directly.</li> </ul> |

Table 4.2: Requirement specification in UPPAAL compared to mCRL2

| Aspect | UPPAAL                                                                                                                                                     | mCRL2                                                                                                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Traces | <ul> <li>Can give a trace as a counter example or a witness.</li> <li>Can walk through the trace.</li> <li>Shows the whole state at every step.</li> </ul> | <ul> <li>Gives traces only as counter examples, no witnesses.</li> <li>Can walk through the trace.</li> <li>State of individual components are difficult to untangle.</li> <li>Provides multiple tools to make traces easier to read.</li> </ul> |

Table 4.3: Diagnostics in UPPAAL compared to mCRL2

### 4.4.3 Diagnostics

Both tools have the ability to check the specified requirements in a graphical user interface, and give counterexamples when a property is not satisfied. The information UPPAAL gives, however, is a little more accessible.

# 5. Translation

In this chapter we discuss the structure and design of the EULYNX to UPPAAL translator. First we go into the EULYNX interpretations that are suitable for this research and core design decisions of the translator, followed by the general structure of the generated model. After that we zoom in on the different steps the translator takes and how the different components in EULYNX are translated. This is followed by a general overview of how the fundamental elements of EULYNX models are translated.

# 5.1 Possible EULYNX interpretations

Because the semantics of UML, SysML, and EULYNX are not exactly defined and some behaviour is ambiguous, there are multiple interpretations of the modelling language. Next to the goal of creating a translation that produces as similar behaviour as possible to the mCRL2 translation, we also look at which interpretations fit best with UPPAAL as target language. There are two main points where we have to decide which path we should take, because these lay the foundation of the semantics of parallel state machines. Other minor interpretation choices follow from these decisions. The first is how multiple state machines should interleave, and the second is how alterations in the memory are shared between the different state machines.

## 5.1.1 State machine interleavings

How the different parts of the model run together lays the foundation for how the rest of the model needs to be implemented. UPPAAL gives the different processes the possibility to do a step (take a transition) at any time, given that there are no time constraints or channel synchronisations. All these steps of the different processes are done sequentially. It is

possible that one process takes many steps, while the other stays in its current state, again given there are no time constraints or channel synchronisations. This is also a possible interpretation of EULYNX.

The other interpretation we consider for this subject is where the model runs on cycles [29], and that in each cycle all the state machines do one step. This prevents that in some traces one state machine is being blocked whiled the other is constantly activated. It also has the added benefit of a reduced state space, because there are less state machine interleavings possible. While the individual steps still occur sequentially, each state machine has done one step before the cycle repeats. This makes it also possible to implement in UPPAAL. To orchestrate the processes to take one step each cycle, a separate process is required that manages the cycles of the model and triggers the different processes to take a step.

## 5.1.2 Memory sharing

State machines in EULYNX are connected to each other via ports and flows. These can also be seen as properties where a change in value is reflected on the connected ports. The other state machine can then read the new value of this property. How these variable alterations are handled can be done in several different ways. The current translation to mCRL2 uses queues for this. Each alteration is put in a queue and handled separately by the receiving state machines. UPPAAL does not offer queues as a specific functionality, however they can be implemented using arrays and a bit of additional code for the different operations.

A different interpretation is the variant with direct memory sharing. In this variant the state machines operate on shared variables, so the change is visible to the other state machine immediately. Implementing this in UPPAAL is fairly straightforward as UPPAAL provides a global scope in which shared variables can be declared. Another variation of this interpretation is where there are two variables declared for every port connection, the input and the output side. With this it is possible to publish all changes at the same time, by creating an atomic operation that writes the values of all the source sides of the flows to the variables corresponding to the target sides of the flows.

## 5.1.3 Decisions