University of Twente EEMCS Computer Architecture and Embedded Systems

# On Productive, Low-Level Languages for Real-World FPGAs

**MSc Thesis** Pieter Staal (s1776894)

Monday 28<sup>th</sup> February, 2022

## **Supervisors**

ir. E. Molenkamp ir. H.H. Folmer dr. W. Kuijper dr. ir. C.P.R. Baaij

# Contents

| 1                | Introduction                                              | <b>2</b>  |

|------------------|-----------------------------------------------------------|-----------|

| <b>2</b>         | Computational Complexities in Modern FPGA Synthesis Flows | 3         |

| 3                | On Productive, Low-Level Languages for Real-World FPGAs   | 8         |

| 4                | Design Decisions                                          | 17        |

| 5                | Software Manual Introduction                              | <b>22</b> |

| 6                | Setting Up                                                | <b>24</b> |

| 7                | Programming In Ex-PART                                    | 27        |

| 8                | Example Programs                                          | 44        |

| 9                | Maintenance                                               | 55        |

| $\mathbf{A}_{]}$ | opendices                                                 | 67        |

| $\mathbf{A}$     | Case Studies Code                                         | 68        |

# Chapter 1

# Introduction

# 1.1 Introduction

In this master thesis we set out to design and develop a productive, low-level FPGA design language. A productive language offers designers abstractions such that complex designs can be defined efficiently and elegantly. Low-level languages offer major control over how exactly the program text is translated to the target architecture. Consequently, in a low-level language the target architecture is in a certain way visible to the designer. To anchor this research in reality, we additionally required the language to work for a real FPGA chip.

No current language for FPGAs fulfills these criteria. The design and implementation of such a language have shown what difficulties must still be overcome to realize a production-ready productive low-level language. However, it has also shown that modern tools enable the development of such languages while this used to be impossible.

# 1.2 Organization

This thesis starts with a survey of computational complexities in modern FPGA synthesis flows. This research was conducted as no such overview was readily available, while having a clear view of the processes involved in synthesis and their computational complexities does provide much insight into what a low-level language must be able to do.

Our main findings are then presented in the paper On Productive, Low-Level Languages for Real-World FPGAs. The design of our language Ex-PART (Explicit Place And Route Tool – a bit of a misnomer as the final version does not explicitly allow routing constraints) Several larger hardware designs built in Ex-PART are analyzed. The results of the designs defined in Ex-PART are discussed.

As an academic paper is not a good place to present all the design decisions taken during the development of Ex-PART, an extra design decisions document is included after the main paper.

Since Ex-PART is quite a large software package its design, implementation, and usage are explained in Ex-PART manual. This manual provides a thorough explanation of every source file in the program and of every feature a designer can use. It also contains warnings for partly implemented features and behavior that one may not expect. Furthermore, a guide to setting up Ex-PART is provided.

Chapter 2

# Computational Complexities in Modern FPGA Synthesis Flows

# Computational Complexities in Modern FPGA Synthesis Flows

Pieter Staal

University of Twente Enschede, the Netherlands p.j.staal@student.utwente.nl

*Abstract*—The modern FPGA synthesis flow from hardware description to bitstream requires solving four main problems either optimally or up to certain constraints: logic synthesis, packing, placement, and routing.

In the literature no comprehensive overview of the computational complexities of these problems is available. This paper provides such an overview. It was found that both logic synthesis and placement are NP-complete. Packing was shown to be the same problem as placement and routing in general, but polynomially solvable in special cases that occur in real FPGAs. Routing has been found to be NP-complete for a specific architecture. Optimizations in logic synthesis were surveyed: circuit minimization is  $\Sigma_2^P$ -complete, subcircuit substitution is NPcomplete, and finite state machine extraction and optimization are efficiently solvable.

New, larger FPGAs allow FPGA engineers to build larger designs. However, such a larger design implies that the size of the problems to be solved increases as well. The found complexities indicate that run-time of tools solving these problems will grow much faster than the size of the problem does. Therefore, it is concluded that this method of defining and synthesizing FPGA designs is not sustainable.

*Index Terms*—Complexity, Digital Hardware Design, Electronic Design Automation, NP-Complete, NP-Hard, Logic Synthesis, Place and Route

### I. INTRODUCTION

A modern solution to the stagnating performance of processors is parallelism. The reconfigurable fabric of logic on an FPGA is very suitable to solve problems in parallel. In theory, this parallelism scales well: a larger FPGA immediately allows one to instantiate more of the same design, and thus solve more problem instances at the same time. Likewise, it allows larger instances of the same problem to be solved.

Larger FPGAs and larger designs imply that the problems synthesis tools need to solve also increase in size. Already it can take hours to fully synthesize a large design. With the continued growth of FPGAs, run-times will only increase.

How much run-times can increase can be predicted by examining the computational complexity of the problems involved. Formal statements and proofs on the complexity of synthesis are not available in a clear review. While it is generally known that these problems are 'hard,' it is difficult to find exactly how hard.

This paper surveys the problems a modern FPGA flow must solve to synthesize a design described in a hardware description language (HDL) such as Verilog or VHDL. For each of these problems the complexities are surveyed. Furthermore, the complexities of computing some optimizations are surveyed.

High-level synthesis is left out of this survey, as in most cases high-level languages compile to a conventional HDL, and from that point on the process is the same.

Note that, in the literature, the term *synthesis* is not just used for the process of translating a hardware description language to a bitstream. It is also used for *logic synthesis*, which is just one step of synthesis. In this paper, *synthesis* always refers to the full process.

Some background information on complexity theory necessary to understand this paper is provided here. P and NP are classes of problems. A problem belongs to class P if it is solvable by an algorithm that runs in "Polynomial time:" the run-time grows according to a polynomial function, where the variable of the polynomial represents the size of the input to the algorithm. NP is the class of problems solvable in "Non-deterministic Polynomial" time. A non-deterministic computer (which is a mathematical construct to reason about complexity) can 'guess' how to continue instead of always applying the same next computation deterministically. When solving the problem, the non-deterministic computer has the power to always 'guess' correctly allowing it to solve problems much faster. However, if a problem is only practically solvable on such a computer, it is hard to solve in real life, where such computers do not exist and must be simulated on a regular computer which has to evaluate every guess. A problem is in NP if a polynomial time verifier exists. This verifier is an algorithm that can determine whether some solution is indeed a solution to the problem. If it can determine this in polynomial time for any solution, the problem is in NP.

Note that if a problem is in P then it must also be in NP. We can come up with an answer in polynomial time, hence we can also verify an answer in polynomial time using the same algorithm. Whether NP is also a subset of P, and therefore P = NP, is one of the greatest open problems in computer science.

If a problem is *at least as hard* as the hardest problems in NP, this problem is said to be *NP-hard*. Note that an NP-hard problem can be much harder than some problem in NP, as NP-hardness is a lower bound.

With NP-hardness as a lower bound to complexity, it is natural to consider some upper bound. Membership of NP is exactly such an upper bound. Problems that are both NP-hard

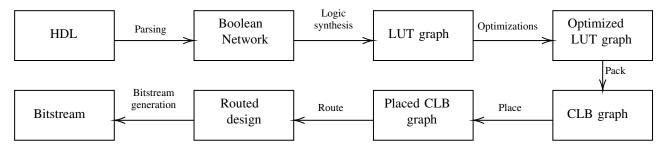

Fig. 1. A modern synthesis flow from HDL to bitstream.

and in NP are called NP-complete. Showing that a problem is NP-complete thus provides both a lower and upper bound on the hardness of the problem.

In practice, usually it turns out that if a problem is in P it is efficiently solvable, even for relatively large instances. NP-complete problems turn out to be very difficult to solve: consequently, supplying a larger input to an algorithm solving an NP-complete problem results in a much longer run-time of the algorithm. To remedy this problem a little, heuristics and approximate algorithms are used.

Complexity classes containing problems that are not in NP, but are NP-hard, also exist. One such class is  $\Sigma_2^P$ -complete [1]. For this paper it suffices to know that these problems are harder than NP-complete problems, but just like NP-complete problems,  $\Sigma_2^P$ -complete problems have a well-defined upper bound.

For more information on complexity theory, see *Computers* and *Intractability* [2].

#### II. SURVEY

#### A. Logic Synthesis

1) HDL conversions: Hardware is designed in a hardware description language (HDL). While Verilog and VHDL were designed with both synthesis and simulation in mind, most of the demand at the time was for a simulation language [3]. Therefore, these languages contain unsynthesizable simulation constructs. However, the synthesizable subset is still not one-to-one mappable to an FPGA. For example, processes containing if-statements do not map directly to a circuit, they must first be translated to a multiplexer tree. Therefore, HDL code must be converted to some representation that is one-to-one mappable to an FPGA.

A parsing and elaboration step converts HDL code to the intermediate representation of the synthesis tool. This problem is hard to translate to a formal statement, as it consists of many different algorithms which are applied to the parse tree and the details highly depend on the exact intermediate representation. A well-documented example of this process can be found in the open-source synthesis tool Yosys [4], [5].

2) Technology Mapping: The core problem of logic synthesis is that of technology mapping. Informally, this is the process of converting a circuit of Boolean functions to a circuit of size K look-up tables (K-LUTs), where K is some positive integer. Given some Boolean network B where nodes are

arbitrary Boolean functions, find some Boolean network N with K-LUTs as nodes. N must compute the same function as B. Hence, a hardware description is in this step converted to a collection of combinational circuits consisting only of K-LUTs, connected via registers. It is possible to concentrate on combinational circuits since this process can be applied for every combinational path between registers, and the registers can simply be assigned as many flip-flops as their size requires.

Note that this definition for technology mapping does not specify anything about the quality of the Boolean network. If B, or the functions on the nodes of B, are sufficiently simple (i.e. have K or less inputs), the conversion can be trivially achieved by mapping every Boolean function to a size K look-up table corresponding to that function and preserving the connection structure [6]. This technique wastes look-up tables, as it does not combine functions with less than K inputs.

To make good use of the available resources it is imperative to optimize to certain resource-minimizing measures. In the case of optimization for using the least amount of LUTs, the problem is called K-RLMP [7]: find the network N consisting of K-LUTs as described above, such that the amount of nodes is minimal. Thus solving this problem minimizes LUT usage. It has been proven that this problem is NP-complete for  $K \ge 3$ for combinational circuits in general [7], [8]. For other Kthe complexity has not been determined. Real FPGAs have look-up tables with  $K \ge 3$ , so solving a real-world K-RLMP instance is always NP-complete.

*3) Optimizations:* In synthesis tools used in industry different optimizations are applied on sub-designs, and can be applied several times [6], shrinking the inputs considerably for the latter steps, decreasing run-time and possibly delivering in a higher quality end-result.

Boolean circuit minimization optimizes the amount of gates used in combinational circuits. The problem is as follows: "given a Boolean network, find the smallest Boolean network that computes exactly the same function" [9]. Since a Boolean network corresponds to a combinational circuit, this amounts to finding a circuit that computes the same function as the input circuit using as little gates as possible. It has been shown that in general Boolean circuit minimization is  $\Sigma_2^P$ -complete [9]. This procedure is applied to combinational logic, so instances usually stay small, as in most hardware designs long combinational paths are cut by registers. Moreover, Boolean circuit minimization is such a common optimization problem that many heuristics have been developed. Therefore, even though the minimization problem is hard, it is possible to minimize or at least significantly shrink real-world circuits using Boolean circuit minimization. The high complexity does however imply that when instances do grow, the run-time of these algorithms increases significantly.

*Subcircuit substitution* is the process of identifying a part of the circuit that can be replaced by one single cell. For an FPGA that contains hardware adders, this process may identify an addition operation and synthesize it to a hardware adder instead of configuring LUTs as an adder. Ad hoc methods are able to solve this problem, for certain types of circuits. However, in general this corresponds to the subgraph isomorphism problem, which is NP-complete [10].

Finite State Machine (FSM) extraction and optimization detects finite state machines and minimizes the amount of states and control bits. This saves on routing and logic resources used by the design. For FSM extraction very efficient algorithms are available [11] which are used in practice [5]. FSM optimization entails finding the FSM with the minimum number of states performing the same function as the given FSM. Minimizing the number of states of an FSM corresponds to DFA minimization, for which an  $O(n \log n)$  algorithm exists [12].

### B. Packing

Modern FPGAs do not consist of variably interconnectable LUTs, but of connectable *configurable logic blocks* (CLBs), which can contain much more than just LUTs. Registers, multiplexers, adders, and DSP blocks are commonly found in such CLBs [13]. FPGAs can contain many types of CLBs, laid out in a grid and connectable via a reconfigurable routing network. Not necessarily every port of every circuit in the CLB is connected to the routing network.

Packing translates an optimized cell graph to a graph of configured CLBs. A configured CLB contains a configuration for the registers controlling its routing resources and LUTs such that it corresponds to the part of the cell graph that is mapped to the CLB. So, given a graph of cells (like LUTs, registers, adders, etc.) the packer maps these cells onto specific instances of those cells in a *type* of CLB available on the target architecture. The packer must preserve the connection structure as defined in the optimized cell graph when it packs several elements in the same CLB. The packer may optimize to use the minimal amount of CLBs for the given graph. Other optimization criteria, like minimizing delay, may be employed as well.

Notice that the packing problem, as presented here, is a place and route problem [13]. A CLB can contain both LUTs and routing resources, hence mapping some subgraph of the input graph to the internal components of a CLB is indeed a small place and route problem. This place and route problem is not just limited to the internal components of a CLB as it is not necessarily given how some part of the input graph may be divided over several CLBs.

The description of the packing problem has been kept very general. In practice, CLBs are far more homogeneous, or their structure is very simple. Since this highly restricts the problem, algorithms can solve this restricted packing problem in polynomial time: VPack [14] operates on CLBs that consist of *n basic logic elements* (BLE), partially connected to the global routing network via configurable multiplexers. VPack can pack designs for this simple architecture in O(kC), where *k* is the maximum fan-out, and C is the amount of LUTs in the design.

Feasible solutions are obtainable in polynomial time for real-world FPGAs. However, the general case amounts to solving placement and routing.

### C. Placement

The placement phase of digital hardware synthesis takes a graph produced by the packer and for each node allocates a specific CLB on the FPGA onto which that node will be placed. A good placement algorithm should place highly connected CLBs closely together to make the routing problem easier. Hence there is no one single 'Placement Problem': a measure must be defined to be optimized against and this results in problems of different complexity.

Two variations of the placement problem are presented: an optimization version and a constraint satisfaction version. The optimization version is defined as follows [15]: given are a set of modules M (which are CLB types accompanied by a configuration), positions P (these positions are physical CLBs to which a module may be mapped), signals S, a set of nets for every signal  $\{N_1, ..., N_{|S|}\}$ , a distance function  $d(p_i, p_j)$  where  $p_i, p_j \in P$ , a weight function  $w(N_i)$ , and some cost measuring function  $f(N_i, X)$  that computes the cost for a net  $N_i$  under a module assignment X. Such a function could be the minimum wire length of a net under assignment X, computed using the distance function d. With these givens, construct some assignment  $X : M \to P$  such that:

- 1) Each module  $m \in M$  must be assigned to some position  $p \in P$ .

- 2) Each position  $p \in P$  has either one or zero modules assigned to it.

- 3)  $\sum_{i=1}^{s} w(N_i) f(N_i, X)$  is minimal.

This definition of the placement problem corresponds directly to the Quadratic Assignment Problem [15], which has been proven to be NP-hard [16].

The other variant has the same givens and requirements, except for requirement 3) [17]:

3)  $\sum_{i=1}^{s} w(N_i) f(N_i, X) \leq L$ , for some given L.

This requirement checkable in polynomial time: simply by applying the sum and checking whether it is indeed smaller than the given L (assuming that f is a function computable in polynomial time). Therefore this version of the placement problem is both in NP and NP-hard, thus it is NP-complete.

### D. Routing

In the last step of synthesis the placed CLBs need to be connected via the routing network as defined by the placed CLB graph. Architectures of commercial FPGAs differ [18], but in general the routing network of an FPGA consists of wires, configurable switches and configurable connection points. In- and outputs of CLBs can be connected to wires via connection points and switches can be configured to connect or disconnect wires.

Because of large differences in architecture it is impractical to define one general routing problem suitable for complexity analysis [18]. A general graph-theoretic definition may be possible, but has not been attempted. A complexity result from this definition might not be useful either: routing in general may be far more complex than routing on a specific architecture.

One instance of the routing problem has been investigated in detail [19]. A Xilinx-like FPGA model was investigated where a global routing step assigns a string of connection and switching blocks to a net after which a detailed router assigns specific wires, switches and connections points for that net. It is shown that detailed routing is NP-complete [19], irrespective of the topologies of the switch blocks [20].

Little research has been done on the complexity of routing on real FPGA architectures. During most of the history of FPGAs their exact architecture was strictly proprietary and thus not available to researchers. Since any conclusions about routing depend heavily on the exact architecture hardly any results are available.

### III. CONCLUSION

To achieve a working design from a description in an HDL it is necessary to solve at least three problems that have been partially shown to be NP-complete. Applying certain optimization strategies further increases the amount of NPhard problems that must be solved. Finding an *optimal* solution requires solving all problems optimally at once, further increasing complexity.

To improve tractability of the synthesis problem many of the problems can be split up to smaller instances, since a smaller instance decreases run-time just as dramatically as a larger instance increases it. Further improving workability, approximations and heuristics for these problems exist.

The complexities of the problems involved show that the current method of synthesizing FPGA designs is not sustainable. It is already increasingly difficult to quickly prototype a large design with run-times as long as they are. Effectively utilizing future larger FPGAs for larger designs will take increasingly more time, severely hampering an engineer's ability to quickly prototype designs - one of the most distinguishing features of FPGAs.

#### References

- Sanjeev Arora and Boaz Barak, Computational Complexity A Modern Approach. Cambridge University Press, 2009. [Online]. Available: http://www.cambridge.org/catalogue/catalogue.asp?isbn=9780521424264

- [2] M. R. Garey and D. S. Johnson, "Computers and Intractability: A Guide to the Theory of NP-Completeness," 1978.

- [3] P. Flake, P. Moorby, S. Golson, A. Salz, and S. Davidmann, "Verilog HDL and Its Ancestors and Descendants," *Proc. ACM Program. Lang.*, vol. 4, no. HOPL, Jun. 2020. [Online]. Available: [https://doi.org/10.1145/3386337](https://doi.org/10.1145/3386337)

- [4] D. Shah, E. Hung, C. Wolf, S. Bazanski, D. Gisselquist, and M. Milanović, "Yosys+nextpnr: an Open Source Framework from Verilog to Bitstream for Commercial FPGAs," 2019.

- [5] C. Wolf, "Yosys manual." [Online]. Available: http://www.clifford.at/yosys/files/yosys\_manual.pdf

- [6] J. Cong and Y. Ding, "Combinational Logic Synthesis for LUT Based Field Programmable Gate Arrays," ACM Trans. Des. Autom. Electron. Syst., vol. 1, no. 2, p. 145–204, Apr. 1996. [Online]. Available: https://doi.org/10.1145/233539.233540

- [7] A. Farrahi and M. Sarrafzadeh, "Complexity of the lookup-table minimization problem for FPGA technology mapping," *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and Systems, vol. 13, no. 11, pp. 1319–1332, 1994.

- [8] A. Ling, D. Singh, and S. Brown, "FPGA technology mapping: a study of optimality," in *Proceedings. 42nd Design Automation Conference*, 2005., 2005, pp. 427–432.

- [9] D. Buchfuhrer and C. Umans, "The complexity of Boolean formula minimization," *Journal of Computer and System Sciences*, vol. 77, no. 1, pp. 142–153, 2011, celebrating Karp's Kyoto Prize. [Online]. Available: https://www.sciencedirect.com/science/article/pii/S0022000010000954

- [10] M. Ohlrich, C. Ebeling, E. Ginting, and L. Sather, "SubGemini: Identifying Subcircuits Using a Fast Subgraph Isomorphism Algorithm," in Proceedings of the 30th International Design Automation Conference, ser. DAC '93. New York, NY, USA: Association for Computing Machinery, 1993, p. 31–37. [Online]. Available: https://doi.org/10.1145/157485.164556

- [11] Y. Shi, C. W. Ting, B.-H. Gwee, and Y. Ren, "A highly efficient method for extracting FSMs from flattened gate-level netlist," in *Proceedings of* 2010 IEEE International Symposium on Circuits and Systems, 2010, pp. 2610–2613.

- [12] J. Hopcroft, "An n log n Algorithm for Minimizing States in a Finite Automaton," in *Theory of Machines and Computations*, Z. Kohavi and A. Paz, Eds. Academic Press, 1971, pp. 189–196. [Online]. Available: https://www.sciencedirect.com/science/article/pii/B9780124177505500221

- [13] J. Luu, J. H. Anderson, and J. S. Rose, "Architecture Description and Packing for Logic Blocks with Hierarchy, Modes and Complex Interconnect," in *Proceedings of the 19th ACM/SIGDA International Symposium on Field Programmable Gate Arrays*, ser. FPGA '11. New York, NY, USA: Association for Computing Machinery, 2011, p. 227–236. [Online]. Available: https://doi.org/10.1145/1950413.1950457

- [14] V. Betz and J. Rose, "Cluster-based logic blocks for FPGAs: areaefficiency vs. input sharing and size," *Proceedings of CICC 97 - Custom Integrated Circuits Conference*, pp. 551–554, 1997.

- [15] S. Sahni and A. Bhatt, "The Complexity of Design Automation Problems," in *Proceedings of the 17th Design Automation Conference*, ser. DAC '80. New York, NY, USA: Association for Computing Machinery, 1980, p. 402–411. [Online]. Available: https://doi.org/10.1145/800139.804562

- [16] S. Sahni and T. Gonzalez, "P-Complete Approximation Problems," J. ACM, vol. 23, no. 3, p. 555–565, Jul. 1976. [Online]. Available: https://doi.org/10.1145/321958.321975

- [17] W. E. Donath, "Complexity Theory and Design Automation," in Proceedings of the 17th Design Automation Conference, ser. DAC '80. New York, NY, USA: Association for Computing Machinery, 1980, p. 412–419. [Online]. Available: https://doi.org/10.1145/800139.804563

- [18] Gomez, Daniel and Ciesielski, Maciej, "A Tutorial on FPGA Routing," 01 2008.

- [19] Yu-Liang Wu and Tsukiyama, S. and Marek-Sadowska, M., "Graph based analysis of 2-D FPGA routing," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 15, no. 1, pp. 33–44, 1996.

- [20] Y.-L. Wu, S. Tsukiyama, and M. Marek-Sadowska, "On computational complexity of a detailed routing problem in two dimensional FPGAs," in *Proceedings of 4th Great Lakes Symposium on VLSI*, 1994, pp. 70–75.

Chapter 3

# On Productive, Low-Level Languages for Real-World FPGAs

# On Productive, Low-Level Languages for Real-World FPGAs

Pieter Staal

University of Twente Enschede, the Netherlands p.j.staal@student.utwente.nl

*Abstract*—FPGA designs are described in either Verilog or VHDL (HDLs), or in a high-level synthesis language that compiles to one of these. HDLs, however, are such an abstraction over FPGAs that the synthesis process is convoluted. Hence, hardly any *control* is available to hardware designers, hindering them in maximizing the performance of FPGAs.

To show that languages with more control than HDLs are possible, "Ex-PART" was designed and developed: a language that enables fine-grained control over placement of modules. The hypothesis is posited that the hierarchic structure of a hardware design corresponds well with a structure of adequate placement directives for FPGAs.

Non-trivial hardware was designed in Ex-PART demonstrating that it behaves as intended. For many designs the hypothesis held true. For the largest design it did not: a much better result was obtained by placement directives that were decoupled from the program structure.

These findings show that it is possible and practical to build low-level hardware design languages in which substantial hardware can be designed. However, if designers need to optimize their FPGA designs to their maximum potential, a future lowlevel languages must decouple placement directives from the program structure.

*Index Terms*—FPGA, low-level language, Digital Hardware Design

### I. INTRODUCTION

The languages in use today for the description of FPGA designs were not conceived specifically for FPGAs. Verilog and VHDL (*Hardware Description Languages* or HDLs) describe digital hardware in general, not specifically targeted for an FPGA architecture. This mismatch in purposes becomes apparent with issues such as long synthesis times, and a lack of fine-grained control over the synthesis process. Contemporary HDLs do not include features that can solve these problems elegantly.

When every last bit of performance must be squeezed from the FPGA a language with a high degree of *control* is required. Compare software engineering, where an embedded engineer with very limited resources can use a language such as C to manage these in detail. A language providing much control over the resources of the target architecture is classified as a *low-level* language.

For processors, languages with a high degree of control exist: C provides all the power a software engineer needs to exert full control over the final product, while providing abstractions to efficiently develop software. These features are what is intended with a *productive, low-level language*. Such

languages do not exist for FPGAs: the "lowest" level language available to hardware designers are the conventional HDLs.

For example, a feature that can increase control that is not available in HDLs is determining *where* some part of a design should be placed on an FPGA. Sometimes this is possible, but only by using synthesis directives which are not part of the language itself and may be ignored by the compiler.

In this paper, we present a new language, "Ex-PART", and a synthesis flow that implements it. The language is equipped with features allowing hardware designers to make informed design decisions on the exact location of components, or hierarchies of components, on the target FPGA.

Instead of developing an entire synthesis tool from scratch, we extended open-source tools for both logic synthesis and place and route to support our language features. This allowed us to test whether it is practical to design non-trivial hardware in Ex-PART and to evaluate the results.

In Ex-PART, a designer can specify coordinates and sizes for modules in a hardware design, facilitating fine-grained control over placement. Using coordinates and sizes for hardware modules in the language is based on the hypothesis that there is a good match between the structure of the hardware design and the structure of the placement on the FPGA.

This hypothesis is stated as follows:

**Hypothesis 1** The hierarchic structure of a hardware design corresponds well with a structure of adequate placement directives.

However, our results show that this hypothesis does not hold in general.

The main contributions of this paper are:

- 1) Ex-PART, an HDL that offers fine-grained control over placement on FPGAs (Section III).

- 2) An extension to the open-source synthesis toolchain implementing Ex-PART (Section III-E)

- Three hardware designs (Section IV) show that hypothesis 1 does not hold in general (Section V-A) providing important feedback on the development of other lowlevel FPGA languages (Section V)

#### II. RELATED WORK

Research on unifying HDLs has been conducted. LLHD (Low-Level Hardware Description) [1] is a language that aims to be an intermediate representation for any hardware

description language. LLHD has three versions: behavioral, structural, and netlist. Note that LLHD stops at the netlist level because LLHD needs to be synthesizable to both ASICs and FPGAs. Therefore, it is impossible to incorporate FPGA-specific information like placement and routing constraints into a language that compiles to LLHD.

A low-level FPGA language does exist: Reticle [2] aims to describe modern FPGAs at the tile level. It includes support for LUT and DSP tiles. Reticle is meant as a compilation target, and transforming Reticle to a bitstream is extremely fast because the language is so close to the FPGA hardware. As Reticle is a compilation target, it is not productive to program directly in Reticle (Similar to programming in Assembly for a processor). A language such as Reticle would, however, be an appropriate compilation target for a low-level language.

In [3] the FPGA is divided into regions in which parts of the design may be placed. The regions are then connected via a packet-switched network as a communication channel between the sub-designs. By splitting up the design, synthesis run-times can be reduced: a smaller design decreases runtime just as drastically as a larger design increases it. This strategy allows parallel synthesis of the sub-designs, further decreasing the run-time of synthesis. Designs built in this scheme should not be subdivided very often since connecting very small, simple, components via a packet-switched network wastes FPGA resources. Moreover, the strategy applied here is not integrated into a language.

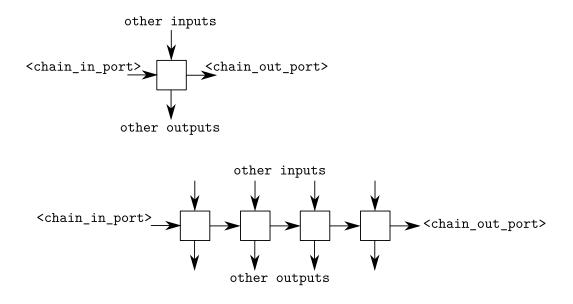

### III. EX-PART

Describing hardware in Ex-PART consists of two phases: First, components are defined. Then instances of those components are laid out and connected. Inspired by C's header system, these phases happen in two separate files: respectively the "component file" and the "instantiation file".

### A. Component Definition

Every component is modeled as a mealy machine, which enables the description of sequential hardware. A component without a state describes combinational hardware. A component may have any amount of inputs, states, and outputs. Each of these properties is annotated with a *type*. Inputs and outputs can only be connected if they are of the same type. States must additionally be supplied with an initial value. As an example, defining a 16-bit unsigned integer state with initial state zero and name 'counter' is written as:

state counter = 0 : Unsigned 16

The types used are those of the high-level synthesis tool Clash, which will be elaborated on in Section III-E.

For every output and state, an expression describing its relation to the inputs and previous state must be defined. The syntax for these expressions is that of a Haskell expression. The current state and next state are differentiated by adding a prime (') to the state name to designate the next state.

For example, incrementing the state 'counter' by some amount set on the 'interval' input is denoted as:

counter' = counter + interval

third<sup>1</sup> is compute<sup>2</sup> in  $(5, 5)^3$  at  $(second.x^5 + second.w, 0)^4$

Fig. 1. Example instantiation of a component. 1. Name given to this instance; 2. Name of component to be instantiated here; 3. Width and height of component; 4. Coordinates of the top left corner of this component; 5. X property of instance named 'second'; 6. Width property of component named 'second'.

The complete code of a simple combinational component is shown in Figure 3.

It is possible to add arbitrary Haskell code in a haskell block. In such a block, data types and type synonyms may be defined as well. These definitions can be used in every component definition.

#### B. Instantiation and Connection

The components defined in the component file are laid out and connected in the instantiation file. Instantiation files are structured as a hierarchy of modules. Modules can have inputs and outputs annotated by types as in component definitions. A module is located at a certain position on the FPGA and is of a certain size. These properties are given through x and y coordinates and width and height numbers. In denoting these properties, the size and location information of other modules and components may be used. Modules may contain submodules, component instantiations, and connections. All coordinates used in one module are relative to the topleft corner of that module. Submodules define a hierarchy in modules and ease working with the coordinate notation. Component instantiation statements place a component defined in the component file at a certain position and allocate some rectangular area for the component, as shown in Figure 1. Again, this position is relative to the position of the module in which this component is instantiated. Connections connect ports from components and modules to other ports. An example of connecting the output port of one component to the input port of another is given in Figure 2.

Note that this definition allows overlapping components. Overlap gives the placer more freedom to find better placements. Good placements on FPGAs are often not rectangular, or components may be interconnected thoroughly. In these cases some or full overlap of components yields much better results. Hence, the hardware designer can decide how large the solution space is that the placer must explore by adjusting the amount of overlap.

To ease the development of larger designs, features are available for repetitive layouts of components and their connections. These language constructs are all elaborated to modules utilizing only submodules, instances, and connec-

Fig. 2. Example of a connection between the output port of one component instantiation and the input port of another; 1. Name of the source instance; 2. Name of the output port of this instance; 3: Arrow syntax to denote connection; 4. Name of the destination instance; 5. Name of an input port of the destination instance.

```

component on_odd()

1

input value : Maybe Value

2

output result : Maybe Value

3

4

result = case value of

5

Just v -> Just (v *

3

+

1)

6

Nothing -> Nothing

8

}

```

Fig. 3. Description of the component on\_odd

tions. Documentation and usage examples are available in the repository [4].

### C. Design Feedback

Overviews of metrics like area usage, maximum frequency, and synthesis times for the entire design and for individual components can be provided by a script.

Both the bitstream and the location information can be visualized. The visualizer shows changes immediately when compiling. Therefore, it is possible to monitor important properties of the design during development.

Clash can be used to verify the functional correctness of a design. It provides an interactive interface that allows simulating the defined module and all its submodules with arbitrary inputs. It is possible to automate these tests with testing libraries.

### D. Example Design

This walk-through exhibits the design process of a simple module in Ex-PART. This module applies the rules of the Collatz conjecture to an integer n in a register. After cycle i, the value of n is given by:

$$n_{i+1} = \begin{cases} n_i/2 & \text{if } n_i \text{ is even} \\ 3 \cdot n_i + 1 & \text{if } n_i \text{ is odd} \end{cases}$$

(1)

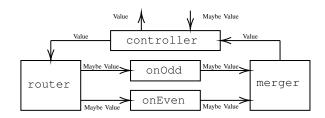

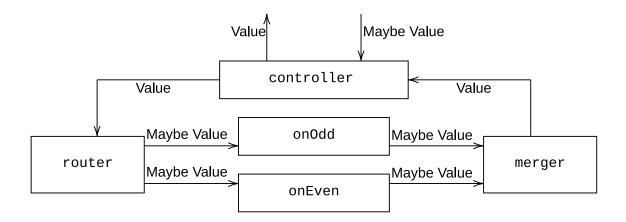

*Components:* To realize this design five components are defined in the component file.

- 1) control stores the value of *n*, and sets a new value for *n* if it is provided on its input.

- 2) on\_odd performs the computation for odd n.

- 3) on\_even performs the computation for even n.

- router sends n from the controller to either on\_odd or on\_even, depending on the parity of n.

- 5) merger takes the result from either on\_odd or on\_even and sends it to the controller.

The components are to be connected as shown in Figure 4, where the arrows are annotated with the type of the ports they connect.

The definition of the on\_odd component is shown in Figure 3. Both its input and output are of type Maybe Value: there can either be a value on the input, or Nothing, signifying that there is no input. In hardware, this would be translated into a port with enough bits to contain the representation of Value, and one extra bit signifying whether the value is Nothing. The relation between the input value and the output result is defined in the case expression. It states that if value is of the form Nothing, emit Nothing again. If it does contain

Fig. 4. Architecture for the Collatz conjecture calculator.

a value, multiply that value by three and add one, as is the definition for the odd case in equation 1. Notice that this is a combinational piece of hardware: the relation between input and output is defined directly, without state.

When a component has been defined in Ex-PART, one can inspect properties such as area usage. The visualizer can render these results and an analysis script gives a quick overview of resource usages reported by the tools.

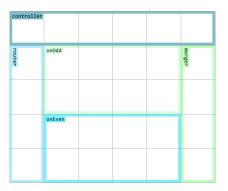

Using similar information for the remaining components of the Collatz design, a layout is defined in the instantiation file which is shown in Figure 5. Plenty of space is taken for each component and connections are not shown. An explanation of important lines is provided below.

- 1: The definition of the top-level module. The top-level module must have a constant expression for its coordinates, as its position is what the coordinates of every submodule and component depend on. It is instantiated at (2, 2) as on the target architecture the two leftmost columns and the two topmost rows do not contain any LUTs. An area of six by five tiles is deemed sufficient for the whole module.

- 2: Modules have inputs and outputs. As these are the I/O of the top-level module, they will be connected to the I/O pins of the FPGA.

- 5: This is one of the component instantiations. In the component file, the control component was defined. This instantiation has been given the name controller and an area of six tiles at the top of the module is allocated.

- 7: The submodule update\_n is defined. Its location is relative to its parent module's location, thus we can instantiate it at (0, controller.h) to place the whole module exactly under the controller component. Its width is set equal to that of the controller, and height is set as the remaining module height.

- 8: Similarly to the top-level module, the update\_n module also exposes its internal data to two ports. An input and output port are defined. This definition shows that we can place a value at the input of this module, and the module will return the new value according to the rules of the Collatz conjecture.

- 13: The instantiation of the on\_odd component. Its width and location are defined in terms of other components to make resizing and moving easier.

*Connections:* Every component has input and output ports. These ports can be referenced in a connection statement. The

```

collatz in (6, 5) at (2, 2) {

1

input setting : Maybe Value

2

output result : Value

3

4

controller is control in (6, 1) at (0, 0)

5

6

update_n in (controller.w, 4) at (0, controller.h) {

7

input value_in : Value

8

output value out : Value

9

10

router is router in (1, on odd.h + on even.h)

11

12

at (0, 0)

on_odd is on_odd in (update_n.w - 2, 2)

13

14

at (update n.x + 1, 0)

on_even is on_even in (on_odd.w, on_odd.h)

15

16

at (on_odd.x, on_odd.h)

merger is merger in (1, on_odd.h + on_even.h)

17

18

at (on_odd.x + on_odd.w, 0)

19

}

20

}

Fig. 5. Instantiation file for the Collatz example.

```

connections in the update\_n module are shown in Figure 6. An explanation is provided of the important lines:

- 1: When no component is specified, as with value\_in in this statement, the current module's I/O ports are intended. Hence, this connection statement connects the input value\_in of the update\_n module to the input value of router. As these are both of the type Value, this connection is possible.

- 2: This is a connection internal to the update\_n module. The odd port of the router component is connected to the value port of the on\_odd component.

- 4: The result port of on\_odd is connected to the value\_odd port of merger.

- 6: The value at the result port of merger is the result of the calculation and should therefore be routed out of the module via the value\_out port.

The rest of the connections can be found in the complete example in the repository [4].

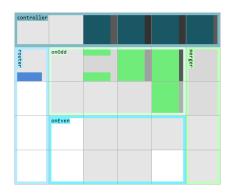

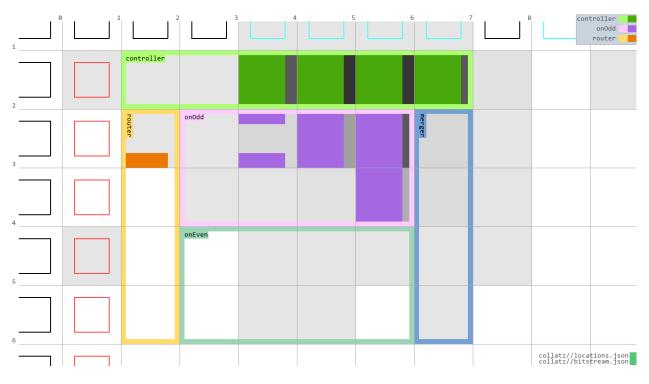

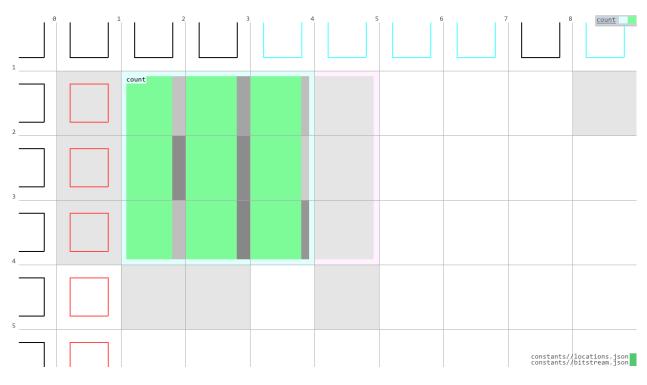

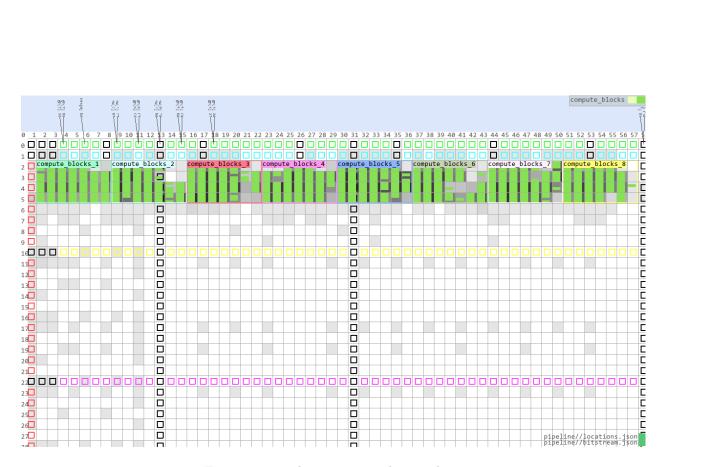

*Visualization:* Since coordinates usually do not speak to the imagination, we also supply a visualizer that can show both bitstreams and layout definitions. Therefore, it is possible to check with the visualizer whether the layout is as intended. The layout defined in Figure 5 is shown in Figure 7.

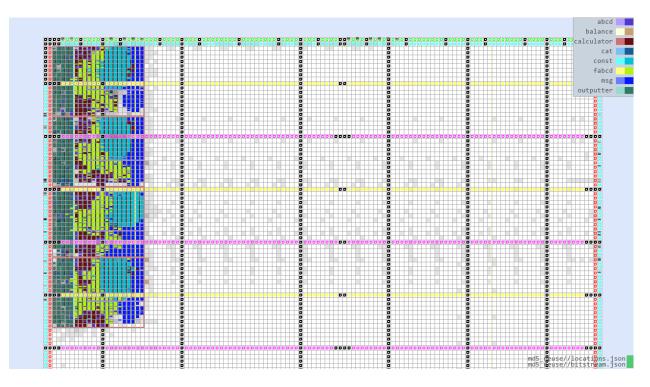

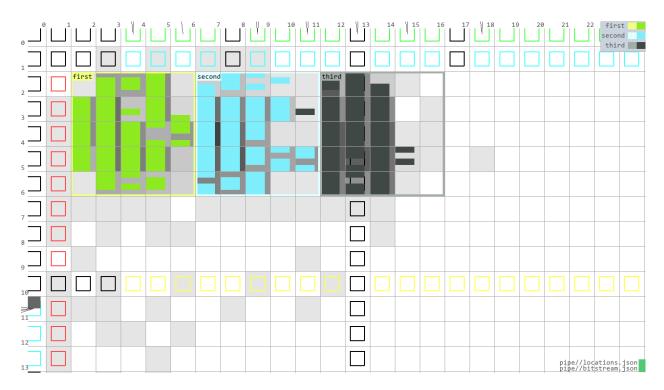

*Synthesis:* With the components, layout, and connections specified the design can be synthesized and the result is shown in Figure 8. This is a visualization of the bitstream generated by the tools Ex-PART employs. This bitstream can be flashed to a Lattice ECP5 FPGA.

This visualization should be read as follows: FPGAs consist of a grid of *tiles*. Every square in the visualization is such a tile. Each tile on the ECP5 contains four *slices*, which are drawn as a colored horizontal rectangle. A slice contains two registers and two 4-bit LUTs. Notice that the background of

- 3 router.even->on\_even.value

- 4 on\_odd.result->merger.value\_odd

6 merger.result->value\_out

Fig. 6. Connections defined in the update\_n module.

Fig. 7. Layout of the Collatz example, as shown by Ex-PART's visualizer.

Fig. 8. visualization of the bitstream as synthesized for the Collatz conjecture example.

a tile is not always white: the brightness of a tile illustrates the usage of routing resources on that tile: the darker it is, the more resources are used.

Some conclusions can be drawn based on this visualization. Conceptually, on\_odd and on\_even perform similar tasks. In hardware these differ: dividing by two is the same as a shift of one bit which is just a rearrangement of wires while calculating the odd branch requires LUTs. Therefore, fewer resources should have been allocated to the on\_even component. Similarly, the router uses just one slice, but four tiles have been allocated. On the other hand, examining the controller shows that decreasing its area may not work: it uses two-thirds of its slices and many routing resources. With this information, the design can be reworked to use much less area. Thus the visualization gives valuable feedback on the resource usage of components.

### E. Implementation

To be able to focus on language design, and target a real FPGA, existing tools were repurposed. This choice resulted in a compilation process that seems quite elaborate; however, it actually enabled rapid prototype development.

Auxiliary Tools: To synthesize Ex-PART we use three existing tools for Verilog generation, logic synthesis, placement, and routing. All tools used by Ex-PART are open-source. Using open-source tools as the back-bone of the language gives us the freedom to inspect the processes employed

value\_in->router.value

<sup>2</sup> router.odd->on\_odd.value

<sup>5</sup> on\_even.result->merger.value\_even

whenever necessary. This, along with well-document input and output formats, allow fast development of experimental software extending these tools.

*Clash* [5] is used to generate Verilog. Clash is a highlevel synthesis tool that can transform hardware descriptions in Haskell to Verilog or VHDL. Haskell's syntax was deemed very concise and appropriate for the description of expressions in Ex-PART, and it is relatively easy to generate programmatically. By repurposing Haskell's syntax in Ex-PART it is straightforward to generate Clash components from a description in Ex-PART.

*Yosys* [6] is an open-source logic synthesis tool. It can synthesize Verilog for some FPGAs. Yosys' outputs are in the JSON format which is human-readable and easy to work with programmatically. The specification of the output is well-documented. For features absent in the documentation, Yosys' code is available for inspection.

To perform placement and routing for the ECP5 FPGA *nextpnr* [6] is used. This tool can perform placement and routing given a JSON file generated by Yosys. It can output a JSON file describing the placed and routed design, or a textual configuration file that can easily be converted to a bitstream that can be flashed to the ECP5.

*Compilation:* In summary, compilation from Ex-PART to the ECP5 FPGA consists of the following steps:

- 1) Parse the component and instantiation file.

- 2) Elaborate the design.

- 3) Calculate absolute positions.

- 4) Generate Clash for simulation and synthesis.

- 5) Compile Clash to Verilog per component.

- 6) Synthesize the components with Yosys.

- 7) Connect and instantiate components as defined in the instantiation file.

- 8) Place and route the resulting design with nextpnr, constraining locations.

The component and instantiation files are read and parsed. The parsing process produces data structures representing the hardware design. Many of the constructs available in Ex-PART can be elaborated into simpler constructs. Thus elaboration converts the design into a design that only uses connections, component instantiations, and submodule definitions. The rest of the compilation is applied to the elaborated data structure.

A file (locations.json) with absolute coordinates of the top-left and bottom-right corner of every component instantiation is generated. This file is used in constraining LUT locations during placement.

Every component is compiled to its own Clash file. Such files can be loaded in the interactive Clash environment to validate the functional correctness of the design through simulation.

For every component, the generated Clash is compiled to Verilog, as that is the format accepted by the synthesis tool Yosys. Notice that synthesis has to be applied only once for every component, even if it is re-used. The entire design is *not* compiled to Verilog: only every bottom-level component that is defined in the component file.

The generated Verilog files are synthesized with Yosys. Yosys produces a JSON file describing the design in terms of look-up tables and flip-flops. Note that Yosys could be configured to synthesize to more complicated cells, such as DSP blocks. This does imply that when a component uses such cells, the designer must place the component in an area that contains such cells. After logic synthesis by Yosys, the connections, instantiations, and hierarchy described in the instantiation file are converted into Yosys' JSON format and appended to this file.

The resulting JSON file is processed by nextpnr to place and route the design on the ECP5 FPGA. A Python script is executed just before the placement step to constrain the placement of look-up tables. The script looks up the rectangular area a LUT should be in, in the locations.json file that was generated earlier. If the designer did not supply enough area for a component, nextpnr will throw an error.

If every component did indeed get enough space for all its LUTs, registers, and connections, nextpnr produces textual bitstream files, which can be converted into a binary bitstream for programming an ECP5 FPGA. The visualizer can show where all the LUTs are placed.

Note that in this implementation *constraints* are added to the placer which may make the problem at hand harder to solve. We chose this strategy as it was the fastest route to realization.

A detailed description of the compilation process and the complete code are available in the repository [4].

### IV. RESULTS

### A. Compilation Flows

Ex-PART comes with three alternative compilation flows to compare the results of different synthesis strategies.

- 1) *Ex-PART* takes location and size annotations into account when synthesizing the design.

- 2) Hierarchic: The design is split into Verilog modules as a designer using a conventional HDL would do. Every component is compiled to a separate Verilog module. This generates HDL code organized similarly to how a hardware designer would have. No placement constraints are applied.

- 3) *Monolithic*: No modules are generated at all. One fully flattened design is generated such that the synthesis tool can optimize between module interfaces.

For three examples the placements are shown: the Collatz example from Section III-D, a parallel MD5 hash calculator, and a simple manycore. To further compare the costs and benefits of each flow, performance metrics like maximum frequency, area usage, and synthesis run-times for all three flows are given.

### B. Collatz Conjecture Calculator

The placement found for the Collatz conjecture calculator is shown in Figure 8. The results of running all three flows for this module are shown in Table I.

|                                                             | Ex-PART | Hierarchic | Monolithic |  |  |

|-------------------------------------------------------------|---------|------------|------------|--|--|

| LUTs                                                        | 54      | 54         | 49         |  |  |

| $f_{max}$ (MHz)                                             | 122.29  | 132.01     | 148.46     |  |  |

| Flip-flops                                                  | 32      | 32         | 32         |  |  |

| Synthesis time (s)                                          | 0.75    | 0.74       | 0.6        |  |  |

| Placing time (s)                                            | 0.05    | 0.04       | 0.04       |  |  |

| Routing time (s)                                            | 0.07    | 0.06       | 0.1        |  |  |

| Total time (s)                                              | 0.87    | 0.84       | 0.74       |  |  |

| TABLE I                                                     |         |            |            |  |  |

| Desire as a set of the set of the set of the set of the set |         |            |            |  |  |

RESULTS FOR THE COLLATZ CONJECTURE CALCULATOR.

### C. MD5 Hasher

MD5 [7] is a hashing algorithm. Although it has fallen out of use for cryptographic purposes, it is a good demonstrator for Ex-PART as the calculation of an MD5 hash is not trivial.

This design can hash 128-bit messages. These messages are provided in 32-bit chunks. When four chunks have arrived, the hasher starts. It applies the MD5 algorithm in 64 cycles. When finished, the 128-bit hash is emitted in 32-bit chunks in four cycles.

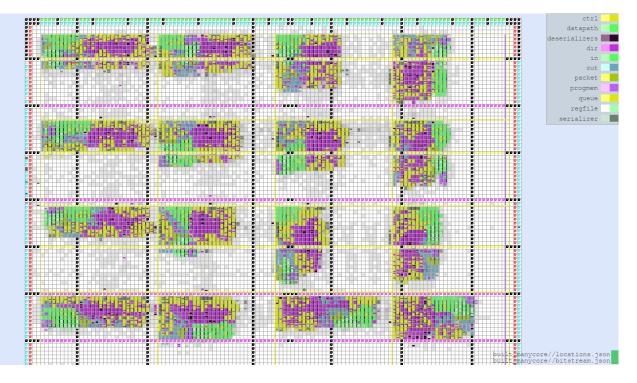

Module re-use is used to instantiate the hasher four times, demonstrating Ex-PART's productivity. A load balancer divides the incoming message words over the four hashers to compute four hashes in parallel.

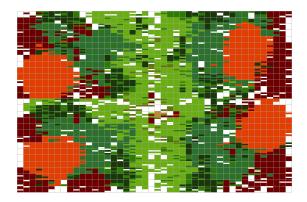

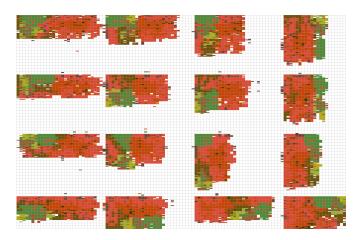

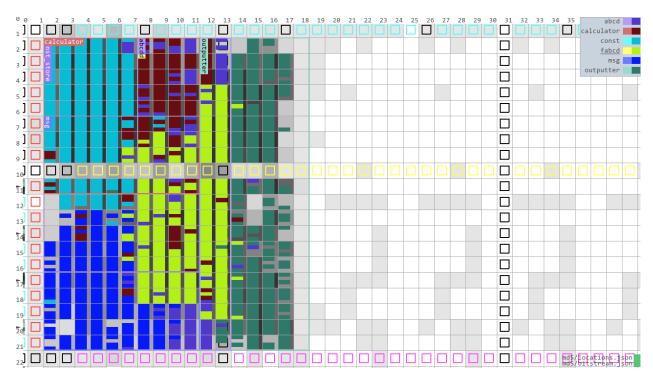

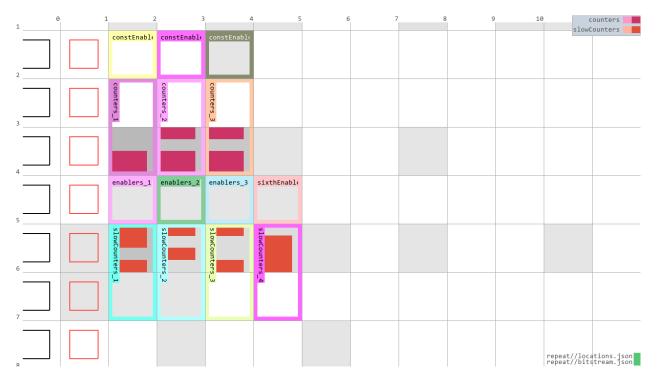

The placement found by the hierarchic flow is shown in Figure 9. The default placement algorithm found a rectangular area and a roughly symmetric placement for the four hashers. The total design takes up a rectangle of 44 by 29 tiles, or 1279 tiles in total. For the sake of showing that Ex-PART can impart control over placement, suppose instead a linear layout is desired. Such a layout was defined in Ex-PART, and the result is shown in Figure 10. This layout fits in an area of 20 by 62 tiles, occupying 1240 tiles in total. Hence, this layout uses a very similar amount of space as the hierarchic flow, showing that a linear layout could be achieved without wasting area.

In Table II the rest of the metrics are shown. The monolithic run takes much more time to synthesize as it applies logic synthesis to the entire design at once, instead of optimizing smaller modules separately. The place and route time of the Ex-PART flow is longer than the hierarchical. This is due to the stricter constraints on placement that are applied by the designer in Ex-PART. The hierarchical design is free of such constraints. Note that the quality of the designs does not differ much: the maximum frequency  $f_{max}$  is nearly identical for every flow.

|                    | Ex-PART | Hierarchic | Monolithic |

|--------------------|---------|------------|------------|

| LUTs               | 6606    | 6602       | 6249       |

| $f_{max}$ (MHz)    | 17.04   | 17.45      | 18.38      |

| Flip-flops         | 3176    | 3176       | 3176       |

| Synthesis time (s) | 5.02    | 5.91       | 25.32      |

| Placing time (s)   | 49.56   | 31         | 30.38      |

| Routing time (s)   | 25.76   | 12.43      | 12         |

| Total time (s)     | 80.34   | 49.34      | 67.7       |

|                    | TABLE   | П          |            |

RESULTS FOR THE FOUR MD5 HASHERS.

Fig. 9. Placement of four MD5 hashers by the hierarchic flow.

Fig. 10. Linear placement of the MD5 example, constrained as such by the placement directives in Ex-PART.

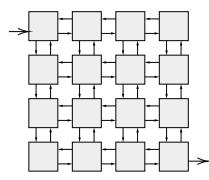

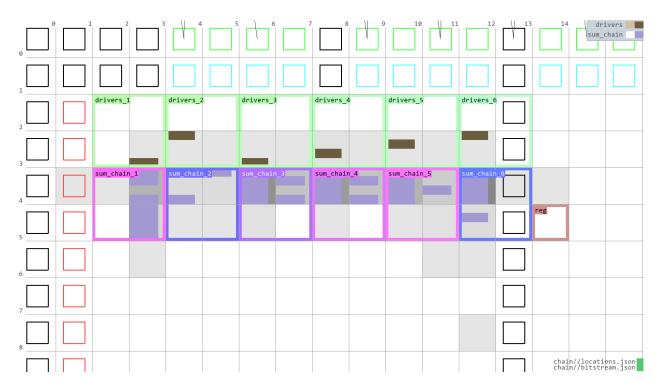

### D. $4 \times 4$ Manycore

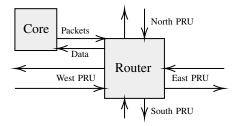

A manycore was designed to exhibit designing hardware requiring more resources in Ex-PART. The manycore consists of very elementary processors with four 8-bit registers, six instructions, and a program memory of 32 instructions. They are connected via a packet-switched network in a grid topology. Each processor is paired with a router providing access to the on-chip network. This Processing and Routing Unit (PRU) is laid out in a grid. The processor and router were kept simple to be able to synthesize many PRUs for a relatively small FPGA.

The architecture of a PRU is shown in Figure 11. The processor reads incoming packets from a FIFO and pushes packets into the routing network via another FIFO. The router

Fig. 11. Design of a Processing and Routing Unit, the main building block of the manycore.

Fig. 12. Architecture of the  $4 \times 4$  manycore.

uses a simple decision procedure based on its location and the destination location in the packet to send incoming packets to their destination.

The architecture of the manycore is shown in Figure 12. The cores are linked to their neighboring PRUs through the routers via their north, east, south, and west I/O ports. On the fringes of the network one input and one output are located to feed data into the network and receive results from the cores. These are constrained to I/O ports of the FPGA.

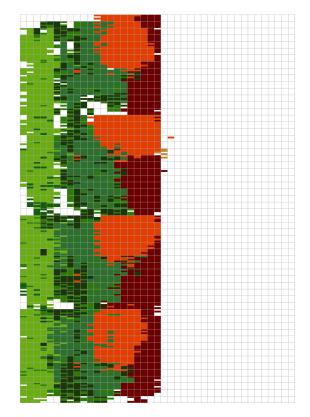

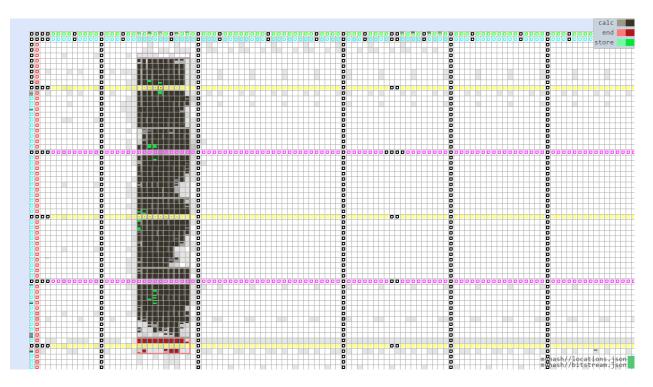

A space-efficient placement of the manycore was hard to achieve. In Figure 13 one placement obtained by Ex-PART is shown, and in Table III the metrics of synthesizing this design are shown. The Ex-PART flow is faster than the hierarchical flow because the hierarchical flow places the cores close to eachother while in Ex-PART the designer can pre-emptively leave room between the PRUs to make routing easier.

Notice the discrepancy between the amounts of LUTs used between the three flows. The monolithic flow manages to optimize out one-third of the LUTs, resulting in saving a huge amount of time during placement and routing and obtaining a higher maximum frequency. The main difference between the Ex-PART and hierarchic flow, and the monolithic flow is that the monolithic flow can optimize over the interfaces between modules. This strategy increases synthesis run-time, as is clear from the results: the monolithic flow runs more than ten times as long. In this case, however, the extra time spent during synthesis saves much time during placement and routing.

Upon further inspection, the large optimization was achieved mainly between routers. The conceptual design of this manycore favors routers and processors to be grouped as one unit, the PRU. However, this conceptual separation of routers in the network implies a physical separation as well,

|                           | Ex-PART | Hierarchic | Monolithic |  |  |

|---------------------------|---------|------------|------------|--|--|

| LUTs                      | 14560   | 14848      | 9954       |  |  |

| $f_{max}$ (MHz)           | 58.3    | 57.4       | 74.24      |  |  |

| Flip-flops                | 17632   | 17632      | 14932      |  |  |

| Synthesis time (s)        | 3.93    | 7          | 87.2       |  |  |

| Placing time (s)          | 128.63  | 147.26     | 63.06      |  |  |

| Routing time (s)          | 353.42  | 2007.7     | 35.78      |  |  |

| Total (s)                 | 485.98  | 2161.96    | 186.04     |  |  |

| TABLE III                 |         |            |            |  |  |

| RESULTS FOR THE MANYCORE. |         |            |            |  |  |

Fig. 13. A placement of the  $4 \times 4$  manycore found through Ex-PART. Each PRU is clearly visible as a separate entity.

by hypothesis 1. When the design was arranged such that the entire routing network was one optimizable module, indeed a similar result as the monolithic flow was found.

#### V. DISCUSSION

#### A. Hypothesis

During the design of Ex-PART, hypothesis 1 on the correspondence of design hierarchies and adequate placements was assumed to hold. The results of the MD5 design show that there are designs for which the hypothesis is true; however, the development of the manycore shows that the hypothesis does not hold in general: the structure of a design may be pleasant to work with, easy to expand, and easily modified, but using this structure as a directive for placement did not yield an adequate placement. Hence, it is critical for a low-level language for FPGAs to take into account that the structure of the design cannot be linked in a one-to-one fashion to directives involving low-level features. This result is vital for the further development of Ex-PART, or the design of other low-level languages.

The manycore design did show that the designer had control over placement. In this case, the design for the routing network was split up such that certain optimizations were not detectable for the tools; hence, the conceptual structure of the design induced a sub-optimal design. However, in the placement the conceptual separation of the PRUs *is* still visible, showing that Ex-PART works as intended.

### B. Open-source Synthesis Tools

To gain more control over synthesis, placement, and routing of hardware designs tools must provide clearly documented input and output formats: the fact that Yosys and nextpnr do provide this, entirely enabled the development of Ex-PART. If every step in a synthesis flow produces and consumes open files anyone can inject their own processing just as has been done for Ex-PART enabling the development of low-level FPGA languages and thereby giving hardware designers just as much freedom in their tools as software engineers.

When the tools are open-source as well, any lacking documentation can be compensated for by investigating the source code. Bugs in custom processing can also be resolved more conveniently when the source code is available for debugging.

#### C. Routing

Ex-PART focuses on placement; however, a low-level language could allow hardware designers to put constraints on routing as well. The granularity of this control can vary immensely: a language may require designers to specify paths completely, or allow designers to specify parts of paths while the tooling figures out the rest. The design of a language that effectively incorporates this control in its syntax and semantics is future work.

#### D. Synthesis Speed

To apply the placement directives, Ex-PART supplies extra constraints to the place and route tool. This method may introduce harder to solve constraints resulting in longer place and route times. However, it did enable the fast development of Ex-PART as this method is supported by nextpnr. A low-level FPGA language could be designed with synthesis speed in mind. A language where hierarchies are synthesized, placed, and routed completely separately can be much faster than current synthesis tools. Synthesis consists of three NPcomplete or harder problems [8], thus having the designer split up the design into smaller problems decreases the individual run-times of the sub-designs such that the sum of their runtimes is smaller than synthesizing the entire design at once. The smaller designs must then be connected correctly again, this corresponds to another (quite small!) routing problem. Such strategies are only possible when the designer annotates where the design can be split up.

### E. Dynamic Partial Reconfiguration

Language features constraining placement as in Ex-PART may be combined with dynamic partial reconfiguration. Defining rectangles for modules within the language in which the hardware is designed explicitly shows when components can be interchanged. A tool strictly enforcing such area allocations eases working on reconfigurable designs.

#### VI. CONCLUSION

The development of Ex-PART was sparked by the lack of languages offering fine-grained control over synthesis, placement, and routing of hardware designs intended for FPGAs. In the design of Ex-PART, the assumption was made that the structure of a design corresponds well with a structure of adequate placement directives.

To evaluate Ex-PART three designs were developed: a Collatz conjecture calculator, a parallel MD5 hash calculator, and a rudimentary manycore. For the first two designs, Ex-PART proved very effective: the designs could be laid out in a largely different layout from the regular synthesis tools, proving that Ex-PART grants designers more control.

However, the manycore design demonstrated that linking placement directives to design structures does not always yield good results. The conceptual separation of cores in the manycore worked well during development, but inhibited the tools from making an extreme optimization.

This shows that the hypothesis does not hold in general. This result is critical in the development of other low-level FPGA languages as it implies that directives increasing control should to be decoupled from hierarchic design constructs.

Ex-PART opens up a lower level FPGA programming style previously inaccessible to hardware designers. With placement design decisions embedded inside the language, and tools available to make these decisions in an informed manner, placement can be performed *while* describing the hardware. It has been shown that developing a language like Ex-PART is highly feasible with modern open-source synthesis and place and route tools. New productive, low-level languages will open up FPGAs enabling skilled hardware designers to use FPGAs up to their maximum potential.

#### REFERENCES

- [1] F. Schuiki, A. Kurth, T. Grosser, and L. Benini, "LLHD: A multi-level intermediate representation for hardware description languages," *CoRR*, vol. abs/2004.03494, 2020. [Online]. Available: https://arxiv.org/abs/2004.03494

- [2] L. Vega, J. McMahan, A. Sampson, D. Grossman, and L. Ceze, "Reticle: a virtual machine for programming modern FPGAs," in *PLDI '21: 42nd ACM SIGPLAN International Conference on Programming Language Design and Implementation, Virtual Event, Canada, June 20-25, 2021*, S. N. Freund and E. Yahav, Eds. ACM, 2021, pp. 756–771. [Online]. Available: https://doi.org/10.1145/3453483.3454075

- [3] Y. Xiao, D. Park, A. Butt, H. Giesen, Z. Han, R. Ding, N. Magnezi, R. Rubin, and A. DeHon, "Reducing FPGA compile time with separate compilation for FPGA building blocks," in 2019 International Conference on Field-Programmable Technology (ICFPT), 2019, pp. 153–161.

- [4] P. J. Staal and H. H. Folmer, "Ex-PART." [Online]. Available: https://github.com/PietPtr/Ex-PART

- [5] "Clash," https://clash-lang.org, accessed: 2021-12-21.

- [6] D. Shah, E. Hung, C. Wolf, S. Bazanski, D. Gisselquist, and M. Milanovi, "Yosys+nextpnr: an open source framework from Verilog to bitstream for commercial FPGAs," 2019.

- [7] R. Rivest, "The MD5 message-digest algorithm," Internet Requests for Comments, RFC Editor, RFC 1321, 4 1992. [Online]. Available: https://www.rfc-editor.org/rfc/rfc1321.txt

- [8] P. J. Staal, H. H. Folmer, "Computational complexities in modern FPGA synthesis flows," *unpublished*, 2022.

# Chapter 4

# **Design Decisions**

# 4.1 FPGA Design Descriptions

The lowest level hardware description languages available to FPGA engineers are Verilog and VHDL. The results from the survey paper on computational complexities [1] show that the conversion from HDLs to an FPGA design is three times NP-hard. Furthermore, HDLs obscure many features inherent to FPGAs: where some part of the design is placed and how it is routed is entirely hidden from the perspective of an HDL. Hence, HDLs are not very low-level at all.

To examine what kind of language could be a good low-level language for an FPGA, we decided to start with examining the architecture of a specific FPGA (the Lattice ECP5). We took the ECP5 FPGA and forgot about every programming toolchain and from that perspective we designed a hypothetical toolchain from the ground up, balancing abstracting away cumbersome details of the FPGA architecture with preserving transparency.

The first step in the design of this hypothetical toolchain was an assembly-like language for the ECP5. In this language every LUT and register could be configured in as much detail as was available on the ECP5. This description of a design on an FPGA can be trivially compiled to a bitstream. This idea is indeed not new, Reticle [2] is such a language where the designer must specify the exact location and configuration of a tile on the FPGA. Their compilation speed is of course lightning fast: they make the designer specify so many details that no NP-hard problems need to be solved at all.

Building a large design in such a language is not productive as specifying the configuration and location of every tile by hand is a huge task. To obtain a productive language, language we started abstracting away details from that low-level language to provide productivity while maintaining transparency. This process of abstraction is what led to the current design of Ex-PART. These abstractions were made with attention to computational complexity of synthesis in mind, however this was a secondary goal. Sadly, in the current implementation of Ex-PART not much gains were made in synthesis speed in general. However, as discussed in the paper, Ex-PART's syntax and organization do open up avenues to synthesis strategies that may significantly speed up synthesis. See also Section 4.8 of this document.

# 4.2 Design Representation

Hardware description languages represent designs differently. Ex-PART must use a representation that is easily annotated with low-level directives. First we introduce how traditional HDLs and Clash represent their designs.

In Verilog and VHDL, a hierarchy of *modules* represents the hardware design. These modules define their inputs and outputs, and state is defined as registers belonging to that module. Inside the module combinational and sequential constructs can be applied to the input signals and state to define the output signals. Each module may instantiate other modules to create a hierarchy. In Clash one can lift pure Haskell functions to the domain of signals by using the functions moore and mealy to generate a Moore or Mealy machine from a specific type signature, or one can utilize the applicative functor instance of the Signal datatype to apply pure functions over signals. These structures allow powerful functional programming patterns to be used to describe hardware designs on many levels of abstraction.

For Ex-PART a limited version of a module representation is used. We view the hierarchy defining a hardware design as a tree of module instantiations. The leaves of this tree are all Mealy machines, and the nodes are groups of instantiations of predefined Mealy machines, or definitions of other submodules. This design is more limited than Verilog and VHDL as it only allows logic to be defined on the leaves of the tree, not in the nodes where only instantiations and connections between modules can be defined. This design representation also does not allow any of the powerful programming patterns Clash features. What this design *does* allow is clear places for placement annotations: the nodes and leaves of the tree. Furthermore, tree structures are easy to work with and implement, and enable such features as placement relative to parents.

Restricting logic to the leaves made implementation easier. Furthermore, this logic could have been represented differently, e.g. by a Moore machine or a set of processes. Mealy machines are used as they support both combinational and sequential hardware: To build a combinational circuit, leave out the state. To define memory elements, simply drive the value of the state unmodified to the output. Furthermore, it is easy to generate the definition of a mealy machine in Clash programmatically, making implementation of Ex-PART easier.

# 4.3 Separate Component Definitions and Instantiations

Designing hardware in an HDL consists of defining a hierarchy of modules, each operating on their inputs and state to produce an output. When that definition is ready, the design is synthesized. If synthesis succeeds in reasonable time, the design can be uploaded to an FPGA.

In Ex-PART, more control is given to the designer. With this control the designer can improve the chances that synthesis succeeds. This does add an extra phase in the design of hardware in Ex-PART. In the first phase of development the designer defines the modules themselves in the form of Mealy machines, this is quite similar to development in a traditional HDL. In the second phase the hierarchy and connections between those modules is defined and the components and hierarchies are laid out physically on the FPGA.

To explicitly show that these phases are separate concerns, they are performed in separate files. Component definitions are written in .expc (c for component) files, and hierarchies of instantiations in the .expi (i for instantiation) file.

## 4.4 Layout Expressions

The goal of Ex-PART is to allow a lower level of hardware descriptions, and specifically to provide language constructs to influence placement.

Some other work has been done in designing (embedded) languages with language constructs for placement. Wired [3] uses a relative system: components are laid out next to each other. Thereby allowing descriptions along the lines of "component a is below component b, component c is to the left of component a". Reticle [2] on the other hand uses a coordinate system. Elements of the system can be placed by the designer on an (x, y) coordinate.

To denote positions and sizes we chose to use a coordinate-based system, i.e. positions are denoted by an x and y value and sizes by a width and height value. With this system it is completely clear where a cell will be placed. Furthermore, this matches well with the tools as they also use a coordinate system for tiles on the ECP5 FPGA. Since coordinates are not easy to reason about for humans a visualizer is available. Having the visualizer in the design loop helps the designer verify their coordinate expressions. Another measure that makes defining placements easier is the fact that coordinates need not be expressed absolutely but can be denoted as an expression whose terms are other coordinates and sizes.

# 4.5 Component Shapes

In Ex-PART the designer is able to place a component in a certain area. The ideal shape of this area differs per component and it may also change when the component is connected to another component. For example, a component on its own may be best synthesized in a rectangular fashion, while when it is synthesized as a sub-component of a complicated hierarchy it may take on a more circular shape.

Synthesis tools usually generate standalone designs in a rectangular pattern, showing that any other shape usually is not necessary. Furthermore, we need to take into account that defining a shape in a text-based format is not human friendly. Allowing the definition of any shape would lead to much more syntactical noise causing confusion. Experience in designing in Ex-PART shows that a visualizer is necessary to efficiently work with defining rectangles using coordinates and sizes. These factors motivate the choice of limiting Ex-PART component shapes to rectangles.

Ex-PART allows overlap in component shapes. The exact consequences of overlapping components varies wildly per component and by the degree of overlap. To illustrate some of the consequences one may encounter we elaborate two examples.

Two components may not contain much logic but are connected via a high bit width connection. If one does not define areas for these two components that overlap, all the connections must go between the edge of the two areas that they share. This results in a complicated routing problem. To make the routing problem easier these components can be given a partly or fully overlapping area to be synthesized in. Now the placer can place the cells of both components in an interspersed fashion such that the routing problem becomes easier again.