# **Exploring Energy Efficient** DSP Design for an Audio ASIC

K.T. Raben, BSc

Faculty of Electrical Engineering, Mathematics and Computer Science Research Chair of Computer Architecture for Embedded Systems (CAES)

## **EXAMINATION COMMITTEE**

Committee Chairman: dr. ir. S.H. Gerez Daily Supervisor: H.H. Folmer, MSc External Member: dr. ir. A.B.J. Kokkeler

April 7<sup>th</sup> 2022

## **UNIVERSITY OF TWENTE.**

#### Abstract

With more and more consumer audio products becoming portable, maximizing battery lifetime has become extremely important. This drives the need for more energy-efficient Application Specific Integrated Circuits (ASIC) with a focus on audio. Often these chips have a Digital Signal Processor (DSP) section in their design to manipulate the audio signal before being amplified. Such a DSP typically implements various signal processing algorithms. This thesis explores how certain architectural choices influence the energy efficiency of such a DSP. A focus is laid on how the time-area trade off affects the energy consumption of a Finite Impulse Response (FIR) filter implementation. Through the use of Clash[1], a hardware description language with strong abstraction mechanisms, a method is presented where the amount of parallelism in a processor-like architecture can be controlled by one argument, creating a "knob" to generate designs which possess the same functionality but do so in a varying number of clock cycles. Through industry standard tools all the created designs are synthesized and the energy consumption is simulated. The energy efficiency of the processor designs generated with the variable parallelism are compared to a fully dedicated FIR filter implementation.

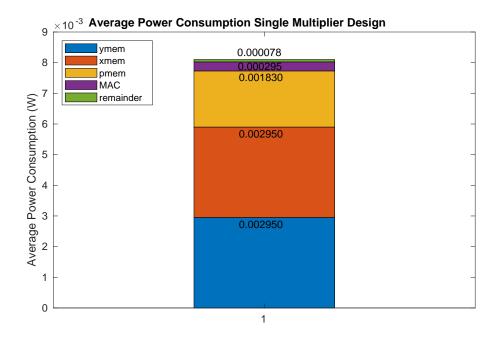

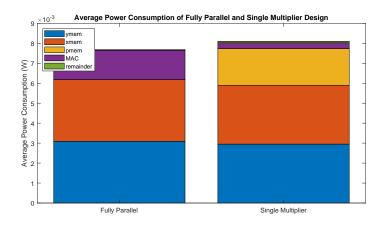

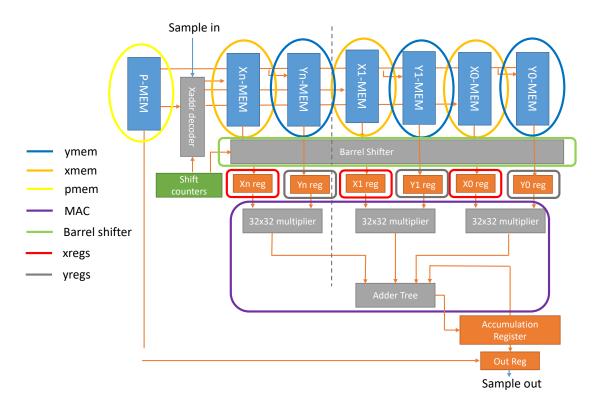

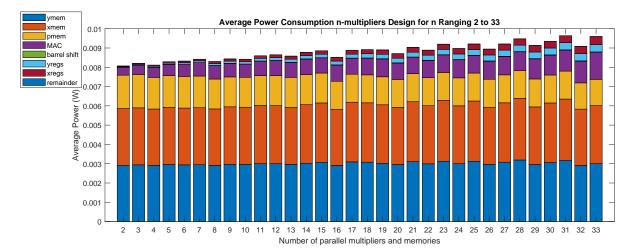

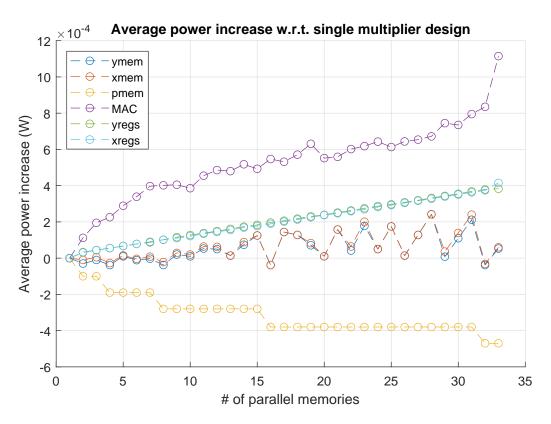

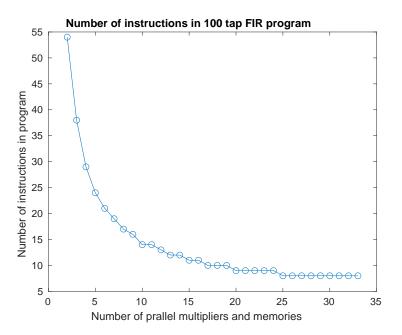

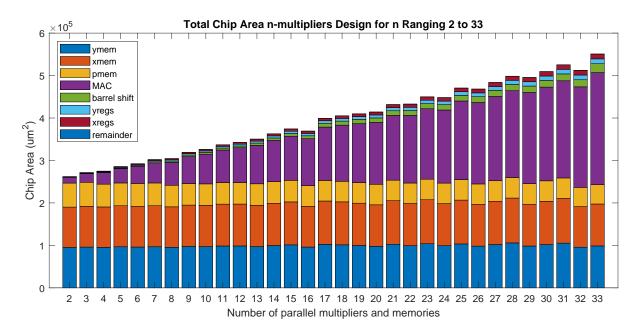

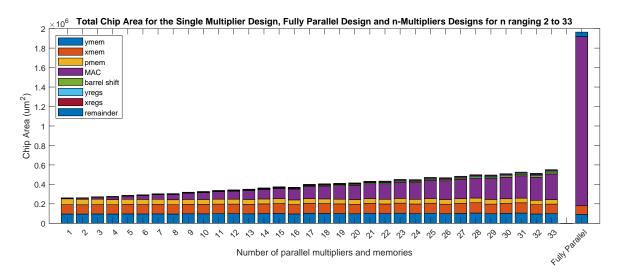

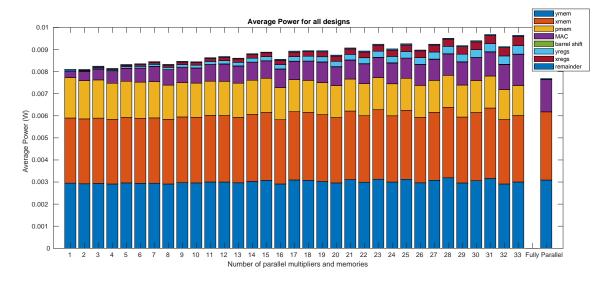

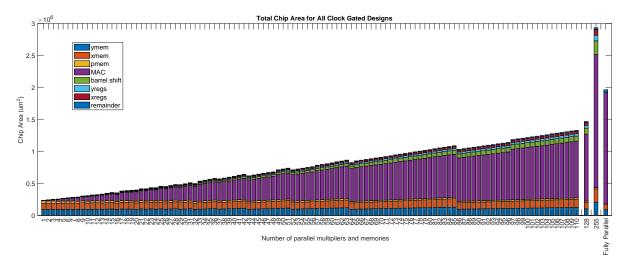

The results show that with a a fully parallel design a 85% reduction in energy consumption can be achieved with respect to a design with only a single multiplier, but at the cost of 8 times the chip area needed. By turning the "knob" results are obtained for designs with more than one multiplier, but less multipliers than the fully parallel design. From these results it can be seen that a significant decreases in energy consumption occur for small increases in number of multipliers. A design with 2 multipliers already reduces the energy consumption by 35%, while only increasing the chip area needed by 2%. The results also show however that further increasing the amount of multipliers does not always result in a decrease in energy consumption.

With obtaining the results it is also shown how the presented method can help an IC designer gain more insight in navigating the design space from an energy consumption perspective. Using the proposed method, the effect a specific architectural choice has on energy efficiency can be investigated.

## CONTENTS

| 1 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1        |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2 | Problem Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 2        |

|   | 2.1 DSP algorithms for audio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2        |

|   | 2.2 Implemented Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2        |

|   | 2.3 Time-area trade-off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2        |

|   | 2.4 Research Question                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2        |

| 3 | Energy Efficient Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3        |

| • | 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3        |

|   | 3.2 Energy Efficiency on a Circuit Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3        |

|   | 3.2.1 Voltage Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4        |

|   | 3.2.2 Reducing the Average Switched Capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 4        |

|   | 3.3 Energy Efficient Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4        |

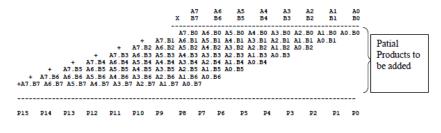

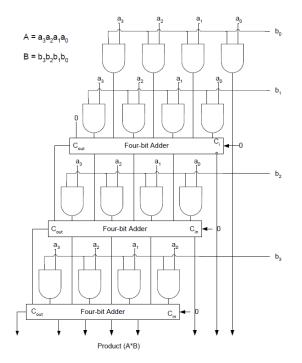

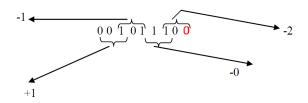

|   | 3.3.1 Partial Product Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4        |

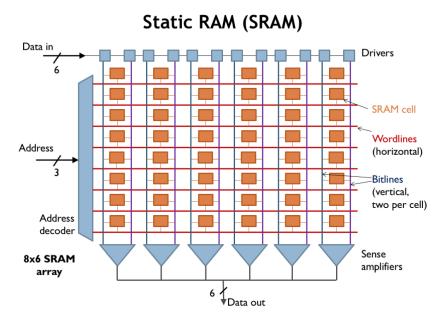

|   | 3.4 Power Analysis of Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6        |

|   | 3.5 Energy Efficiency on an Algorithmic Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7        |

|   | 3.6 Energy Efficiency on Architectural Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7        |

|   | 3.6.1 Spatial Locality                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7        |

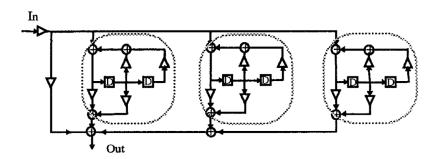

|   | 3.6.2 Regularity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8        |

|   | 3.7 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8        |

|   | EID Designs with different time area trade offe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9        |

| 4 | FIR Designs with different time-area trade-offs 4.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9<br>9   |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9<br>9   |

|   | 4.2         System Constraints         4.2.1         List of Constraints <td>9</td> | 9        |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9<br>10  |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10       |

|   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11<br>11 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12       |

|   | 5 1 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12<br>13 |

|   | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18<br>10 |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18       |

|   | 0 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19       |

|   | 4.5.3 Hardware Description of n Multiplier Designs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20       |

| 5 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 26       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 26       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27       |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 27       |

|   | 5.4 Samples, Coefficients, Programs and Expected Output Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28       |

|    | 5.6 Tool Overview                                                                                                                                                                                                                                                                                                                                                                                                                   | 28<br>28<br>28                                                                          |  |  |  |  |  |  |  |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

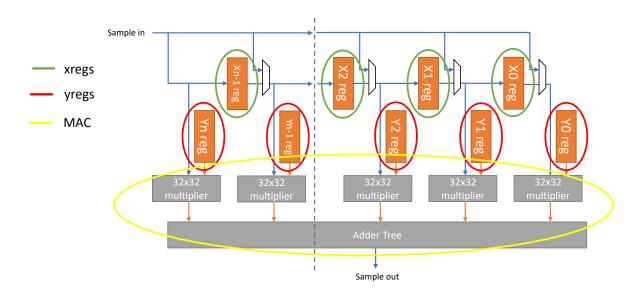

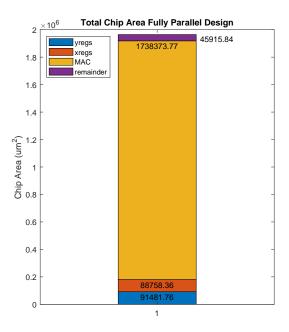

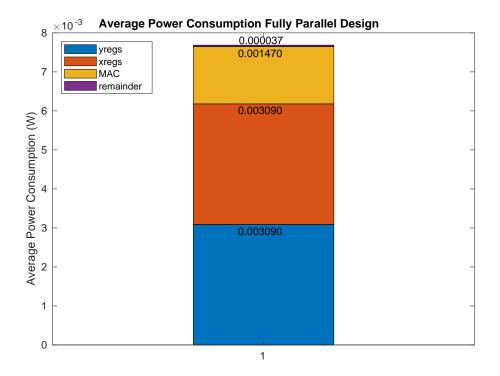

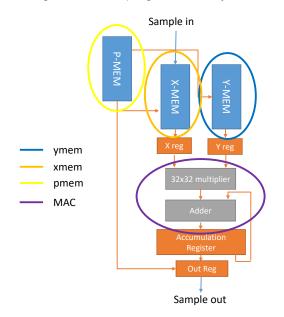

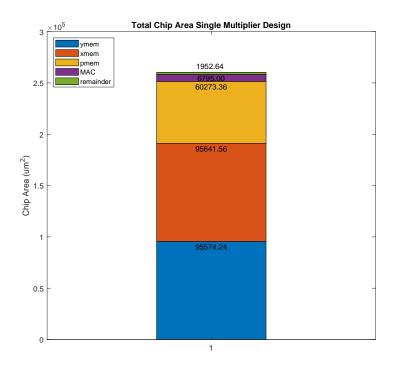

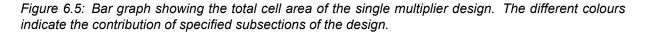

| 6  | 6.1       Fully Parallel Design       3         6.2       Single Multiplier Design       3         6.3       Comparison Fully Parallel - Single Multiplier       3         6.4       N Multiplier Design       3         6.5       Comparison of Sinlge Multiplier, N-Multiplier and Fully Parallel Designs       3         6.6       Clock Gating       3         6.7       Results Clock Gated Designs       3                    | <b>30</b><br>32<br>33<br>34<br>38<br>39<br>39                                           |  |  |  |  |  |  |  |

| 7  | Conclusion 4                                                                                                                                                                                                                                                                                                                                                                                                                        | 14                                                                                      |  |  |  |  |  |  |  |

| 8  | Discussion and Future Work 4                                                                                                                                                                                                                                                                                                                                                                                                        | 15                                                                                      |  |  |  |  |  |  |  |

| Re | References                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                         |  |  |  |  |  |  |  |

| A  | A.1 Fully Parallel Design       4         A.1.1 Data Types       4         A.1.2 Design and Testbench       4         A.2 Single Multiplier Design       5         A.2.1 Data Types       5         A.2.2 Design and Testbench       5         A.2.1 Data Types       5         A.2.2 Design and Testbench       5         A.3.1 Data Types       5         A.3.1 Data Types       5         A.3.2 Top Design and Testbench       5 | <b>19</b><br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19<br>19 |  |  |  |  |  |  |  |

| В  | B.1 SRAM Primitive                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>53</b><br>53<br>53                                                                   |  |  |  |  |  |  |  |

| С  | C.1       Matlab Stimuli Generation and Program Compiler                                                                                                                                                                                                                                                                                                                                                                            | <b>55</b><br>55<br>58<br>58<br>70                                                       |  |  |  |  |  |  |  |

| D  | D.1 Designs without Clock Gating                                                                                                                                                                                                                                                                                                                                                                                                    | <b>74</b><br>74<br>75                                                                   |  |  |  |  |  |  |  |

## 1 INTRODUCTION

With the increase in popularity of wireless headphones and true wireless in-ear monitors there comes a drive to create audio products that can function a long time on small batteries. To achieve this long battery lifetime the energy consumption of the product must be brought down. This requirement results in a desire for audio ICs with low energy consumption.

In audio IC's, before a bitstream is converted to an analog signal, a manipulation of the stream is often desired. High-performance audio ICs typically have specific digital hardware to handle a set of possible manipulations. This hardware is required to be fast enough to handle the data-rates but should also possess the flexibility such that it can be configured to perform several different signal processing functions. Flexible hardware that serves such a purpose is called a Digital Signal Processor (DSP). It lies between a traditional processor and dedicated hardware in terms of performance, energy efficiency and programmability.

The DSP section of the chip can have a large impact on this total energy consumption and should therefore be designed with energy efficiency in mind. In designing this flexible hardware many architectural choices have to be made which all have an influence on the total energy consumption of the hardware. Gaining insight into the exact influence of a specific architectural choice is however a difficult task. This work delves into the aspects of what makes an energy efficient DSP design and proposes a method to easily make high-level architectural choices and observe the effect this choice has on energy efficiency.

In particular, this work investigates the architectural choice of how many calculations are done simultaneously and how that influences the energy efficiency of a DSP design. By using the proposed method, more exact measurements can be made of how much efficiency is gained by performing more calculations at the same time and what the costs are in terms of chip area needed. This information can guide the IC designer in creating an efficient, cost-effective hardware design.

#### **Collaboration with Axign**

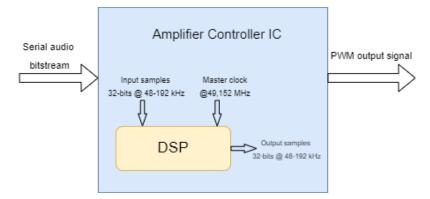

This work is developed in collaboration with Axign, a fabless semiconductor company from Enschede. Axign develops state-of-the-art class-D audio amplifier controllers. For future products, Axign would like to include a energy efficient DSP as part of their amplifier controller IC.

#### **Thesis Layout**

The structure of this thesis is as follows: First, in chapter 2 the global research topic of energy efficient DSP design will be refined in a concrete research question. Chapter 3 will elaborate on the theory involved in creating energy efficient digital hardware. Keeping this knowledge in mind a method of creating multiple design architectures is presented in chapter 4. For each design, the energy consumption is determined through the method described in chapter 5. An overview of the results for the different designs is given in chapter 6, after which a conclusion is presented in chapter 7.

## 2 PROBLEM DEFINITION

#### 2.1 DSP algorithms for audio

The functionalities that an audio DSP should support naturally differ for each product, but common functions are: Channel mixing, volume control, equalization, and interpolation/decimation of signals. Most of the above-mentioned functionality is some combination of multiplication and addition of a set of (delayed) samples. The algorithms behind many of these implementations are often Finite Impulse Response (FIR) filters, Infinite Impulse Response (IIR) filters, a Least Mean Squares (LMS) calculation, or the Fast Fourier Transform (FFT).

### 2.2 Implemented Algorithm

To limit the design space that needs to be explored this research is narrowed down to a single algorithm to be implemented. Of the algorithms mentioned in section 2.1, the FIR algorithm can be used to perform, among other things, interpolation, decimation, and equalization. With respect to the IIR algorithm it is less complex, as it is a system without feedback. The FFT and LMS algorithms are less often used. For these reasons, the research focuses on creating an FIR filter implementation.

#### 2.3 Time-area trade-off

To further limit the scope, the question is approached from a digital IC architecture perspective. All DSP algorithms mentioned above are dominated by multiplier operations and memory access [2]. Therefore this research will mainly revolve around the chosen structure of digital building blocks that implement these operations, such as memory elements, multipliers and adders. For a FIR implementation changing the number and structure of memory elements and multipliers results in varying the time-area trade-off. Designs with a different time-area trade-off will take a different number of clock cycles to finish the operation and can be implemented with a different amount of chip area. This thesis focuses on how that trade-off affects energy efficiency.

#### 2.4 Research Question

After constraining the larger question of how to design an energy efficient DSP the following research question is formed:

"How does the time-area trade-off affect the energy efficiency of a streaming FIR filter ASIC implementation for audio purposes?"

## **3 ENERGY EFFICIENT DESIGN**

#### 3.1 Introduction

Energy efficient design can be approached from many different levels of abstraction. The total energyefficiency will depend on the choices made on all levels. But especially on how well the different levels are attuned to each other. For instance, circuit level analysis may give insight into how the power consumption of memory access is in proportion to that of a multiplier. This information can be used to find a good combination of an algorithm and an architecture that can optimize for multiplications and memory access in an energy-efficient manner.

This chapter will discuss the different levels mentioned above in more detail. The relevant aspects that need to be considered in the DSP design are elaborated upon and aspects that fall outside of this research scope are addressed.

#### 3.2 Energy Efficiency on a Circuit Level

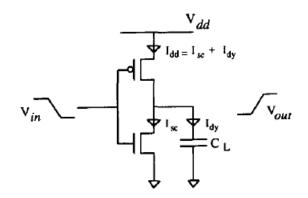

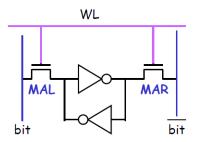

At the basis of digital CMOS circuitry lies the inverter shown in Figure 3.1. There are three major sources of power dissipation in these circuits: A switching component  $P_s$ , a short-circuit component  $P_{sc}$  and a leakage component  $P_l$ . Equation 3.1 gives a description of these sources of dissipation[3].

Figure 3.1: CMOS circuitry for digital inverter [4]

$$P_{\text{total}} = P_s + P_{sc} + P_l$$

=  $p_t \left( C_L \cdot V_{dd}^2 \cdot f_{\text{clk}} \right) + I_{sc} \cdot V_{dd} + I_{\text{leakage}} \cdot V_{dd}$  (3.1)

Here  $I_{leakage}$  is the leakage current and mostly dependent on the chip process technology[5].  $I_{sc}$  is the short-circuit current that occurs when switching.  $C_L$  is the load capacitance that needs to be driven.  $p_t$  is the probability of a switch occurring between zero to one or vice versa.

For modern CMOS technologies, the contributions of  $P_l$  and  $P_{sc}$  are generally well below that of  $P_s$ [5][6][7]. Therefore, the focus of this work is mainly laid on the switching power dissipation.

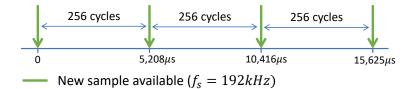

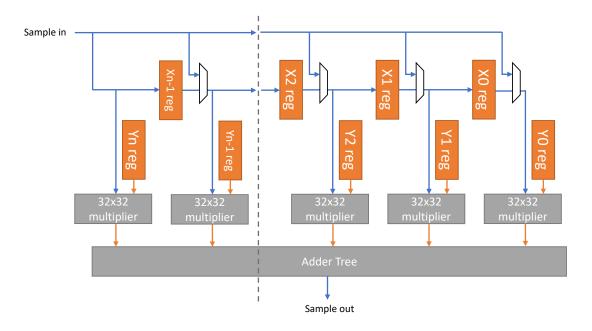

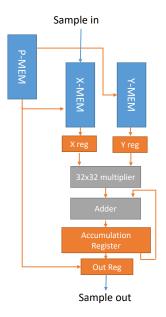

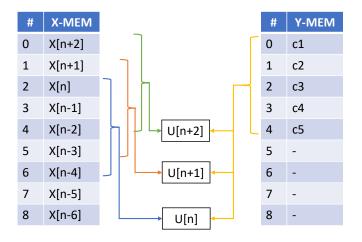

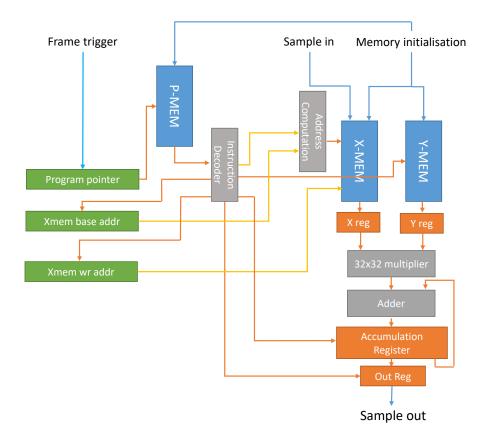

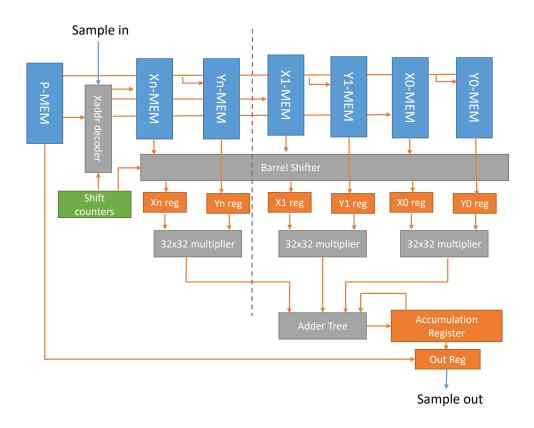

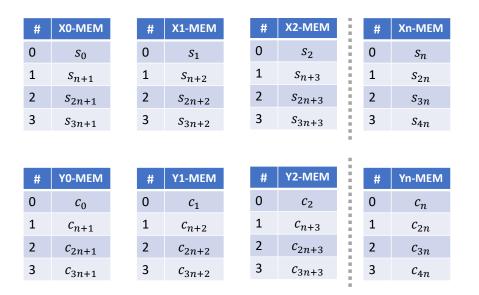

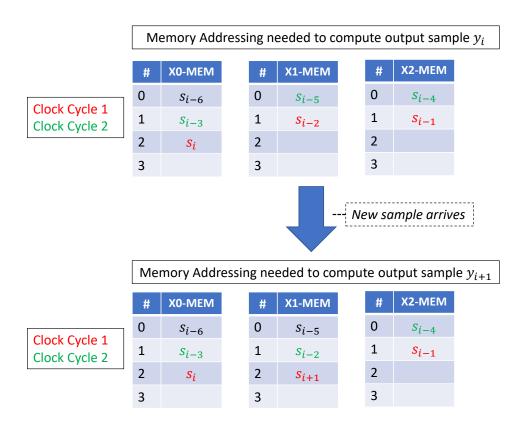

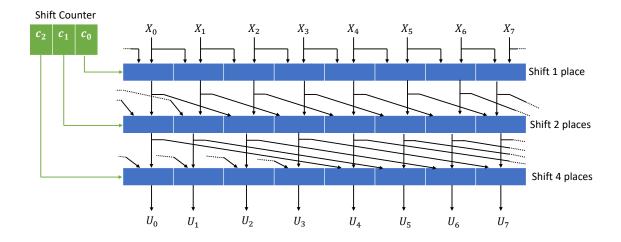

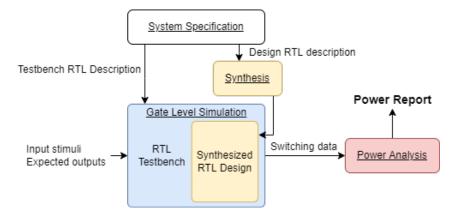

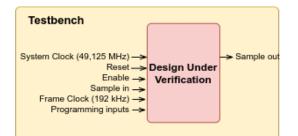

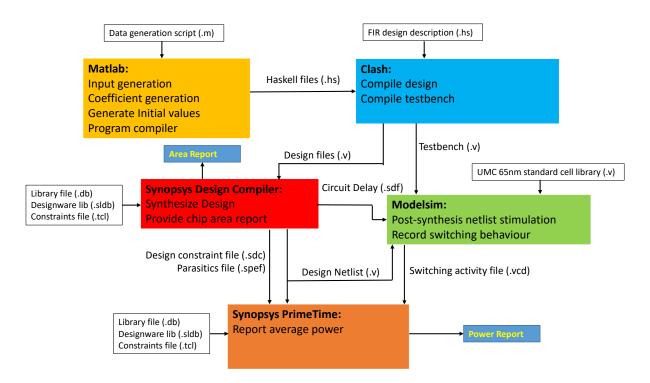

### 3.2.1 Voltage Scaling