# UNIVERSITY OF TWENTE.

Faculty of Electrical Engineering, Mathematics & Computer Science

# A Tunable Accelerator for the YOLOv4-tiny Object Detector using Vitis Unified Software Platform

Sridhar Balamurali MSc. Thesis May 2023

> Supervisors dr. ir. S.H. Gerez dr. ir. N. Alachiotis dr. C.G. Zeinstra

Computer Architectures and Embedded Systems Group

Faculty of Electrical Engineering, University of Twente P.O. Box 217 7500 AE Enschede The Netherlands

# Abstract

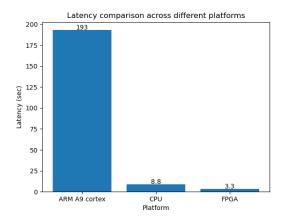

Deep learning-based object detection plays a crucial role in various computer vision applications. However, deploying these complex networks on embedded systems that have limited resources presents significant challenges. This thesis addresses these challenges by developing a unified and tunable FPGA accelerator, drawing inspiration from an existing architecture [1]. The accelerator is designed to optimize the performance of not only the computationally intensive convolutional layers but also other non-convolutional layers in the YOLOv4-tiny model. To achieve this, Vivado HLS is utilized to create IPs with design parameters that allow for tuning through parallelism control. Key optimizations, such as fixed-point quantization and channel interleaving, are employed. The Vitis unified software platform is utilized to dynamically configure the layers of YOLOv4-tiny within the processing system of the ZedBoard. The proposed accelerator achieves a significant speedup, with the convolutional layers running 20 times faster compared to previous works on the same platform with a MACC operation taking 2 clock cycles inside the convolution block with a throughput of 5.84 GOPS/secs, resulting in an inference rate of 3.3 seconds per image. The overall architecture achieves a throughput of 2.05 GOPS/sec with resource utilization of 166 (76%) DSP units, 149 (53%) BRAM18K blocks, LUT, and FF utilization of about 56% and 43% respectively. Furthermore, when compared with the ARM A9 processor on the ZedBoard and host CPU implementation, the implemented architecture demonstrates a speed improvement of 58x, and 3x respectively.

# Contents

| AI | Abstract |                                                          |    |  |  |  |  |  |

|----|----------|----------------------------------------------------------|----|--|--|--|--|--|

| Li | st of    | acronyms                                                 | vi |  |  |  |  |  |

| 1  | Intr     | oduction                                                 | 1  |  |  |  |  |  |

|    | 1.1      | Problem statement and System Setup                       | 2  |  |  |  |  |  |

|    | 1.2      | Research Questions                                       | 3  |  |  |  |  |  |

|    | 1.3      | Contribution                                             | 4  |  |  |  |  |  |

|    | 1.4      | Thesis Outline                                           | 4  |  |  |  |  |  |

| 2  | CN       | N Background                                             | 6  |  |  |  |  |  |

|    | 2.1      | Convolutional Neural Network                             | 6  |  |  |  |  |  |

|    |          | 2.1.1 Convolutional Layer                                | 6  |  |  |  |  |  |

|    |          | 2.1.2 Other Typical Layer Types                          | 7  |  |  |  |  |  |

|    |          | 2.1.3 Evaluation Metrics                                 | 9  |  |  |  |  |  |

|    |          | 2.1.4 Dataset                                            | 11 |  |  |  |  |  |

|    |          | 2.1.5 Frameworks                                         | 12 |  |  |  |  |  |

|    | 2.2      | YOLO: Real-Time object detection algorithm               | 13 |  |  |  |  |  |

|    | 2.3      | Motivation For choosing YOLOv4-tiny                      | 15 |  |  |  |  |  |

|    |          | 2.3.1 Theorectical upper bound performance:              | 15 |  |  |  |  |  |

|    | 2.4      | YOLOv4-tiny                                              | 17 |  |  |  |  |  |

| 3  | Lite     | rature Review                                            | 21 |  |  |  |  |  |

|    | 3.1      | 2-D Convolution on FPGA                                  | 21 |  |  |  |  |  |

|    | 3.2      | Fixed-point Quantization                                 | 22 |  |  |  |  |  |

|    | 3.3      | Dynamically Configurable Architecture                    | 22 |  |  |  |  |  |

|    | 3.4      | Related Work on YOLO                                     | 23 |  |  |  |  |  |

| 4  | Rele     | evant Tool: Vitis Unified Software Platform & Vivado HLS | 26 |  |  |  |  |  |

|    | 4.1      | WorkFlow Used For Creating Accelerated Application       | 26 |  |  |  |  |  |

|    | 4.2      | Data types                                               | 27 |  |  |  |  |  |

|    | 4.3      | HLS Stream Library                                       | 28 |  |  |  |  |  |

|    |          | 4.3.1 Using HLS stream                                   | 29 |  |  |  |  |  |

|    |          | 4.3.2 Naming streams                                     | 29 |  |  |  |  |  |

|   |      | 4.3.3 I/O for streams $\ldots \ldots 29$ |

|---|------|----------------------------------------------------------------------------------------------------------------|

|   |      | 4.3.4 Blocking reads and writes                                                                                |

|   |      | 4.3.5 Non-Blocking reads and writes                                                                            |

|   | 4.4  | Source code Example                                                                                            |

|   |      | 4.4.1 Pragmas and performance improvement                                                                      |

|   |      | 4.4.2 Resource utilization comparision                                                                         |

| 5 | Soft | tware Implementation of YOLOv4-tiny on Zedboard's PS and Host CPU 39                                           |

|   | 5.1  | Software Implementation                                                                                        |

|   |      | 5.1.1 Yolov4-tiny Baremetal Floating-point model                                                               |

|   | 5.2  | Profiling results for yolov4-tiny on Host CPU                                                                  |

|   | 5.3  | Vitis Vivado setup and profiling results of yolov4-tiny model on ZedBoard PS 46                                |

|   | 5.4  | Yolov4-tiny Fixed-point Model                                                                                  |

| 6 | Har  | dware IP Block Design 53                                                                                       |

| Ŭ | 6.1  | Motivation for using unified hardware architecture                                                             |

|   | 6.2  | Convolutional Layer IP                                                                                         |

|   | 0    | 6.2.1 Convolutional IP block design                                                                            |

|   |      | 6.2.2 Tunable Line Buffer                                                                                      |

|   |      | 6.2.3 3x3 Sliding Window                                                                                       |

|   |      | 6.2.4 Multiply Accumulate batch units                                                                          |

|   |      | 6.2.5 Output stream merge                                                                                      |

|   |      | 6.2.6 Optimisation                                                                                             |

|   |      | 6.2.7 Architecture of the convolutional IP                                                                     |

|   |      | 6.2.8 Latency Estimation of Convolutional IP block                                                             |

|   | 6.3  | Accumulation & Activation IP block                                                                             |

|   |      | 6.3.1 Latency estimation of Accumulation block                                                                 |

|   | 6.4  | Max Pooling Layer IP block                                                                                     |

|   |      | 6.4.1 Latency estimate of Maxpool Layer                                                                        |

|   | 6.5  | Upsample Layer IP block                                                                                        |

|   |      | 6.5.1 Latency estimation of upsample layer                                                                     |

|   | 6.6  | Yolo Layer                                                                                                     |

|   |      | 6.6.1 Latency estimation of Yolo IP block                                                                      |

| 7 | Syst | tem Design 77                                                                                                  |

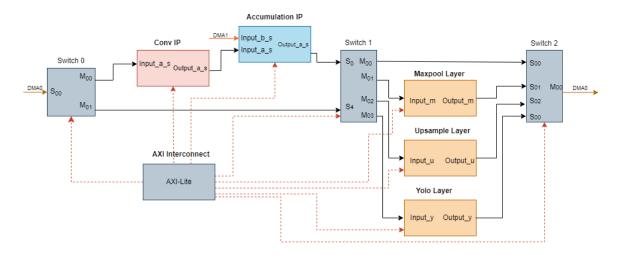

|   | 7.1  | System Overview                                                                                                |

|   | 7.2  | Network Shaping                                                                                                |

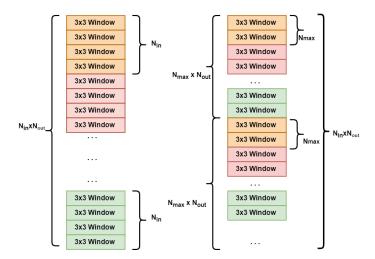

|   |      | 7.2.1 Channel Folding 78                                                                                       |

|   |      | 7.2.2 Channel Padding and Kernel size padding                                                                  |

|   | 7.3  | Hardware Accelerator Block setup                                                                               |

|   | 7.4  | Processing System (PS) Design 82                                                                               |

|   |      | 7.4.1 Software Driver for ARM A9 Cortex Processor                                                              |

|   |      | 7.4.2 Weights rearrangement for channel folding                                                                |

|    |        | 7.4.3                            | Memory Access                                                        | 83  |  |  |  |  |

|----|--------|----------------------------------|----------------------------------------------------------------------|-----|--|--|--|--|

|    |        | 7.4.4                            | Input Image transformation                                           | 84  |  |  |  |  |

|    |        | 7.4.5                            | Route Layer Implementation                                           | 84  |  |  |  |  |

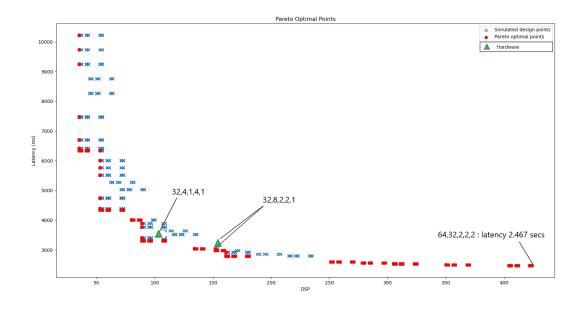

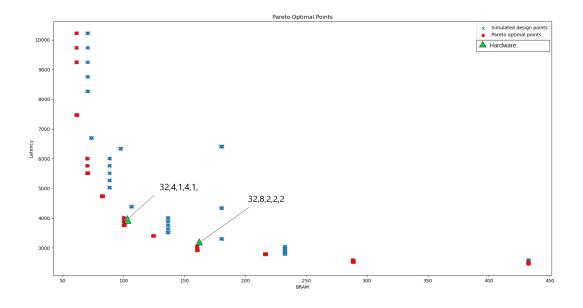

|    | 7.5    | Design                           | 1 Space exploration                                                  | 84  |  |  |  |  |

| 8  | Res    | ults                             |                                                                      | 87  |  |  |  |  |

|    | 8.1    | Specif                           | ications of the target platform                                      | 87  |  |  |  |  |

|    |        | 8.1.1                            | Intel Core i5-8250U CPU                                              | 87  |  |  |  |  |

|    |        | 8.1.2                            | ZedBoard                                                             | 88  |  |  |  |  |

|    | 8.2    | Unifie                           | d accelerator Configurations                                         | 88  |  |  |  |  |

|    | 8.3    | Layer-                           | wise performance comparision                                         | 90  |  |  |  |  |

|    |        | 8.3.1                            | Performance breakdown per convolutional layer: PS only configuration | 90  |  |  |  |  |

|    |        | 8.3.2                            | Performance Breakdown per convolutional Layer: PS+PL Only Con-       |     |  |  |  |  |

|    |        |                                  | figuration                                                           | 91  |  |  |  |  |

|    |        | 8.3.3                            | Performance Improvement in Setup 2                                   | 92  |  |  |  |  |

|    |        | 8.3.4                            | Performance difference in this work vs Ref $[1]$                     | 92  |  |  |  |  |

|    | 8.4    | Resou                            | rce Utilization Breakdown                                            | 94  |  |  |  |  |

|    |        | 8.4.1                            | Resouce Utilization Breakdown: setup 1                               | 94  |  |  |  |  |

|    |        | 8.4.2                            | Resource Utilization Breakdown: setup 2                              | 97  |  |  |  |  |

|    | 8.5    | Platfo                           | rm Comparison                                                        | 97  |  |  |  |  |

|    | 8.6    | Speed                            | and Resource Efficiency                                              | 98  |  |  |  |  |

|    | 8.7    | Power                            | and Energy Efficiency                                                | 99  |  |  |  |  |

|    | 8.8    | Comp                             | arison with CPU and FPGA                                             | 100 |  |  |  |  |

| 9  | Con    | onclusion and Recommendations 10 |                                                                      |     |  |  |  |  |

|    | 9.1    | Resear                           | rch subquestions                                                     | 102 |  |  |  |  |

|    | 9.2    | Main                             | research question                                                    | 105 |  |  |  |  |

|    | 9.3    | Recon                            | nmendations                                                          | 106 |  |  |  |  |

|    |        | 9.3.1                            | Testing on different Xilinx-based platforms                          | 106 |  |  |  |  |

|    |        | 9.3.2                            | Reduced bit-width implementation                                     | 106 |  |  |  |  |

|    |        | 9.3.3                            | Non-uniform channel interleaving                                     | 107 |  |  |  |  |

| Re | eferen | ices                             |                                                                      | 108 |  |  |  |  |

| Ar | opend  | lices                            |                                                                      |     |  |  |  |  |

| Α  | Yolo   | ov4-tiny                         | / Details                                                            | 112 |  |  |  |  |

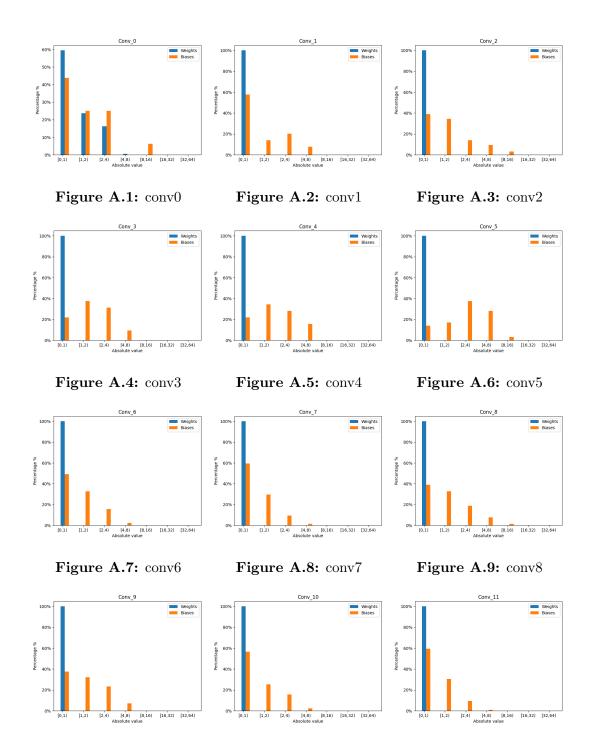

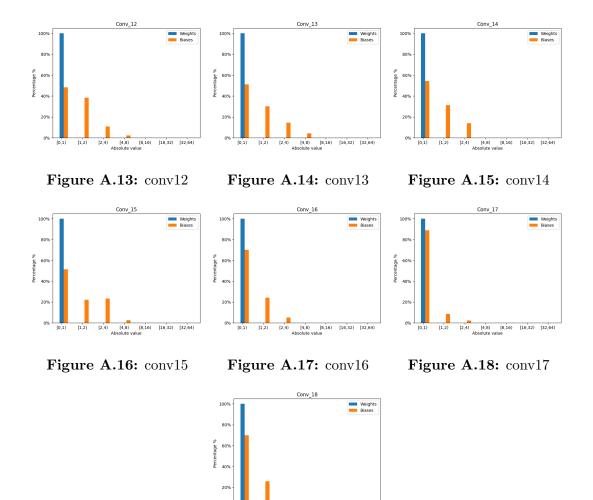

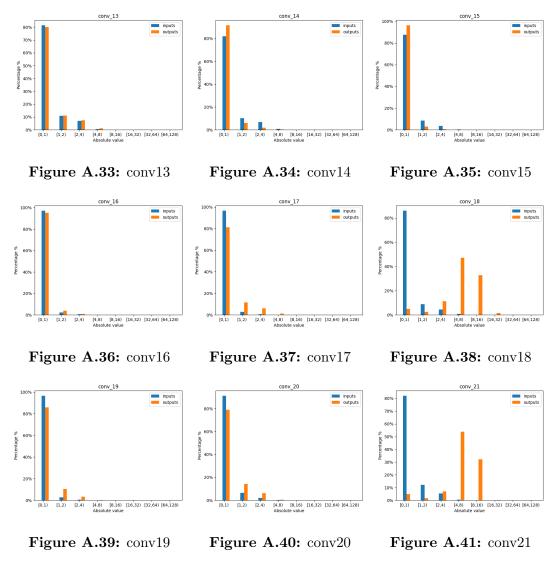

|    |        |                                  | t Distribution of yolov4-tiny                                        | 113 |  |  |  |  |

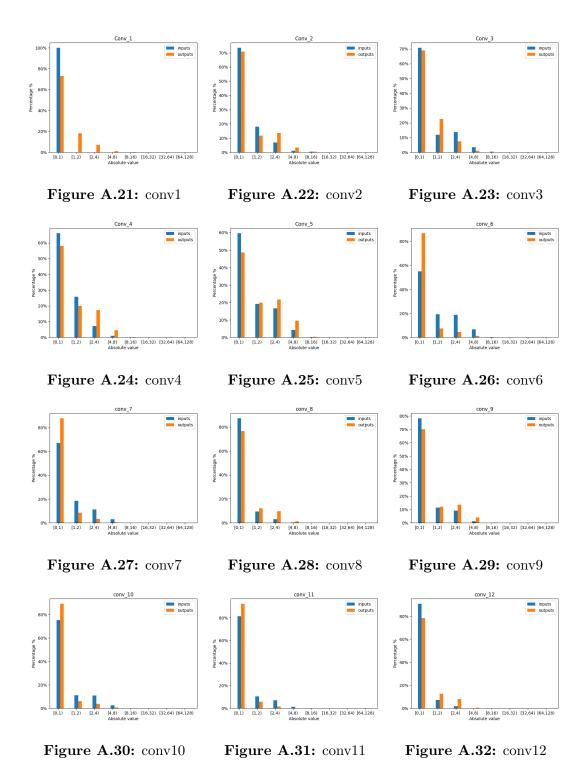

|    | A.2    | -                                | Distribution of yolov4-tiny                                          | 115 |  |  |  |  |

|    | A.3    |                                  | n Results                                                            | 117 |  |  |  |  |

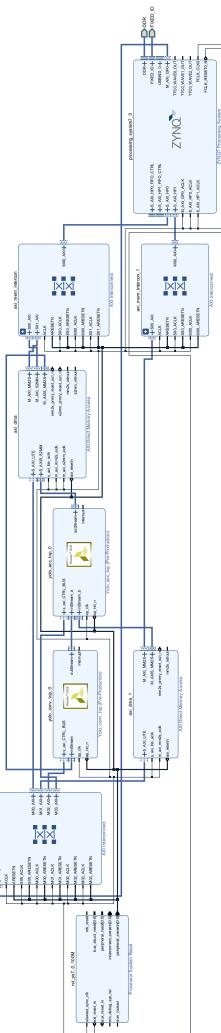

|    |        | A.3.1                            | Setup 1                                                              | 117 |  |  |  |  |

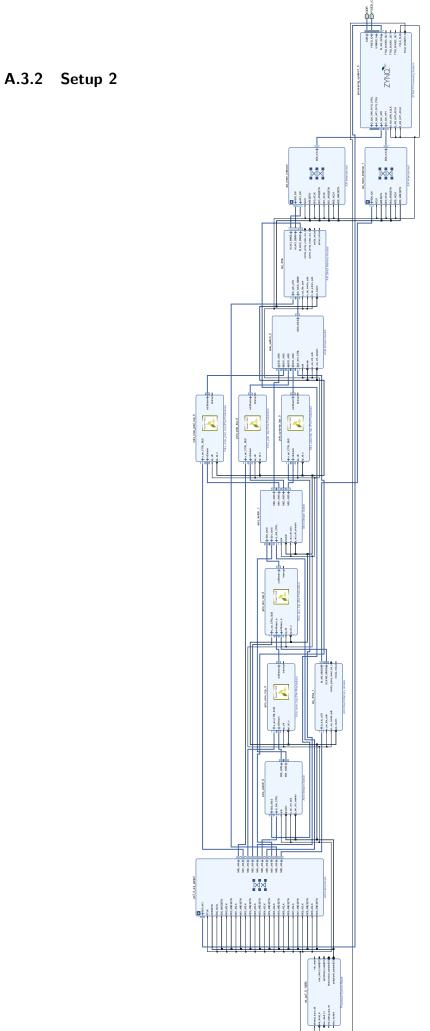

|    |        | A.3.2                            | Setup 2                                                              | 118 |  |  |  |  |

V

# List of acronyms

| DNN   | Deep Neural Network            |

|-------|--------------------------------|

| YOLO  | You Only Look Once             |

| GPUs  | Graphics Processing units      |

| FPGAs | Field Programmable Gate Arrays |

| loU   | Intersection over Union        |

| FPS   | Frame Per Seconds              |

| PE    | Processing Element             |

| PS    | Processing System              |

| PL    | Programmable Logic             |

| PL    | Programmable Logic             |

| MACC  | Multiply and Accumulate        |

| mAP   | Mean Average Precision         |

| CNN   | Convolutional Neural Network   |

| COCO  | Commom Objects in Context      |

| HLS   | High Level Synthesis           |

| RTL   | Register Transfer Level        |

| ReLU  | Rectified Linear Unit          |

| AXI   | Advanced eXtensible Interface  |

| IP    | Intellctual Property           |

| TFLM  | TensorFlow Lite Micro          |

| SPP   | Spatial Pyramid Pooling        |

# Chapter 1

# Introduction

In today's information age, image processing is a crucial technology that enables electronic systems to perceive, analyze, and manipulate the world. Traditional image processing techniques primarily rely on mathematical algorithms or feature descriptors [2]. However, since the early 2000s, there has been a growing interest in bio-inspired deep neural network (Deep Neural Network (DNN)) applications. These DNNs have become increasingly popular due to their ability to learn complex patterns and features from large datasets, leading to superior performance in various image-processing tasks.

In the present day, computer vision is a dynamic area of research that is producing impressive outcomes. An extensively employed task in computer vision is the detection of objects. This task facilitates systems to identify and categorize objects within images. Conventional object detection methods relied on manually crafted feature extractors, but they have been surpassed by deep learning techniques [3] [4]. One of these approaches that have achieved real-time performance in object detection is the You Only Look Once (YOLO) (You Only Look Once) detector, which was introduced in 2016 [5]. YOLO provides a novel method where image pixels are used to predict object locations and corresponding classes. Earlier techniques utilized complex pipelines that were difficult to optimize and performed relatively poorly. Numerous versions of YOLO have been released over the years, but this work employs the most recent scientifically validated version, which is YOLOv4-tiny [6].

The primary difficulty with DNNs like You Only Look Once (YOLOv4-tiny) is their prolonged computational time, which necessitates high-processing-capability platforms. Generally, greater computational ability results in increased power consumption. Graphics Processing units (GPUs) and large-scale cloud servers are typical examples of such platforms.

Researchers are exploring balancing performance and power consumption for deploying neural networks in embedded applications. Field Programmable Gate Arrays (FPGAs) have shown promise as a platform for this purpose, as they can be hardware reconfigured to enable flexible parallelism [7]. Additionally, many hardware acceleration techniques make FPGAs suitable for energy-efficient scenarios. These include utilizing specialized hardware blocks, such as DSPs and BRAMs, to accelerate computation, as well as optimizing memory usage with techniques like data folding and line buffering. Overall, FPGAs offer a potential solution to the challenge of deploying DNNs in embedded applications with limited resources.

In recent times, there has been a surge of network architectures that are highly efficient in object detection, which have the potential to advance the development of intelligent systems. However, implementing these networks on FPGA poses a considerable challenge due to their large scale. Moreover, it is highly desirable to have a tunable FPGA implementation available for these complex networks. By providing a tunable design, different design decisions can be made to cater to the varying requirements of different applications without having to start the system design process from scratch repeatedly.

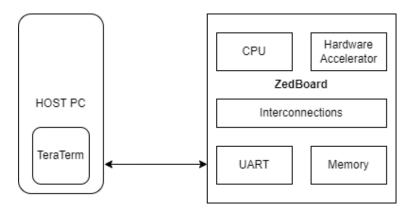

### 1.1 Problem statement and System Setup

The goal of this thesis is to develop a tunable YOLOv4-tiny FPGA implementation targetting resource-constrained devices like Zedboard, which is an ARM/FPGA Soc development board. There have been recent works that accelerate the YOLOv4-tiny object detection algorithm. A Convolutional Neural Network (CNN) accelerator for YOLOv4-tiny integrated with TensorFlow lite framework (TensorFlow Lite Micro (TFLM)) has been implemented using a Catapult high-level synthesis tool in order to realize real-time performance [8]. An accelerator was developed for FPGA to increase the throughput for the convolutional layers of YOLOv4-tiny to improve upon the DSP utilization of the design [9]. Both designs used Catapult C for High-level synthesis.

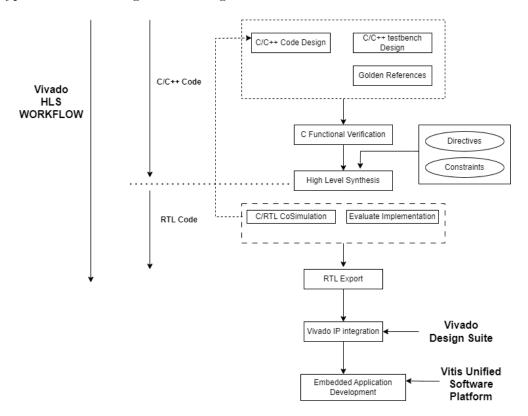

Catapult can be a useful tool for accelerating FPGA design but it has some limitations too [10]. Catapult does not provide the level of control and optimization that is available in traditional RTL design flow provided by Xilinx tools such as Vivado. This makes it less suitable for designs that require fine-grained optimization and control over the hardware implementation. This fine-grained optimization is required when making the design more tunable. Moreover, Catapult offers limited support for the AXI interface, which makes it difficult to interface with other Intellctual Property (IP) blocks or to implement complex data transfer between the processing system and the programmable logic blocks inside FPGA. Therefore for this project Xilinx tool such as Vivado HLS is used to implement IP blocks. These IP blocks are integrated using the Vivado designer suite. Finally, Vitis unified software platform is used for creating hardware software codesign implementation. Further details regarding how Vivado HLS can be utilized to create Advanced eXtensible Interface (AXI) interfaces and how other directives can be utilized to improve the performance of the accelerator is discussed in chapter 4.

A bare-metal application without a camera is chosen for this implementation because it eliminates the need for an extra operating system, which results in lower overhead and better system performance. Additionally, it provides greater control over hardware resources, leading to more efficient utilization of available resources. Finally, the use of bare-metal implementation enables greater customization and flexibility in terms of hardware-software integration, allowing the system to be adapted to specific needs. Images are firstly pre-processed on the host PC. Pre-processing involves the following steps:

- 1. Image resizing

- 2. Letterboxing the image.

- 3. Channel Interleaving.

Figure 1.1: System Overview for YOLOv4-tiny Algorithm Processing [8]

These pre-processed images are fed to the accelerator architecture running on the FPGA programmable logic. The Zedboard outputs bounding box coordinates and class predictions along with their accuracy, which is then relayed back to the host PC through the UART interface and displayed on a serial terminal called "Tera Term".

### 1.2 Research Questions

How can a tuneable FPGA design be created for the deep-learning object detector YOLOv4tiny with possible opportunity for carrying out design space exploration?

To answer this main research question, the following research subquestions need to be answered:

- How can a YOLOv4-tiny be optimized at the software level before hardware accelerating the model?

- What are the design decisions that are taken to accelerate the YOLOv4-tiny model?

- How can an FPGA design for YOLOv4-tiny be made parameterisable? Given the parameters what values are optimal?

- How can a YOLOv4-tiny accelerator be created using the Vitis unified software platform?

• Can a design space exploration be carried out for the YOLOv4-tiny model to find optimal design points which reach low latency with as few resources as possible?

# 1.3 Contribution

The primary aim of this thesis, as stated in the central research question, is to develop a flexible FPGA design for YOLOv4-tiny using the Vitis Unified Software Platform on limited-resource devices. However, this is not the only contribution of this work. The main contribution of this thesis has been listed below.

- Bare-metal software applications, capable of running on resource-limited platforms like Zedboard, have been developed by integrating the Darknet framework with both floating and fixed-point operations. These applications serve as a foundation for executing neural networks on a single-core processor

- An FPGA implementation of the YOLOv4-tiny neural network, implemented through Xilinx HLS tools is provided. The FPGA hardware IPs are utilized as a dedicated CNN accelerator. Fixed-point quantization and channel interleaving techniques have been employed to enhance acceleration performance, taking into account the network topology and data analysis.

- The presented work proposes a dynamic and configurable architecture, capable of computing all layers in the YOLOv4-tiny neural network without the need for bitstream reconfiguration. The technique utilized is known as network transformation, which involves reshaping the original network structure to be compatible with the accelerator. This approach facilitates efficient computation of the neural network on FPGA hardware.

The distinction between *design parameters* and *typology parameters* is important in the context of hardware design for neural networks. Design parameters are concerned with the hardware details such as the number of memory banks, the maximum number of channels the IP can process, and other related aspects. In contrast, typological parameters are related to the network typology and include information about the layers and their configurations. The rest of the thesis will make use of these two concepts to design and implement FPGA-based hardware for neural networks.

### 1.4 Thesis Outline

**Chapter 2** focuses on providing background information about Convolutional Neural Networks and their typical components. The chapter also explains why YOLOv4-tiny was chosen as the network of interest for this particular design.

**Chapter 3**, popular techniques for optimizing Convolutional Neural Networks on Field Programmable Gate Arrays (FPGAs). It also highlights recent research studies that have explored methods for accelerating YOLO on FPGAs.

**Chapter 4** delves into the software tools and platforms used to implement the various layers of the YOLOv4-tiny network. The chapter provides a detailed explanation of the Vitis Unified software platform and its role in implementing CNN. The chapter gives the reasons for choosing Vitis Unified, highlighting its advantages over other software platforms in terms of ease of use, flexibility, and performance. The chapter also presents the design flow of the Vitis platform and the optimization techniques used to improve the performance of the implemented layers. Overall, the chapter provides a comprehensive understanding of the software tools used in the implementation of the YOLOv4-tiny. network.

**Chapter 5** provides a comprehensive description of the bare-metal floating-point model of the YOLOv4-tiny network, including its architecture and layers. It discusses the results obtained from profiling the simulation model to identify the bottleneck layers that may affect the network's overall performance. Additionally, the chapter introduces the bare-metal fixed-point model of the YOLOv4-tiny network, which serves as a reference for hardware implementation. The section also explains the methodology used to convert the floatingpoint model into a fixed-point model and describes the differences between the two models. Overall, Chapter 5 provides important background information necessary for the subsequent hardware implementation of the network.

**Chapter 6** focuses on the hardware IP design of each layer in the YOLOv4-tiny network. It begins by providing an overview of the main methods and algorithms for each IP. The chapter then goes on to provide a detailed explanation of the design and implementation process.

**Chapter 7** concentrates on the system-level design and optimizations for the implementation of the YOLOv4-tiny network on FPGA.

**Chapter 8** evaluates the results of the hardware-software codesign model and compares them with previous work regarding YOLOv4-tiny. It also compares the FPGA implementation results of the model with those of the CPU.

**Chapter 9** summarizes the key findings of the thesis and highlights the contributions of the work. It also discusses the limitations of the proposed approach and suggests potential areas for future research and improvement.

# Chapter 2

# **CNN Background**

Background information about neural networks is provided in this chapter to support the selection of YOLO. Section 2.1.1 explains the fundamental concepts of Convolution Neural Networks which include the metrics for evaluating CNN and datasets used. Section 2.2 introduces Yolo Algorithm. Section 2.3 describes the motivation for the selection of the YOLOv4tiny object detection algorithm. Finally, section 2.4 gives the description of YOLOv4-tiny architecture.

### 2.1 Convolutional Neural Network

Convolutional Neural Networks (CNNs) are bio-inspired, as connections between artificial neurons are similar to biological synapses. In contrast with fully-connected networks, in which every neuron is linked to all neurons in the next layer, CNN has a relatively concise organization. Because each neuron only responds to a certain receptive field. The reduction in connectivity means lower computational complexity. Therefore, CNN has gained popularity in image classification, object detection, and signal processing.

#### 2.1.1 Convolutional Layer

Convolution filters are the main computational element in CNNs. In the case of an RGB image input, there are three input channels, each of which can be represented as a 2-D matrix. If a convolutional layer has  $N_{in}$  input channels, it will have  $N_{out}$  convolution filters that transform inputs into  $N_{out}$  output channels. In this equation 2.1,  $f_i$  represents the  $i^{th}$  input channel, and  $g_i$  represents the  $j^{th}$  output channel. The formula represents the computation for the output of a single neuron in a fully connected layer of a neural network without activation function applied to the output.

$$g_j = \sum_{i=1}^{N_{in}} f_i * w_{i,j} + b_j, \quad \text{with} \quad j \in [1, N_{out}]$$

(2.1)

The  $w_{i,j}$  term is a filter window used in convolutional operations, and its size is pre-determined by the designers. The values contained in  $w_{i,j}$  and  $b_j$  are called weights and biases, respectively.  $k_h$  and  $k_w$  represent the filter width and height. To perform a forward calculation in a convolutional layer, a total of  $k_h \times k_w \times N_{in} \times N_{out}$  weights and  $N_{out}$  biases are required. When we consider the height and width of each output feature map to be  $g_h$  and  $g_w$ , respectively, we can estimate the total workload of the layer using Floating point operations (FLOPS).

Workload (FLOPS) =

$$g_h \times g_w \times k_h \times k_w \times N_{\text{in}} \times N_{\text{out}} \times 2$$

(2.2)

In the equation 2.2, the workload is multiplied by two because there are nearly the same amount of accumulation and multiplication operations. The values of  $g_w$  and  $g_h$  are typically determined based on the input size, whether the input is padded at the edges, and the stride of the sliding windows.

#### 2.1.2 Other Typical Layer Types

In addition to convolutional layers, various types of layers have been introduced for different purposes such as creating non-linear models, compressing data, and generating more informative outputs.

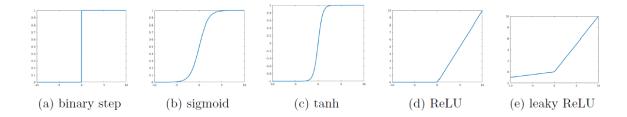

• Non-linearity layers

Non-linearity is crucial in deep learning architectures to provide the necessary nonlinearity, which enables the model to learn complex relationships between inputs and outputs. The non-linear activation functions that are commonly used include binary step, sigmoid, tanh, ReLU, Leaky ReLU, ELU, and so on shown in figure 2.1. The ReLU family of activation functions has become increasingly popular in recent times [11]. This type of function is piecewise linear, and it returns zero for negative inputs and the input value for positive inputs. Rectified Linear Unit (ReLU) has been demonstrated to be computationally efficient and outperforms other activation functions such as sigmoid and tanh in a range of deep learning applications, including image recognition and natural language processing.

Leaky ReLU is used as the activation function in the convolutional layers of the YOLOv4tiny neural network to prevent the "dying ReLU" problem and improve the flow of gradients during backpropagation [6]. Its use helps to maintain high accuracy while reducing the computational cost of the network, making it suitable for real-time object detection applications.

Figure 2.1: Non-linear activation function [12]

#### • Batch normalization

It is a technique utilized to enhance the stability of a neural network [13]. Typically, input data to a neural network is uniform and may not be differentiable in all areas. This technique modifies the distribution of the data, resulting in quicker convergence and decreased overfitting. It can also address the internal covariate shift issue, where the input distribution to each layer changes as the parameters of the previous layers are updated during training, leading to slow convergence and poor performance. Batch normalization is applied after the convolutional layers and before the activation function.

$$\hat{g}_j = \frac{g_j - \mu_B}{\sqrt{\sigma_B^2 + \epsilon}} \tag{2.3}$$

$$g'_j = \gamma \hat{g}_j + \beta \tag{2.4}$$

It takes  $g_j$  and  $g'_j$ , which are the inputs and outputs of the layer, respectively.  $\mu_B$  and  $\sigma_B^2$  represent the mini-batch mean and variance, respectively. A small value denoted by  $\epsilon$  is added to the denominator to avoid division by zero. The parameters  $\epsilon$  are used to scale and shift the normalized values of  $g_j$ , and their values are learned during the training process.

#### • Pooling layer

Max pooling is a valuable and effective method for decreasing the amount of data in deep learning models. It works by selecting a representative value to represent a small region, usually the maximum or average value within that region. This helps to reduce the amount of information in the data while preserving the essential features, making it simpler to work with and analyze the data. As a result, pooling is an efficient way to reduce the computational burden of deep learning models by downsampling the data.

#### • Fully-connected layer

The fully-connected layer is utilized as the last layer in deep learning models to produce classification outcomes by taking into account all the features from previous layers. However, this layer increases computational demands because each neuron in the preceding layer is connected to every neuron in the fully-connected layer, leading to numerous connections and computations. Despite this challenge, fully-connected layers are still valuable for attaining precise classification outcomes in deep learning models.

#### • Softmax layers

Softmax layers are frequently employed in image classification tasks because they can transform the raw scores assigned to each class into probabilities. Before softmax, class classification is based solely on the scores assigned to each class, which can be vague and difficult to interpret, and the sum of these scores across all classes may not be a definite value. The softmax layer addresses these issues by converting the scores into probabilities using the below formulae which offers a more precise and easily understandable indication of the probability of each class.

$$P_i = \frac{e^{|z|_i}}{\sum_{j=1}^K e^{|z_j|_j}}.$$

where  $z_i$  is the input to the *i*-th neuron, K is the total number of neurons in the layer, and  $P_i$  is the output probability of the *i*-th neuron. In other words, the softmax function takes a set of scores (the *z* values) and squashes them into a set of probabilities that sum to 1. Each  $P_i$  represents the probability that the input belongs to class *i*. The denominator ensures that the sum of all the probabilities is 1, while the numerator exponentiates each score to ensure that the probabilities are non-negative.

#### 2.1.3 Evaluation Metrics

Evaluation metrics for object detection are used to evaluate the performance of a model on an object detection task. These metrics provide a way to compare multiple detection systems fairly and objectively, either against each other or against a benchmark. Metrics based on average precision (AP) and its derivatives are used to assess the quality of object detections and benchmark them accordingly.

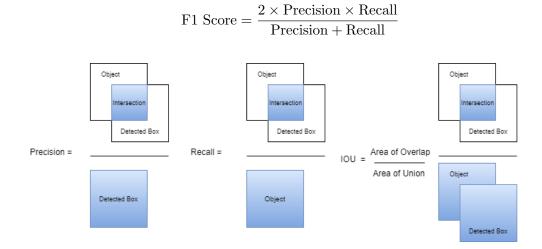

#### • Intersection Over Union (Intersection over Union (IoU))

The fundamental principle underlying modern evaluation metrics for object detection is the Intersection-over-Union (IoU) overlap measure. This metric is defined as the ratio of the intersection of the detection bounding box and the ground truth bounding box to their union. By calculating the IoU, we can determine how well the predicted bounding box aligns with the ground truth bounding box. Typically, an IoU score greater than 0.5 is considered a good prediction. This threshold value may vary depending on the specific application or context.

• True Positives  $t_p$

In object detection tasks, true positives  $t_p$  refer to the number of detections with an IoU score greater than 0.5, indicating that the predicted bounding box overlaps sufficiently with the ground truth bounding box.

• False Positives  $f_p$

False positives  $f_p$  in object detection tasks indicate the number of predicted bounding boxes that either have a low degree of overlap with the ground truth bounding box (measured by an IoU score less than or equal to 0.5) or are identified as duplicates.

#### • False negatives $f_n$

In object detection tasks, false negatives  $f_n$  represent the number of objects that are present in the ground truth but are not detected by the model, regardless of whether the undetected object has an IoU score greater than or less than 0.5. In object detection tasks, false negatives [FN] represent the number of objects that are present in the ground truth but are not detected by the model, regardless of whether the undetected object has an IoU score greater than or less than 0.5.

#### • Precision

Precision is a measure that is utilized in object detection tasks to assess how accurately the model is predicting the bounding boxes. It is calculated by dividing the number of true positive detections by the sum of true positive and false positive detections. Essentially, precision evaluates the proportion of predicted bounding boxes that are accurate.

$$Precision = \frac{True Positive}{True Positive + False Positives}$$

#### • F1 Score

The F1 score is a popular metric used in object detection to assess the overall performance of a model. It is calculated as the harmonic mean of precision and recall, which provides a balanced measurement of the model's capability to identify positive objects while minimizing false positives.

Figure 2.2: Precision vs Recall vs IoU [14]

#### • Average Precision (AP)

To evaluate the performance of a detection model in object detection tasks, the precisionrecall curve is often used, which displays the precision (y-axis) and recall (x-axis) values calculated at different confidence thresholds used for detecting objects. The area under this curve, which is also known as the average precision (AP), provides a single numerical score that summarizes the overall performance of the detection model across all recall levels. The AP score measures how well the model can balance precision and recall across different confidence thresholds, with higher AP scores indicating better model performance. A perfect detection model would have an AP score of 1.0.

Average Precision (AP) =

$$\int_0^1 P(r)dr$$

#### • Mean Average Precision (mAP)

The Mean Average Precision (Mean Average Precision (mAP)) is a metric used in object detection tasks to evaluate the overall performance of a model across all object classes. It is the average of the AP values calculated for each class, with AP being the area under the precision-recall curve. The mAP@0.5 indicates that the calculation is done using an IoU threshold of 0.5 to determine whether a predicted bounding box overlaps with the ground truth box.

#### 2.1.4 Dataset

The Common Objects in Context (COCO) (Common Objects in Context) [11] dataset is a comprehensive collection of images that are used extensively in computer vision research for object detection, segmentation, and captioning. With over 330,000 images and 2.5 million object instances, it is considered a large-scale image recognition dataset. The dataset features images from various categories, including people, animals, vehicles, household items, and outdoor scenes. This diversity makes it a valuable resource for researchers working on computer vision problems related to real-world scenarios.

The COCO dataset is an ideal choice for training and assessing the YOLOv4-tiny model for several reasons.

- Firstly, the dataset offers a wide range of images that cover various object categories and situations. This enables the model to learn and identify various objects, making it helpful for various applications.

- Secondly, the COCO dataset contains comprehensive annotations for each image, including the category, location, and size of each object. This allows the YOLOv4-tiny model to identify and locate objects within an image accurately and classify them correctly, even in complex scenes with multiple objects and occlusions.

• Thirdly, the COCO dataset is widely recognized in the computer vision community, making it a standard benchmark for object detection and segmentation models. This enables the YOLOv4-tiny model's performance on the COCO dataset to be compared with other state-of-the-art models and assessed in a consistent and unbiased manner.

#### 2.1.5 Frameworks

Deep neural network (DNN) frameworks are software tools that provide pre-built implementations of common deep-learning algorithms. Some frameworks even come with pre-trained neural network models. These tools help speed up the development and research in the field of deep learning. Frameworks work with a higher level of abstraction that enables users to define the structure of the application. Configuration files contain the application skeleton that specifies the layer types, number of neurons per layer, input data shape, and other details. Many frameworks can also use GPUs to accelerate the inference and learning process.

Although YOLO was initially implemented in the Darknet framework, it has also been implemented in other popular frameworks. Choosing the right framework is essential to solving the problem effectively. In addition to Darknet, this section will discuss two other widely-used frameworks.

• **Darknet**: Darknet is a neural network framework that is free and available for anyone to use [15] It is created using the programming languages C and CUDA and was developed by Joseph Redmon. The framework has gained recognition because it implemented YOLO, which is an object detection algorithm known for its high accuracy and real-time object detection capabilities. The framework can be utilized with both CPU and GPU acceleration and is supported by various platforms such as Linux, Windows, and macOS.

The most significant benefit of the darkent is its speed and efficiency. Its lightweight design and optimized algorithms allow it to execute fast inference times even on low-powered devices. Moreover, the framework has an intuitive and straightforward API, which makes it simple for researchers and developers to create, train, and evaluate their models.

• Caffe: Caffe is a framework for deep learning that was developed by the Berkeley Vision and Learning Center [16]. It is created with a focus on being efficient, modular, and extensible. Caffe supports both CPU and GPU acceleration, similar to Darknet, and is written in C++ and CUDA, with bindings for other programming languages such as Python and MATLAB.

Caffe is particularly strong because of its pre-trained model zoo. The model zoo contains a wide range of pre-trained models for various computer vision tasks such as object detection, segmentation, and classification. This feature enables developers and researchers to quickly build and evaluate their models for their specific use cases without needing to train their models from scratch. The framework's modular design is another advantage of Caffe, which allows customization and extension of the framework. This modular structure makes Caffe an ideal platform for the research and development of new deep-learning algorithms and architectures.

• **Tensorflow** TensorFlow is a deep learning framework created by the Google Brain team that has become widely used and is considered one of the most popular open-source deep learning frameworks available [17]. TensorFlow works on both CPU and GPU and can be used on various platforms such as Linux, Windows, and macOS.

One of the significant advantages of TensorFlow is its ability to be versatile and scalable, allowing users to train various types of deep learning models such as convolutional neural networks, recurrent neural networks, and generative adversarial networks. TensorFlow is also optimized for distributed computing, making it possible to train large-scale models or on distributed clusters.

Another benefit of TensorFlow is its vast community of users and contributors, which provides numerous resources, including pre-trained models, tutorials, and extensions. This enables researchers and developers to quickly build and evaluate models for their specific applications.

#### Why Darknet over Tensorflow or Caffe Framework.?

Darknet is a preferred framework over Caffe and TensorFlow for the YOLOv4-tiny model for several reasons. One of the significant advantages of Darknet is its speed and efficiency, as it is optimized for object detection tasks and written in C and CUDA, making it fast and memory efficient, particularly when running on GPU. Additionally, Darknet's open-source nature enables developers to customize and modify it to suit specific requirements, which is crucial for improving the performance of the YOLOv4-tiny model. Darknet was built specifically for the YOLO family of object detection models, including YOLOv4-tiny, and is optimized for their unique architecture and requirements. Darknet also provides a wide range of tools and functions for training, testing, and evaluating object detection models, including data augmentation, model visualization, and performance evaluation metrics, making it a comprehensive and integrated solution for object detection tasks.

# 2.2 YOLO: Real-Time object detection algorithm

Joseph Redmon et al. introduced the first generation of You Only Look Once (YOLO) in 2016, which uses a single Convolutional Neural Network (CNN) to predict both class probabilities and bounding boxes [5]. YOLO divides the input image into grids of size S x S, with each grid capable of providing B bounding boxes, along with confidence values for the boxes and probabilities for C classes. YOLO's low latency and high throughput are the key factors behind its state-of-the-art performance in real-time detection.

In 2017, YOLOv2, an improved version of YOLO, was launched with a range of upgrades such as batch normalization and *anchor boxes* [18]. Anchor boxes refer to preset bounding boxes that have fixed scales between width and height. By using anchor boxes instead of a fully-connected layer, the size of objects that can be detected is limited, but it enhances the recall rate and separates object classifications from bounding boxes. To fulfill the requirement of a faster and more efficient object detection network that can run in real-time on devices with limited computational resources like mobile phones or embedded systems, the YOLOv2 tiny model was developed. Compared to the full YOLOv2 network, the tiny model has fewer layers and parameters, which results in faster processing times while maintaining a satisfactory level of accuracy of about 57% in object detection tasks. However, the anchor boxes used in YOLOv2-tiny restrict the range of object sizes that can be detected. This can result in missed detections or inaccurate bounding box sizes for objects outside of the preset range. Moreover, The YOLOv2-tiny model was designed to detect a limited number of object classes, typically around 20. This can be a limitation in scenarios where a larger number of object classes need to be detected.

In 2018, a newer version of YOLO called YOLOv3 was introduced, which improved the accuracy of the model [19]. Instead of using softmax activation at the output of the network, sigmoid activation was used to address the poor performance of softmax when multiple labels correspond to the same bounding box. YOLOv3 also uses a structure similar to feature pyramid networks, combining upsampled features with those from previous layers to process the combined features further through several convolutional layers. This structure makes predictions across different scales easier, leading to improved accuracy.

The YOLOv3 model has a workload of 65.86 GFLOPs and achieves a 51.5% mAP@0.5 on the COCO test-dev dataset while running at 35 FPS on a Pascal Titan X GPU. For resource-constrained environments, a lighter model called YOLOv3-tiny is available. This model is more suitable for embedded applications and can achieve a 33.1% mAP@0.5 on the same test dataset but with a much higher frame rate of 220 FPS on the same GPU device.

In 2020, YOLOv4 was introduced as an upgraded version of previous YOLO models, offering faster, more accurate, and more robust object detection capabilities. One of the key advancements of YOLOv4 is its utilization of a "bag of freebies" and a "bag of specials" [20]." The former involves standard techniques like data augmentation, label smoothing, and random training shapes to enhance model performance, while the latter comprises more sophisticated techniques such as the Mish activation function, self-adversarial training, and DropBlock regularization. YOLOv4 also incorporates a CSPDarknet53 backbone, which is a modified version of the Darknet architecture that includes cross-stage partial connections to improve information flow within the network. Along with a spatial pyramid pooling layer and a path aggregation network, the CSPDarknet53 backbone enhances the model's ability to detect objects at varying scales YOLOv4-tiny is a less resource-intensive version of the YOLOv4 model used for object detection [20]. Its design is suitable for deployment in limited-resource environments like mobile devices and embedded systems. Compared to the full YOLOv4 model, YOLOv4-tiny has a smaller model size and fewer layers, enabling it to operate at a faster speed while utilizing less memory. Despite its reduced size, YOLOv4-tiny still attains high accuracy, with a mean average precision (mAP) of 43.5% on the COCO dataset.

Similar to YOLOv3-tiny, YOLOv4-tiny utilizes anchor boxes for bounding box prediction and a feature pyramid network for detecting objects at different scales. It incorporates some of the enhancements from YOLOv4, including the use of CSPDarknet53 as the backbone network and the integration of Spatial Pyramid Pooling (SPP) (Spatial Pyramid Pooling) to capture context information. The implementation of a new architecture in the Backbone which is called CSPDarkent 53 and the modifications in the Neck have improved the mAP(mean Average Precision) by 10%.

# 2.3 Motivation For choosing YOLOv4-tiny

Table 2.1 gives the comparison of the YOLO model for object detection based on the trade-off between accuracy (mAP) and computational complexity (GOPS) [20] [19] [18]. The Original YOLO models have more than 8x parameters as compared to their tiny counterparts. The YOLO Tiny models are more desirable than the original YOLO models due to their smaller size, faster speed, and lower computational requirements. They are particularly suitable for cases that necessitate real-time object detection on devices with limited power, like embedded systems, drones, and smartphones. Moreover, the YOLO Tiny models usually outperform the original YOLO models when detecting small or distant objects since they are trained on smaller input images, making them more adept at identifying such objects.

| Model       | Parameters        | mAP    | GOPS  |

|-------------|-------------------|--------|-------|

| YOLOv2      | $50.80\mathrm{M}$ | 76.80% | 29.46 |

| YOLOv2-tiny | $6.97 \mathrm{M}$ | 57.10% | 5.46  |

| YOLOv3      | $62.90\mathrm{M}$ | 57.90% | 65.34 |

| YOLOv3-tiny | $8.97\mathrm{M}$  | 33.10% | 5.40  |

| YOLOv4      | $63.80\mathrm{M}$ | 46.70% | 62.00 |

| YOLOv4-tiny | $6.90\mathrm{M}$  | 44.00% | 6.62  |

Table 2.1: Comparison of YOLO models.

#### 2.3.1 Theorectical upper bound performance:

Before selecting the correct version of the YOLO algorithm to be implemented on a target platform, it is important to estimate a theoretical upper-bound performance using the number of computational resources like Multiply-Accumulate (MACC) units present in the target platform. The target platform chosen for this project is ZedBoard. In CNN, convolutional operations are the most computationally intensive operations that are done in a repetitive manner for an entire layer in CNN which takes about 99% [8]. Convolution operation requires Multiply-Accumulate (Multiply and Accumulate (MACC)) operation which is mapped to DSP slices present on the target platform. Therefore for the analysis, 1 DSP slice will be considered as a processing element (Processing Element (PE)) which is designed to perform repetitive multiplication and addition operations, making them well-suited for convolution operations in deep-learning models.

The Theoretical upper bound performance is given by Frames per second which relates to the throughput of the design and the processing elements present in the target platform as follows :

Frame per seconds (Frame Per Seconds (FPS)) =  $\frac{(\text{Throughput of 1 PE x Number of PEs})}{\text{Workload}}$

where:

- Throughput of 1 PE is the number of MACC operations that can be performed by 1 PE per second.

- Number of PEs is the total number of PEs in the target platform.

- Workload is the number of MAC operations required for one inference given as Giga Operations per second (GOPS).

In ZedBoard, there are about 220 DSP slices and each Slice is of size 18x25 fixed-point multiplications. Assuming each DSP slice can perform 1 MAC operation per cycle, Therefore the throughput of a slice per cycle is given as

Throughput of 1 PE per Cycle = 1 MAC

Assuming all PEs are active at the same time i.e. all 220 DSP slices are active at the same time. Additionally, if the clock frequency of the design is 100 MHz. Then

Throughput of 1 PE  $\times$  Number of PE =  $1 \times 100 \times 10^6 \times 220 = 22$  GOPS/secs

The workload for each tiny model can be used from table 2.1.

| Yolo version | Computations (GOPS) | Theoretical Upper bound FPS |

|--------------|---------------------|-----------------------------|

| Yolov2       | 29.46               | 0.74                        |

| Yolov2 tiny  | 5.56                | 3.95                        |

| Yolov3       | 65.34               | 0.33                        |

| Yolov3 tiny  | 5.4                 | 4.07                        |

| Yolov4       | 52.00               | 0.42                        |

| Yolov4 tiny  | 6.62                | 3.33                        |

Table 2.2 gives the FPS results for the YOLO versions shown. The reason for not choosing the yolov3-tiny model was its low accuracy of approximately 33% mAP. Selection between YOLOv2-tiny and YOLOv4-tiny depends on various factors, including the balance between accuracy and speed and the robustness to variation in input data. In terms of speed, which is crucial, YOLOv4-tiny appears to be a better option as it has fewer layers to process as compared to YOLOV2-tiny which means that it has fewer layers and parameters. While this makes the network faster and more efficient, it also reduces its capacity to learn complex features and patterns in the input data, which can affect its accuracy which explains why YOLOv4-tiny has a lower 44% mAP as compared to YOLOv2-tiny (57%). This lower accuracy is also due to the fact that the YOLOv4-tiny model is trained for detecting 80 different classes as compared to 20 classes in the case of YOLOv2-tiny but this also means that YOLOv4-tiny is more robust for new input. Furthermore, YOLOv4-tiny is a newer model that includes various improvements and optimizations compared to the earlier model, such as a better backbone architecture and an enhanced feature pyramid network, which contributes to its accuracy and efficiency. These are some of the reasons why YOLOv4-tiny is preferred over other tiny versions for object detection algorithms.

# 2.4 YOLOv4-tiny

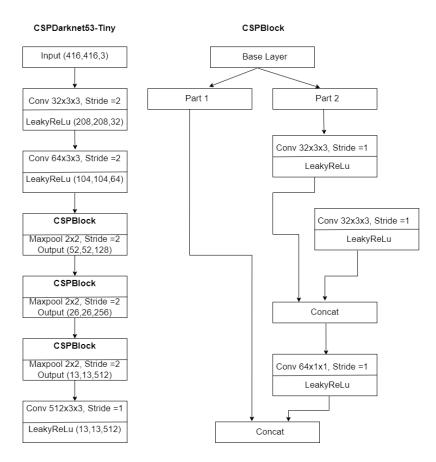

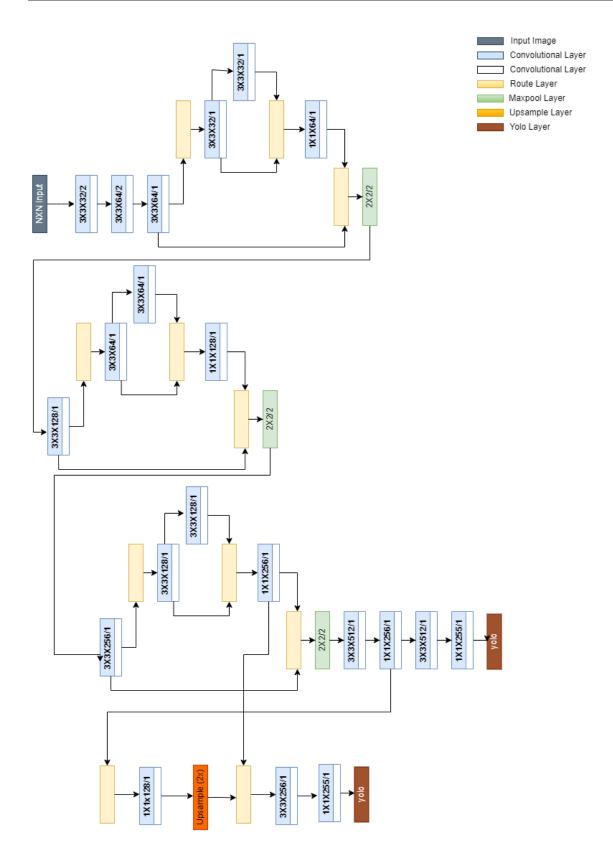

YOLOv4-tiny has a two-part structure that includes detection layers and a backbone network. The backbone network is a modified version of CSPDarknet53, which is a variant of the Darknet network that uses cross-stage partial connections to enhance feature propagation. The CSPDarknet53-tiny architecture implemented in YOLOv4-tiny has a smaller depth and width than the original CSPDarknet53, making it a smaller and faster network.

• **CSPDarknet53-tiny** The backbone network in YOLOv4-tiny, as shown in Figure 2.3 is constructed using CSPDarknet53-tiny, a simplified version of the CSPDarknet53 architecture used in the larger YOLOv4 model. The abbreviation CSP stands for Cross Stage Partial connections, which link the layers in the network. The CSP technique splits the layers into two branches, with one branch performing the convolutional operation and the other performing identity mapping. The outputs of these branches are then combined through concatenation before passing to the next layer, improving gradient flow and reducing overfitting.

The CSPDarknet53-tiny architecture includes three convolutional layers and three CSP-Block modules. The first two convolutional layers consist of a convolutional layer and a Leaky-ReLU layer, with each convolutional layer having a kernel size of 3 and a stride of 2. The final convolutional layer has a kernel size of 3 and a stride of 1. In contrast to the Mish activation function used in the original CSPDarknet53 architecture, CSPDarknet53-tiny uses the simpler Leaky-ReLU activation function to simplify the calculation process. The YOLOv4-tiny model employs two feature maps with different sizes, namely 13 x 13 and 26 x 26, for detecting objects. For each feature map, three anchor boxes of varying sizes are utilized to predict three bounding boxes. Prior to training, k-means clustering is applied to determine the number of anchor boxes, resulting in a total of six predefined boxes across the three scales.

To handle the issue of multiple overlapping detection bounding boxes, YOLOv4-tiny uses a variation of Non-Maximum Suppression (NMS) called distance intersection over union non-maximum suppression (DIoU-NMS). This approach takes into account the distances between the center points of the bounding boxes, especially when they do not overlap. The threshold for DIoU-NMS in this case is set to 0.4.

The YOLOv4-tiny architecture consists of 21 convolutional layers out of which 19 are depthwise convolutions followed by LeakyRelu activations functions and 2 are fully connected layers. There are about 3 Maxpool Layers, 11 route layers, 1 Upsample layer, and 2 Yolo Layers for detecting images at different scales of 26x26 and 13x13 respectively. The detailed block diagram and topological feature of each layer are presented in figure 2.4. Table 2.4 gives the topological configurations on each layer with Billion Floating point operation (BFLOPS) per layer.

Figure 2.3: YOLOv4-tiny Architecture

| Layer<br>conv<br>conv                       | Filters<br>32                     | Size                  | Input                | Output               | BFLOPS |

|---------------------------------------------|-----------------------------------|-----------------------|----------------------|----------------------|--------|

|                                             | 32                                |                       | -                    | 1                    | DILOID |

| conv                                        | 02                                | $3 \ge 3 / 2$         | 416 x 416 x 3        | $208 \ge 208 \ge 32$ | 0.075  |

| 1                                           | 64                                | $3 \ge 3 / 2$         | $208 \ge 208 \ge 32$ | $104 \ge 104 \ge 64$ | 0.399  |

| conv                                        | 64                                | $3 \ge 3 / 1$         | $104 \ge 104 \ge 64$ | 104 x 104 x 64       | 0.397  |

| route                                       | route $2 (output from layer 1/2)$ |                       |                      |                      |        |

| conv                                        | 32                                | $3 \ge 3 / 1$         | $104 \ge 104 \ge 32$ | $104 \ge 104 \ge 32$ | 0.199  |

| conv                                        | 32                                | $3 \ge 3 / 1$         | $104 \ge 104 \ge 32$ | $104 \ge 104 \ge 32$ | 0.199  |

| route                                       |                                   | 54 (outp              | outs from layers 5   | 5 and 4)             |        |

| conv                                        | 64                                | 1 x 1 / 1             | $104 \ge 104 \ge 64$ | 104 x 104 x 64       | 0.089  |

| route                                       |                                   | $2\ 7\ (output)$      | outs from layers 2   | 2 and 7)             |        |

| max                                         | 2 x 2 / 2                         | $104 \ge 104 \ge 128$ | $52 \ge 52 \ge 128$  | $26 \ge 26 \ge 128$  | -      |

| conv                                        | 128                               | $3 \ge 3 / 1$         | $52 \ge 52 \ge 128$  | $52 \ge 52 \ge 128$  | 0.397  |

| route                                       | ·                                 | 10 <i>(o</i>          | utput from layer     | 1/2)                 |        |

| conv                                        | 64                                | $3 \ge 3 / 1$         | $52\ge52\ge64$       | $52 \ge 52 \ge 64$   | 0.199  |

| conv                                        | 64                                | $3 \ge 3 / 1$         | $52 \ge 52 \ge 64$   | $52 \ge 52 \ge 64$   | 0.199  |

| route 13 12 (outputs from layers 13 and 12) |                                   |                       |                      |                      |        |

| conv                                        | 128                               | 1 x 1 / 1             | $52 \ge 52 \ge 128$  | $52 \ge 52 \ge 128$  | 0.089  |

| route                                       | ·                                 | 10 15 (outp           | outs from layers 1   | 0 and 15)            |        |

| max                                         | 2 x 2 / 2                         | $52 \ge 52 \ge 256$   | $26 \ge 26 \ge 256$  | $13 \ge 13 \ge 256$  | -      |

| conv                                        | 256                               | $3 \ge 3 / 1$         | $13 \ge 13 \ge 256$  | $13 \ge 13 \ge 256$  | 0.397  |

| route 18 (output from layer 1/              |                                   |                       |                      | 1/2)                 |        |

| Conv                                        | 128                               | $3 \ge 3 / 1$         | $26 \ge 26 \ge 128$  | $26 \ge 26 \ge 128$  | 0.199  |

| Conv                                        | 128                               | $3 \ge 3 / 1$         | $26 \ge 26 \ge 128$  | $26 \ge 26 \ge 128$  | 0.199  |

| Route                                       | 21, 20                            | -                     | -                    | $26 \ge 26 \ge 256$  | -      |

| Conv                                        | 256                               | 1 x 1 / 1             | $26 \ge 26 \ge 256$  | $26 \ge 26 \ge 256$  | 0.089  |

| Route                                       | 18, 23                            | -                     | -                    | $26 \ge 26 \ge 512$  | -      |

| Max                                         | -                                 | $2\ge 2$ / $2$        | $26 \ge 26 \ge 512$  | $13 \ge 13 \ge 512$  | -      |

| Conv                                        | 512                               | $3 \ge 3 / 1$         | $13 \ge 13 \ge 512$  | $13 \ge 13 \ge 512$  | 0.397  |

| Conv                                        | 256                               | 1 x 1 / 1             | $13 \ge 13 \ge 512$  | $13 \ge 13 \ge 256$  | 0.044  |

| Conv                                        | 512                               | $3 \ge 3 / 1$         | $13 \ge 13 \ge 256$  | $13 \ge 13 \ge 512$  | 0.399  |

| Conv                                        | 255                               | 1 x 1 / 1             | $13 \ge 13 \ge 512$  | $13 \ge 13 \ge 255$  | 0.044  |

| YOLO                                        | -                                 | -                     | -                    | $13 \ge 13 \ge 255$  | -      |

| Route                                       | 27                                | -                     | -                    | $13 \ge 13 \ge 256$  | -      |

| Conv                                        | 128                               | 1 x 1 / 1             | $13 \ge 13 \ge 256$  | $13 \ge 13 \ge 128$  | 0.011  |

| Upsample                                    | -                                 | 2x                    | $13 \ge 13 \ge 128$  | $26 \ge 26 \ge 128$  | -      |

| Route                                       | 33, 23                            | -                     | -                    | $26 \ge 26 \ge 384$  | -      |

| Conv                                        | 256                               | $3 \ge 3 / 1$         | $26 \ge 26 \ge 384$  | 26 x 26 x 256        | 1.196  |

| Conv                                        | 255                               | 1 x 1 / 1             | $26 \ge 26 \ge 256$  | 26 x 26 x 255        | 0.088  |

| YOLO                                        | -                                 | -                     | -                    | 26 x 26 x 255        | -      |

Table 2.3: Network architecture of YOLOv4-tiny

# Chapter 3

# **Literature Review**

This chapter focuses on prior research that involves implementing Convolutional Neural Networks (CNNs) on FPGAs, as well as the specialized techniques utilized in embedded applications. The major obstacle is the significant computation and memory storage demanded by CNNs.

# 3.1 2-D Convolution on FPGA

Numerous research studies are currently focused on optimizing 2-D convolution for embedded FPGA devices, with a primary focus on enhancing memory storage, data bandwidth, and parallelism. By achieving optimal performance in these areas, FPGA devices can handle the computational demands of convolutional neural networks (CNNs) more efficiently than traditional processors, enabling high-performance computing with low power consumption.

The two primary buffer schemes used in FPGA-based convolutional neural networks (CNNs) are full buffering (FB) and partial buffering (PB) [21]. Full buffering involves accessing the entire feature map in a sequential line-by-line manner, ensuring that every input pixel is read from external memories only once. This data is then stored locally and reused by the sliding window. However, this approach typically requires a large on-chip memory on FPGA due to the need to store all input data locally.

In contrast, partial buffering divides the feature map into multiple regions and loads only one region at a time to the FPGA device. Although this approach requires less on-chip memory compared to full buffering, it has the drawback of loading the same data multiple times, which increases the frequency of accessing external memory and demands higher data bandwidth.

An alternative approach to partial buffering is the use of the Image to Column (Im2Col) algorithm [22] [23], which involves splitting the input feature map into batches that have the same size as weight windows. This transformation allows the convolution operation to be represented as a matrix multiplication, which can be further expanded into 1-D vectors. In this way, convolution can be computed as the dot product between the input vector and the

weight vector.

# 3.2 Fixed-point Quantization

Most FPGAs do not have floating-point hard cores, which makes it challenging to handle the high precision required for neural network training. A common approach is to train the network using floating-point representations on a GPU and then convert it to a lowerprecision version with or without retraining. This technique has been documented in research papers [24] [25].

Fixed-point implementation requires determining the number of bits allocated for the integer and fraction parts. In linear quantization, the bit width of integers depends on extreme values and the possibility of overflow. The length of the fraction part affects quantization error, and the step size of quantization shapes the data distribution. Therefore, it is crucial to investigate the trade-off between bit-width and network precision for different network types. This analysis is necessary for accurate implementation of neural networks on FPGAs.

Qiu et al. [26] introduced a dynamic strategy in 2016 that selects different fraction lengths for each layer in a neural network. Re-quantization is then performed between layers by shifting bits in the activation. This dynamic quantization approach is more efficient in terms of resource usage, especially when there is significant variation in weight and data distributions between layers.

In addition to linear quantization, there are alternative methods to reduce bit-width even further. Logarithmic data representation is a technique that transforms weight and activation values into the log domain. This approach can achieve compression because the original distributions of the data are typically non-uniform [27].

Rastegari et al. [28] introduced Binary-Weight-Networks and XNOR-Networks that binarize either the weights or both the weights and data. However, most studies on binarized networks concentrate on image classification rather than object detection due to the significant loss of precision that binarization causes, particularly in bounding box predictions.

# 3.3 Dynamically Configurable Architecture

Different layers within a neural network can have different typology parameters, such as the number of neurons, activation functions, and weights. These parameters can affect the computational requirements and memory access patterns of each layer, making it challenging to optimize performance for the entire network.

One possible solution to this challenge is to design specific hardware for each layer of the network. By customizing the hardware for each layer, it is possible to reduce off-chip memory

transactions and improve performance. For example, hardware accelerators can be designed to perform the specific computations required by each layer, which can lead to faster and more efficient processing [2]. However, one disadvantage of this approach is that it can require significant resources to put the entire network on hardware.

A potential solution to address the compatibility issue and huge storage requirements of intermediate results is to develop a unified hardware architecture that can accommodate all layers. This approach involves controlling multiplexers within the architecture to support a range of convolution types and configurations. This strategy has gained popularity in FPGA-based CNN implementations, with Chakradhar et al. [2] proposing it in 2010. However, a drawback of this approach is that it may sacrifice some performance for the sake of compatibility.

## 3.4 Related Work on YOLO

The Eyeriss architecture, introduced in [29], can minimize off-chip memory access of any CNN shape using a spatial architecture that includes 168 processing elements. This architecture employs a computational scheme named "row stationary" which enhances parallelism to achieve high throughput while optimizing the data movement to improve energy efficiency. The authors evaluated the Eyeriss architecture's performance on Xilinx V707 FPGA, which has 2800 DSP slices, using two popular CNNs: Alexnet and VGG-16. With 16-bit fixed-point arithmetic precision, Eyeriss achieves a frame rate of 37.1 frames/sec and throughput of 23.1 with a DRAM access of 0.0029 per MAC operation for Alexnet CNN, while for VGG-16, the frame rate is 0.7 frames/s with a DRAM access of 0.0035 per MAC operation.

In a recent paper [30], researchers proposed a fully scalable and configurable IP core to improve parallelism during both inference and training time. The core is responsible for accelerating the execution of all the algorithm steps, including pre-processing and model inference, and has been configured for real-time execution of YOLOv3-Tiny and YOLOv4-Tiny models. This core has been integrated into a RISC-V-based system-on-chip architecture and prototyped in an UltraScale XCKU040 FPGA, resulting in a complete system called Soc-Yolo. The IP core consists of a matrix of vector functional units that perform MAC computations, exploiting parallelism with both input and output Feature Map(FM) such as Intra-convolution (concurrently computing multiplications within 2D convolutions), Interconvolutions (Multiple 2D convolutions computed concurrently), and Intra-FM (computing multiple pixels of a single output feature map), inter-FM (concurrently processing multiple output feature map) and enhancing pixel and weight sharing. In performance tests, the YOLOv3-Tiny detector implemented in the SoC-YOLO platform achieved a frame rate of 32 FPS, with a peak throughput of 238 GOPS and an execution time of 30.9 ms. Similarly, the YOLOv4-Tiny detector on the SoC-YOLO platform achieved a frame rate of 31 FPS, with a peak throughput of 357 GOPS and an execution time of 32.1 ms. These results show that the Soc-Yolo-based implementation of the YOLOv3-Tiny and YOLOv4-Tiny models is significantly faster than the CPU version, with speed-ups of nearly 27x and 33x, respectively.

A parameterized FPGA-tailored architecture is proposed in [1] for low-latency detection with tiny YOLO3. The presented work is based on low-latency object detection on a low-end FPGA device like Zedboard. The paper also carries out a design space exploration for identifying design points that optimize latency while meeting the resource constraints of the FPGA device. The developed accelerator is utilized for the execution of all layers of the network through a run-time parameter setting, which is also parameterizable at compile time using Vivado HLS. The architecture is 1.5x more power efficient compared to the floating-point YOLOv3-tiny implementation on a Pascal Titan X and is 290x faster compared to the fully Arm Cortex A9 implementation. The proposed architecture achieves a frame rate of 1.88 FPS and 10.45 GOPs throughput with the low-cost FPGA evaluation board. Moreover, the proposed architecture sees a 290x improvement in latency compared to the hardcore processor of the device, achieving at the same time a reduction in mAP of 2.5 pp (30.9% vs 33.4%) compared to the original model under 16-bit fixed-point implementation.

In [31], a method is proposed to accelerate the YOLOv4 algorithm using FPGA in order to minimize inference time while maintaining high accuracy. The researchers evaluated resource utilization and inference time as important parameters for hardware acceleration of object detection algorithms. The proposed accelerator was designed for the Zynq-7000 SoC to maximize resource utilization and achieve large throughput. They used Vivado 2020.1 to prototype the hardware acceleration of the YOLOv4 algorithm, and employed loop pipelining optimization and loop tiling approach to enhance system throughput and reduce memory access, respectively. The proposed implementation achieved better resource utilization with 23.2k LUTs, 45.8 flip flops, 115 BRAMs, and 174 DSPs under the optimum frequency of 100 MHz. The design claimed to achieve a peak throughput of 189.14 GOP/s and 30 fps performance with an effective resource utilization of about 80%.

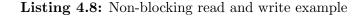

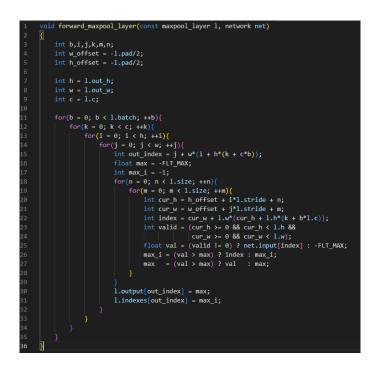

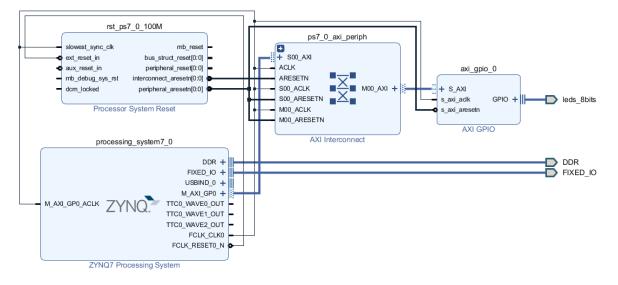

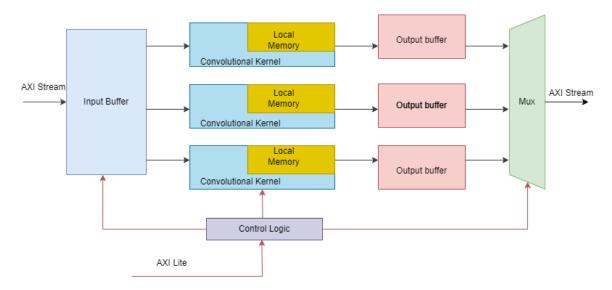

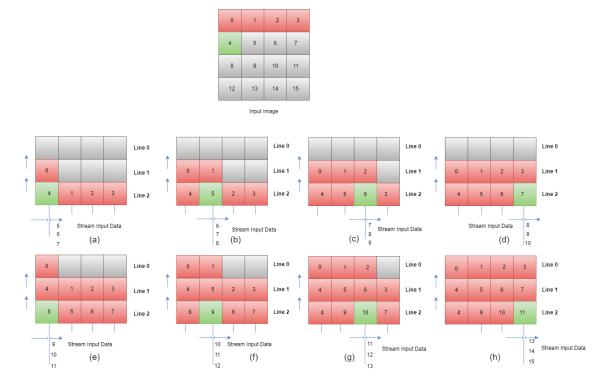

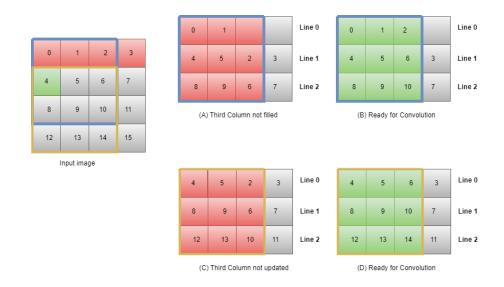

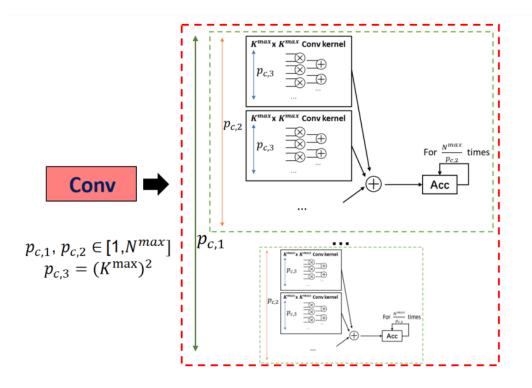

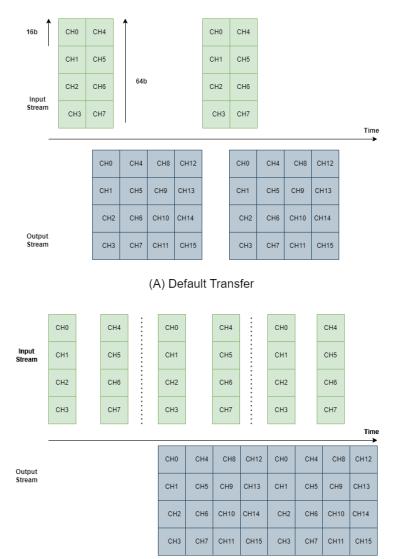

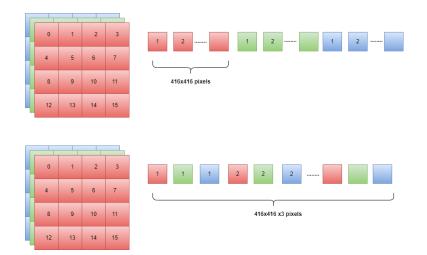

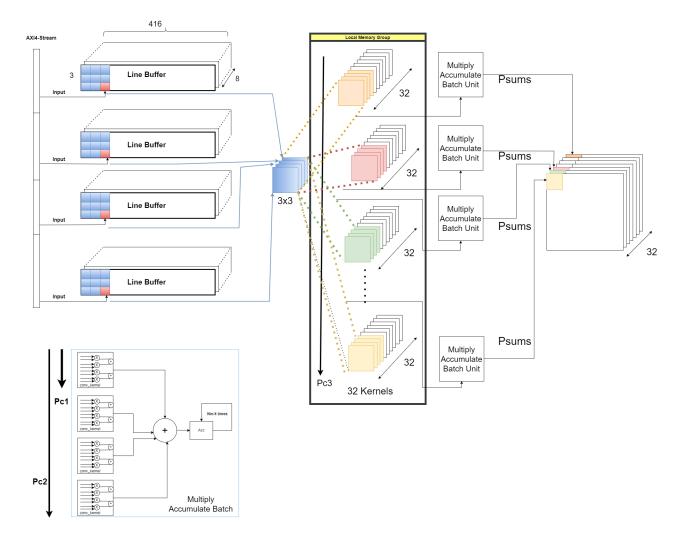

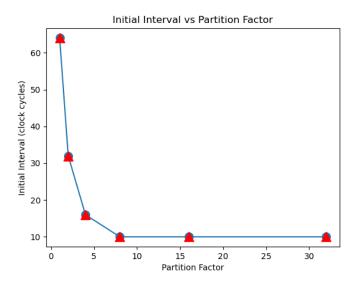

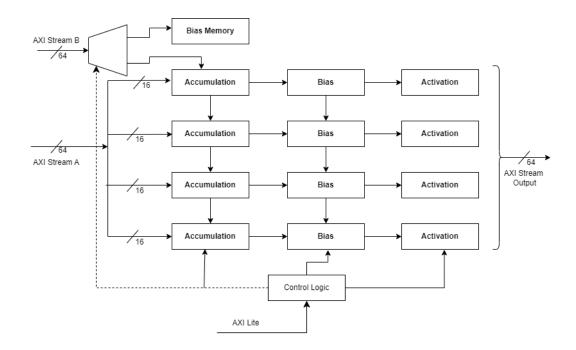

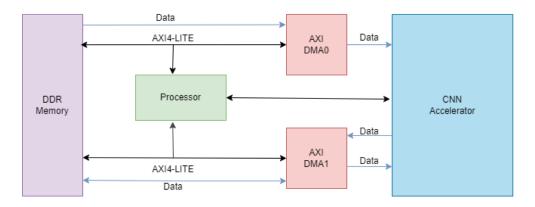

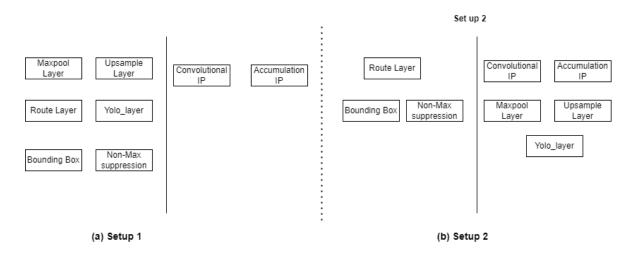

In [32], the authors describe an FPGA implementation of the lightweight YOLOv2 algorithm using a combination of binarized CNN and parallel State Vector regression for bounding box prediction and class estimation. The proposed architecture was implemented on the Xilinx Inc. Zynq UltraScale+ MPSoC zcu102 evaluation board. The binarized CNN was used for classification, while the parallel SVR was used for both classification and localization. The proposed architecture achieved an inference time of 24.5 msec per image, which corresponds to a frame rate of 40.81 FPS with dynamic board power consumption. Compared to the ARM Cortex-A57, the proposed architecture was 177.4 times faster and 1.1 times more power-hungry, with a performance per power efficiency that was 158.9 times better. The performance per power efficiency was calculated to be 9.06 FPS/W with a power consumption of 4.5 W.