# **UNIVERSITY OF TWENTE.**

Faculty of Electrical Engineering, Mathematics & Computer Science

# Radiation resilience evaluation of a Flash-based FPGA with a soft RISC-V Core

Kevin Böhmer M.Sc. Thesis - Embedded Systems September 2023

> Supervisors: dr. ir. M. Ottavi B. Endres Forlin

Computer Architecture for Embedded Systems Faculty of Electrical Engineering, Mathematics and Computer Science University of Twente P.O. Box 217 7500 AE Enschede The Netherlands

## Acknowledgements

I am grateful for the guidance, mentorship, and support I have received throughout the process of completing my thesis. This academic journey has been made possible with the invaluable contributions of several individuals, and I would like to express my appreciation to each of them.

I want to thank Dr. Ir. M. Ottavi for being willing to supervise this thesis. Thank you for your insightful expertise, advice and the opportunity to work under your guidance. I want to thank Bruno Endres Forlin for his role as my daily supervisor. Bruno, your patience in answering my numerous questions and your support have been invaluable throughout this process. Both Bruno and Marco introduced me to the academic world and guided me in the publication of an academic paper, an achievement of which I am incredibly proud.

I would like to extend my gratitude to Prof. Dr. Ir. A.B.J. Kokkeler and Dr. Ir. N. Alachiotis for their roles as members of my graduation committee. Thank you for your willingness to serve as evaluators through the trajectory of my thesis.

The graduation committee consists of the following members:

- Dr. Ir. M. Ottavi (University of Twente & University of Rome Tor Vergata)

- Dr. Ir. N. Alachiotis (University of Twente)

- Prof. Dr. Ir. A.B.J. Kokkeler (University of Twente)

- B. Endres Forlin (University of Twente)

Lastly, I extend my appreciation to you, the reader, for dedicating your time to read my thesis.

## Abstract

Highly reliable and customizable micro-processors are critical enablers for future intelligent space platforms. From an architectural point of view, the RISC-V architecture is the current best option for adaptability, with its modular ISA and a multitude of contributors. To implement such a processor at a low price range, companies are looking at reprogrammable Field-Programmable Gate Arrays (FPGAs), which can extend the mission lifetime. SRAM FPGAs are known to be susceptible to low Linear Energy Transfer Single-Event Upsets (SEUs) in the configuration memory, Flash FPGAs on the other hand, are in general immune to such errors.

This thesis performs for the first time characterization of the open-core NE-ORV32, a lightweight yet representative RISC-V SoC, and provides insights into the tradeoffs of protection mechanisms against neutron-induced SEUs when this core is implemented in a Flash-based FPGA. The Unmodified core is compared against an ECC-protected version and a register-level Triple Modular Redundancy (TMR) with an Error Correction Code (ECC) version. All versions execute the CoreMark benchmark.

The Unmodified NEORV32 instances mainly experienced exceptions arising from Single Event Upsets (SEUs) that affected stored pointers in the data memory. These altered pointers, when employed as addresses, resulted in Load and Store exceptions, stemming from the pointers now residing outside the valid memory range. The incorporation of ECC swiftly mitigated these disparities and reduced Store and Load exceptions to zero. Introducing TMR on the Flip-Flop level further advanced the outcome by eliminating all exceptions, including those tied to Illegal instructions. These Illegal instructions are likely the fallout of SEUs influencing control logic, culminating in Single-Event Functional Interrupts (SEFIs). \_\_\_\_\_

# Contents

| A  | cknov | vledgei                                        | ments                                                      | iii |  |  |  |  |  |  |  |

|----|-------|------------------------------------------------|------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| AI | ostra | ct                                             |                                                            | v   |  |  |  |  |  |  |  |

| Li | st of | acrony                                         | ms                                                         | xi  |  |  |  |  |  |  |  |

| 1  | Intro | oductio                                        | n                                                          | 1   |  |  |  |  |  |  |  |

|    | 1.1   | Motiva                                         | ation                                                      | 3   |  |  |  |  |  |  |  |

|    | 1.2   | Resea                                          | rch goal                                                   | 4   |  |  |  |  |  |  |  |

|    | 1.3   | Repor                                          | t organization                                             | 4   |  |  |  |  |  |  |  |

| 2  | Вас   | kgroun                                         | d                                                          | 5   |  |  |  |  |  |  |  |

|    | 2.1   | Single                                         | Event Effects                                              | 5   |  |  |  |  |  |  |  |

|    |       | 2.1.1                                          | SEE causes                                                 | 5   |  |  |  |  |  |  |  |

|    |       | 2.1.2                                          | Physical origins of SEU                                    | 7   |  |  |  |  |  |  |  |

|    |       | 2.1.3                                          | Effects of SEEs                                            | 8   |  |  |  |  |  |  |  |

|    |       | 2.1.4                                          | Architecturally Correct Execution (ACE)                    | 10  |  |  |  |  |  |  |  |

|    |       | 2.1.5                                          | Architectural Vulnerability Factor (AVF)                   | 12  |  |  |  |  |  |  |  |

|    |       | 2.1.6                                          | Metrics                                                    | 13  |  |  |  |  |  |  |  |

|    | 2.2   | 2.2 Redundancy techniques                      |                                                            |     |  |  |  |  |  |  |  |

|    |       | 2.2.1                                          | Physical Redundancy                                        | 14  |  |  |  |  |  |  |  |

|    |       | 2.2.2                                          | Temporal Redundancy                                        | 15  |  |  |  |  |  |  |  |

|    |       | 2.2.3                                          | Information Redundancy                                     | 15  |  |  |  |  |  |  |  |

|    | 2.3   | RISC-                                          | V and FPGA Integration for Single Event Effects Mitigation | 21  |  |  |  |  |  |  |  |

|    |       | 2.3.1                                          | RISC-V Instruction Set Architecture                        | 21  |  |  |  |  |  |  |  |

| 3  | Rela  | ated Wo                                        | ork                                                        | 23  |  |  |  |  |  |  |  |

| 4  | NEC   | DRV32                                          |                                                            | 27  |  |  |  |  |  |  |  |

|    | 4.1   | NEOR                                           | V32 Processor & CPU                                        | 27  |  |  |  |  |  |  |  |

|    | 4.2   | 2 RISC-V Standard Extensions Configurability 2 |                                                            |     |  |  |  |  |  |  |  |

|    | 4.3   | Pipelir                                        | 1е                                                         | 29  |  |  |  |  |  |  |  |

|   | 4.4<br>4.5<br>4.6 | Memory Access29Execution safety31Wishbone interface32        |

|---|-------------------|--------------------------------------------------------------|

| 5 | NEC               | RV32 Implementation 35                                       |

|   | 5.1               | Target Device                                                |

|   | 5.2               | Unmitiaged NEORV32 implementation                            |

|   |                   | 5.2.1 Memory access                                          |

|   |                   | 5.2.2 AHBL-Wishbone Bridge                                   |

|   | 5.3               | Fault-tolerant enhancements                                  |

|   |                   | 5.3.1 Design of Hsiao Encoder & Decoder                      |

|   |                   | 5.3.2 ECC Implementation                                     |

|   |                   | 5.3.3 TMR implementation                                     |

|   |                   | 5.3.4 FPGA resource usage                                    |

|   |                   | 5.3.5 Power Estimation using Microsemi's Smart Power Tool 48 |

|   | 5.4               | Testing of the Fault-Tolerant adjustments                    |

| 6 | Neu               | tron Beam Experiment 53                                      |

|   | 6.1               | Experimental setup                                           |

|   | 6.2               | Software                                                     |

|   | 6.3               | Error Model                                                  |

|   | 6.4               | Characterization Results                                     |

| 7 | Disc              | ussion 61                                                    |

|   | 7.1               | Implications of findings                                     |

|   |                   | 7.1.1 Unmodified                                             |

|   |                   | 7.1.2 ECC-enhanced                                           |

|   |                   | 7.1.3 ECC+TMR 64                                             |

|   | 7.2               | Program analysis                                             |

|   |                   | 7.2.1 Affected functions                                     |

|   |                   | 7.2.2 Vulnerability Factor                                   |

|   |                   | 7.2.3 CoreMark Linked List Algorithm                         |

|   |                   | 7.2.4 Analysis of the crash traces                           |

|   | 7.3               | Summary                                                      |

| 8 | Sim               | ulation 73                                                   |

| • | 8.1               | Simulation setup                                             |

|   | 8.2               | Fault injection strategy                                     |

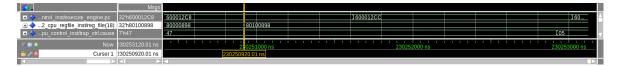

|   | 8.3               | Manual injected faults for PC value 0x600012cc               |

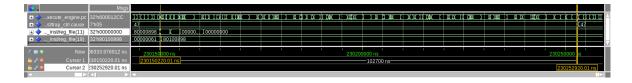

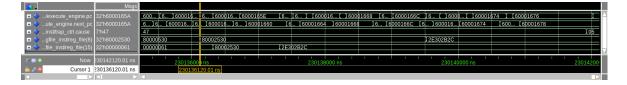

|   | 8.4               | Manual injected faults for PC value 0x60001676               |

|   |                   | ,                                                            |

|    | 8.5   | Summary                      | 78              |

|----|-------|------------------------------|-----------------|

| 9  |       | clusions and recommendations | <b>81</b><br>83 |

| Re | ferer | nces                         | 85              |

#### Appendices

#### Α

|     |                                | 91 |

|-----|--------------------------------|----|

| A.1 | Assembly functions             | 91 |

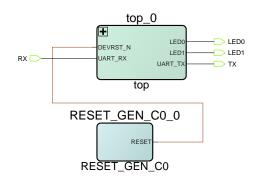

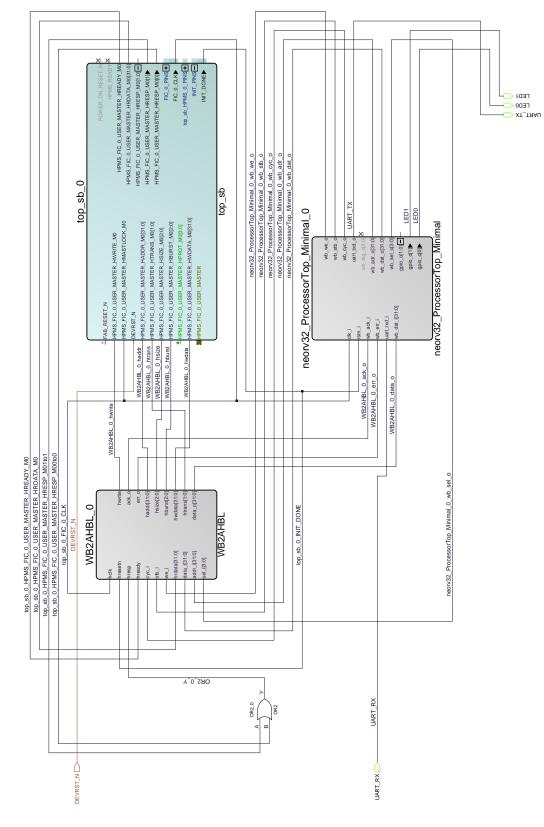

| A.2 | Top-level design in Libero SoC | 95 |

| A.3 | FPGA resources                 | 96 |

| A.4 | Parity check matrices          | 97 |

# List of acronyms

| Architecturally Correct Execution        |  |  |  |  |  |

|------------------------------------------|--|--|--|--|--|

| Artificial Intelligence                  |  |  |  |  |  |

| Arithmetic Logic Unit                    |  |  |  |  |  |

| Application-Specific Integrated Circuits |  |  |  |  |  |

| Architectural Vulnerability Factor       |  |  |  |  |  |

| Block RAM                                |  |  |  |  |  |

| Convolutional Neural Networks            |  |  |  |  |  |

| Commercial Off-The-Shelf                 |  |  |  |  |  |

| Cyclic Redundancy Check                  |  |  |  |  |  |

| Direct Memory Access                     |  |  |  |  |  |

| Data Memory                              |  |  |  |  |  |

| D-type Flip-Flop                         |  |  |  |  |  |

| Dual Modular Redundancy                  |  |  |  |  |  |

| Detected Unrecoverable Error             |  |  |  |  |  |

| Error-Correction Code                    |  |  |  |  |  |

| Error-Detecting Code                     |  |  |  |  |  |

| Eureopean Space Agency                   |  |  |  |  |  |

| First-Level Dynamically Dead             |  |  |  |  |  |

| Failure in Time                          |  |  |  |  |  |

| Field-Programmable Gate Array            |  |  |  |  |  |

| Pulse-Width Modulation                   |  |  |  |  |  |

| Hardware Performance Monitors            |  |  |  |  |  |

| Integrated Circuit                       |  |  |  |  |  |

| Intellectual Property                    |  |  |  |  |  |

|                                          |  |  |  |  |  |

| ISA    | Instruction Set Architecture                       |

|--------|----------------------------------------------------|

| LET    | Linear Energy Transfer                             |

| LUT    | Lookup Table                                       |

| LSB    | Least Significant Bit                              |

| MBU    | Multiple Bit Upset                                 |

| MEBF   | Mean Execution Between Failures                    |

| MSS    | Microcontroller Subsystem                          |

| MTBF   | Mean Time Between Failure                          |

| MTTF   | Mean Time to Failure                               |

| MWBF   | Mean Workload Between Failures                     |

| NMR    | N-Modular Redundancy                               |

| PC     | Program Counter                                    |

| PVF    | Program Vulnerability Factor                       |

| RTL    | Register Transfer Level                            |

| SDC    | Silent Data Corruption                             |

| SEB    | Single Event Burnout                               |

| SECDED | Single-Error Correcting and Double-Error Detecting |

| SEC    | Single Error Correcting                            |

| SED    | Single Error Detecting                             |

| SEE    | Single Event Upset                                 |

| SEFI   | Single Event Functional Interrupt                  |

| SEGR   | Single Event Gate Rupture                          |

| SEL    | Single Event Latchup                               |

| SEMBU  | Single Event Multiple Bit Upset                    |

| SER    | Soft Error Rate                                    |

| SET    | Single Event Transient                             |

| SEU    | Single Event Upset                                 |

| SPI    | Serial Peripheral Interface                        |

| SRAM   | Static RAM                                         |

| SoC    | System on Chip                                     |

| TDD    | Transitively Dynamically Dead                      |

\_\_\_\_\_

- **TMR** Triple Modular Redundancy

- TRL Technology Readiness Level

- VCD Value-Change Dump

- **WDT** Watchdog timer

- eNVM Embedded Non-Volatile Memory

\_\_\_\_\_

### Chapter 1

### Introduction

In recent years, there is an increasing interest in Artificial Intelligence (AI) by the entire aerospace community [1]. For example, the communication delay between Mars and Earth could range from 6.5 to 44 minutes, to enable such a mission, individual space entities need autonomous decision-making abilities. Nevertheless, the majority of tasks performed by processors within space data systems primarily involve non-demanding control and housekeeping operations. Consequently, facilitating more resource-intensive tasks, such as running AI algorithms on embedded systems in space, necessitates a fundamental shift in the design of space-grade processors. This transformation is particularly crucial given that processors on satellites frequently operate under stringent power constraints.

The aerospace industry has highlighted the limitations of existing space-grade computing systems. Full rad-hard processors, which have hardening in both silicon process and microarchitecture, typically lag more than a decade behind their commercial counterparts in terms of performance, because of their niched-size market. Unfortunately, this gap is widening every year [2]. These architectures are built upon the Sparc V8 Instruction Set Architecture (ISA), which was initially introduced in 1992. Despite the decline of SPARC processors in terrestrial applications, they continue to be a prominent choice for ongoing and upcoming missions in the space sector, although these systems heavily depend on outdated architectures. In addition to the inadequate computing power for AI tasks, this persistence has also led to challenges in sourcing developers with expertise in these specific technologies.

Given these circumstances, opting for an architecture that provides a flourishing software environment and ISA extensions, like RISC-V, can become highly beneficial. Embracing the RISC-V architecture offers a multitude of benefits to the space sector. The Eureopean Space Agency (ESA) believes that the utilization of RISC-V presents the opportunity to leverage an expanded and robust software ecosystem in the years to come [2]. This prospect holds particular importance for essential functions such as the maintenance of the software toolchain. Furthermore, the in-

troduction Of RISC-V in space will contribute to providing a range of alternatives to proprietary solutions. Open standards allow designers to access multiple Intellectual Property (IP) sources or even create their own, resulting in a diverse ecosystem of innovation and competition. This is of particular significance as concerns continue to mount regarding monopolistic positions within the embedded market [3], [4], as well as the potential impact of sanctions and the desire for greater independence in the product chain. In addition, the RISC-V ISA is divided into different standard extensions, each targeting specific functionalities, covering low-end to high-performance applications, such as AI. RISC-V's modular design enables engineers to tailor the processor's architecture to meet these requirements more effectively.

To effectively assess the suitability of a RISC-V processor for space applications, a dedicated target platform is essential, which can take the form of either an Application-Specific Integrated Circuits (ASIC) or Field-Programmable Gate Array (FPGA). The advantages of employing an FPGA include its cost-effectiveness and the ability to be reprogrammed. With satellite operational lifetimes extending well over a decade, exceeding the validity of existing telecom standards, the demand for in-flight re-programmability becomes increasingly critical [5]. If software-based solutions are not viable, Repgrogammable FPGAs (RFPGA) could arise as the only method to address this need. The objective of the Heinrich Hertz (H2Sat), launched in 2018, is to validate new hardware, software and communication technologies in space, aimed at addressing the ever-evolving landscape of telecommunication standards [6]. The transponder of this satellite, integrated with an in-flight reconfigurable FPGA-based module, will possess the capability to receive updates while in-flight, allowing for adaptations to new telecommunication standards as they are introduced.

Utilizing Commercial Off-The-Shelf (COTS) electronic components offer an attractive advantage over their Radiation Tolerant or Hardened counterparts, primarily in terms of performance enhancement [7]. In fact, the adoption of COTS devices is often advocated as the optimal approach to meet the escalating performance demands of space applications [8]. However, it is important to acknowledge that COTS devices are more susceptible to external disturbances, such as radiation, owing to their lower power consumption and faster switching characteristics. In the challenging space environment, electronics are subjected to diverse forms of radiation, containing high-energy particles. One particular concern is the occurrence of Single Event Upsets (SEUs), wherein ionizing radiation impacts a memory cell, inducing a change within it. This alteration can lead to bit-flips. One of the most effective strategies for mitigating these effects involves introducing redundancy at the Register Transfer Level (RTL).

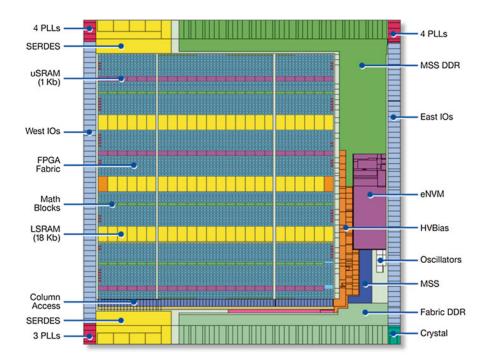

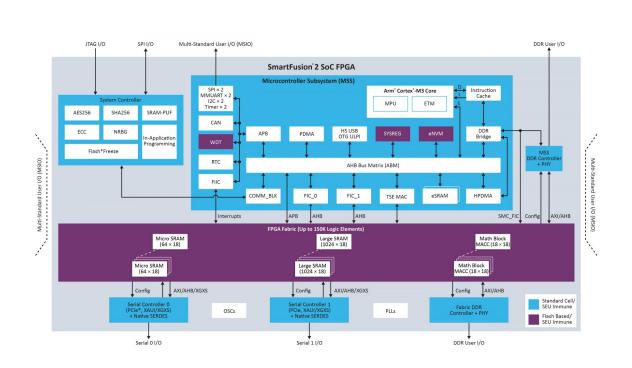

FPGAs come in two primary types: SRAM-based and Flash-based, each offering unique benefits. SRAM-based FPGAs employ Static RAM (SRAM) cells for

#### 1.1. MOTIVATION

configuration, enabling high performance and rapid reconfigurability. However, they are susceptible to SEUs that can induce bit flips in the configuration memory, leading to malfunctions and unpredictable behaviour. In contrast, Flash-based FPGAs are notably well-suited for space applications due to their immunity to configuration memory upsets and low power consumption. Despite this advantage, certain components within Flash-based FPGAs, like Block RAMs (BRAMs) and D-type Flip-Flops, remain vulnerable to SEUs. Thus, incorporating redundancy into the design becomes necessary even for Flash-based FPGAs.

Future space could benefit from these new developments, provided that research is done to satisfy the stringent requirements in space, especially in terms of fault tolerance and assessing of Technology Readiness Level (TRL) for COTS devices. The process of testing and certifying novel cores and platforms before their deployment in space is a crucial step in ensuring the success and safety of space missions. Subjecting cores and platforms to simulated space environments on Earth helps to uncover any vulnerabilities and assess the TRL. A powerful approach to replicating the space environment involves the usage of beam experiments. Through such experiments, the cross-section of devices can be estimated under conditions that closely resemble the space environment, achieved by exposing the device to accelerated particle fluxes.

#### 1.1 Motivation

In the ever-evolving landscape of the space sector, the imperative to embrace COTS devices for space applications has grown exponentially. Building upon the challenges and opportunities outlined in the introduction, this research addresses a critical research gap in the domain of space-grade processors. While substantial progress has been made in the domain of soft cores implemented in SRAM-based FPGAs, a significant research gap exists in the utilization of Flash-based FPGAs, despite their immunity to configuration memory upsets and lower power consumption.

In light of these considerations, this research attempts to delve into two corresponding domains. Firstly, it seeks to deepen our comprehension of the behavioural dynamics of Flash-based FPGAs when subjected to neutron radiation. This aims to unlock insights into the resilience and adaptability of Flash-based FPGAs in the hostile space environment.

Concurrently, this study undertakes the task of exploring the viability of integrating open-source RISC-V cores into a Flash-based FPGA. By doing so, the research tries to match the complexity of fault-tolerant enhancements with the cutting-edge capabilities of RISC-V architecture. The main driving force behind this thesis is to contribute to the new era of space. By investigating the complex behaviours of Flash-based FPGAs when exposed to radiation and aligning them with the reliability of RISC-V cores, this study aims to make a substantial contribution to the progress of aerospace technology.

#### 1.2 Research goal

The previous section has highlighted the importance of fault-tolerant processors. To investigate this issue, this thesis aims to achieve the following research goals:

Investigate different trade-offs between area, power, performance, and resilience for errors in different techniques of fault tolerance in a soft processor implemented on a Flash-based FPGA, and perform a radiation test to measure the performance of the redundancy techniques.

This goal can be achieved by answering the following research questions:

- RQ1: How do different fault tolerance techniques impact the trade-off between area, power, and performance in a soft processor implementation on a Flash-based FPGA?

- RQ2: What is the resilience performance of different fault tolerance techniques in the presence of errors, particularly radiation-induced faults, in a soft processor implemented on a Flash-based FPGA?

#### 1.3 Report organization

This thesis aims to provide a comprehensive analysis of the radiation resilience of Flash-based FPGA with a soft RISC-V core through the exploration of eight key chapters. The remainder of this report is organized as follows. In chapter 2, the groundwork is provided by providing an overview of the necessary background. In Chapter 3, the related work about radiation tests of FPGAs and Asics is presented. In chapter 4, the chosen soft-core and its architecture are presented.

The implementation of this softcore on the chosen FPGA is explored in chapter 5. The setup for the radiation beam experiment and the results of this experiment are shown in Chapter 6. Chapter 7 provides a discussion of the conducted experiment. In chapter 8 the possible exception causes presented in the Discussion are validated through an RTL simulator. Lastly, in Chapter 9, conclusions and recommendations are given.

### **Chapter 2**

# Background

The current Integrated Circuit (IC) technology is vulnerable to Single Event Upset (SEE) caused by particle strikes. These SEEs can influence the functionality of a chip or the computational results, therefore there is a need for fault-tolerant in mission-critical applications, like avionics, space or medical applications. This chapter gives an overview of different forms of SEEs. In addition, this chapter will present common redundancy techniques to mitigate the errors caused by SEEs. Lastly, the RISC-V ISA will be introduced as the target platform.

### 2.1 Single Event Effects

The effects of subatomic radiation particles on ICs are frequently referred to as Single Event Upsets (SEEs). These SEEs can lead to randomly appearing glitches in electronic errors resulting in annoying system responses or catastrophic system failures. Due to the IC devices with higher density and smaller feature sizes, these devices are more vulnerable to SEEs. Smaller feature sizes, result in faster processing and also require a smaller quantity of electrical charge. Because the charges have been decreased, these charges can be generated in the IC device by the passage of cosmic rays or alpha particles.

#### 2.1.1 SEE causes

Satellites in geosynchronous orbit and corresponding regions outside Earth's radiation belts experience upsets due to heavy ions from either cosmic rays or solar flares [9]. The cosmic ray heavy ion flux has approximately 100 particles/cm2 per day. For very sensitive devices this can result in daily upsets. Cosmic rays consist of mostly protons, but also alpha particles and heavy ions, they mainly originated outside the solar system. The solar particles come from the sun and are high-energy protons and heavy ions. Upsets can also occur within the proton radiation belts. The Van Allen belts are two vast regions of intense radiation that encircle the Eart. It is named after the scientist James Van Allen who discovered the belts in 1958. These belts consist of charged particles, primarily electrons and protons. These are trapped by the magnetic field of the Earth, they surround our planet like concentric doughnut-shaped zones. The inner belt is closer to the Earth, while the outer belt is further from Earth, reaching into a region where satellites orbit. The outer belt consists mainly of high-energy electrons and is located 13,000 to 60,000 kilometres from sea level. The lower belt lies 1,000 km to 12,000 km above Earth and consists mainly of high-energy protons. The outer belt affects satellites and the lower belt affects high-altitude aircraft.

The cosmic rays in space and those reaching Earth's atmosphere are similar in their origin and general characteristics, but there are some differences between them. When cosmic rays interact with Earth's atmosphere, several factors come into play that influence their behaviour and composition. The atmosphere provides shielding, it reduces the intensity and energy of cosmic rays reaching the surface compared to those in space. The intensity and energy spectrum of cosmic rays varies with altitude. At a higher level in the atmosphere, there is less atmospheric shielding, therefore the cosmic ray flux is generally higher at higher altitudes. Because cosmic rays penetrate the atmosphere, there is a chain of nuclear reactions that produce high-energy neutrons and protons. At 12,000 kilometres feet altitude and 45 degrees latitude, there are 6000 neutrons per square centimetre. Highenergy cosmic rays and solar particles react with the upper atmosphere generating high-energy protons and neutrons that shower to the ground. Neutrons are particularly troublesome because they are able to penetrate a concrete wall. This effect depends on both the latitude and altitude.

The problems of radiation were already discovered in 1962. During the period from 1962 to 1970, the initial satellite electronics showed unreliability, requiring the incorporation of significant redundancy [10]. The major satellite problem was differential satellite charging in the solar wind, which resulted in noise and arcing between satellite modules. Furthermore, data transmission to Earth suffered from high levels of noise, making it difficult to distinguish electronic soft failures from transmission errors. To address this, these transmissions were divided into smaller data streams accompanied by parity checks and handshaking procedures.

There are more sources of radiation besides cosmic rays, solar particles and the Van Allen belts. Package material of a chip can obtain radioactive isotopes which decay, causing alpha particles right on the device. By carefully selecting the materials, this cause can be greatly reduced. Besides space and avionics, there also exist radiation damage sources on Earth. For instance, nuclear reactors need sensors

and control circuits. Particle accelerators also need electronics for controlling and detector devices. In 1978, the cause of the errors in Intel's 2107 series 16Kb DRAM was found. The problem of trace radioactivity in the memory packaging materials was discovered. A new factory was built on the Green River in Colorado due to the large increase in demand for LSI ceramic packaging in the 1970s. However, this factory was built downstream from the tailings of an old uranium mine. The ceramic LSI packaging was contaminated due to the factory's utilization of water containing a significant amount of radioactive elements [10].

#### 2.1.2 Physical origins of SEU

SEUs can be caused by charge deposition or by charge collection. Firstly **charge deposition** will be explained. There are two main ways in which ionizing radiation causes charge release in a semiconductor device: direction ionization caused by the particle itself, and ionization caused by secondary particles generated through nuclear reactions between the particle and the semiconductor device. Both mechanisms result in the malfunctioning of the integrated circuits.

**Direct Ionization**: When an energetically charged particle moves through semiconductor material it frees electrons along its path as it loses energy. The particle is at rest when all its energy is lost. The total path length of the travelled particle is referred to as the particle's range. The Linear Energy Transfer (LET) describes the energy loss per unit path length of a particle as it passes through the material [11]. LET has units of  $MeV/cm^2/mg$  because the energy loss per distance (MeV/cm) is normalized by the density of the target material ( $mg/cm^3$ ). Therefore the LET can be used for different targets. A LET of 97  $MeV/cm^2/mg$  corresponds to a charge disposition of 1 pC/um. Direction ionization is the primary charge deposition mechanism for upsets by heavy ions. Lighter particles such as protons do not usually produce enough charge by direct ionization to cause upsets in memory circuits. However, because SEE devices are becoming more susceptible, upsets by protons may occur.

**Indirect ionization**: Protons and neutrons can both produce significant upset rates due to indirect mechanisms. A high-energy proton or neutron can cause several nuclear reactions when it enters the semiconductor lattice. These reaction products can deposit energy along their path by direct ionization because these particles are much heavier than the original proton or neutron.

SEUs can also be caused by **charge deposition**. Usually, the most sensitive region is the *reverse-biased* p/n *junction*. These regions can very efficiently collect the particle-induced charge through drift processes, resulting in a transient current at the junction. This current spike has two components: a short component that

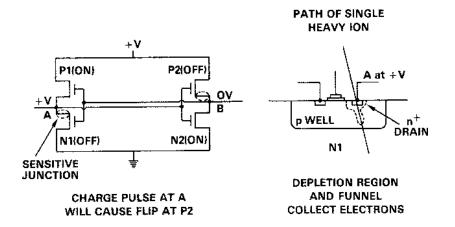

#### SINGLE EVENT UPSET MECHANISM CMOS STATIC RAM

lasts for hundreds of picoseconds after the ion strike and a delayed component that may last hundreds of nanoseconds [9]. Figure 2.1 shows an **SRAM** cell in a valid logic hold state on the left. On the right, the reverse-biased drain N1 is hit with an ion strike. The inverter which is formed by P1 and N1, with input node B held low, and output node A is pulled to VDD by P1. The inverter formed by P2 and N2 has input node A forced high, therefore output node B is pulled low by N2. If an ion strikes and enough charge is collected at the drain of N1, which lowers the potential below the threshold of P2 and N2, the logic stored in the SRAM cell may flip.

When a charged particle, like an ion from radiation, interacts with the floating gate transistor of a **Flash** cell, it needs a significantly higher amount of energy to actually change the stored charge in the floating gate. This is because the charge is stored in the form of trapped electrons, which are very well insulated.

#### 2.1.3 Effects of SEEs

SEEs happen in space, in avionics and even on Earth. When it comes to avionics systems, the main focus is on the neutrons generated by high-energy particles as they penetrate the atmosphere. While approximately 20% of atmospheric particles are protons, their impact is comparable in nature [9]. These SEEs can manifest in the following ways:

1. **SEU**: A change in the state of the the memory. The susceptibility depends on the type of memory, SRAM is more susceptible than Flash memory.

- 2. Single Event Multiple Bit Upset (SEMBU): a single particle strike, that causes multiple changes in memory. An SEU with multiple bits changed.

- Single Event Functional Interrupt (SEFI): unexpected output results that are produced by SEUs originated in the device, for instance, SEUs in the configuration memory of an FPGA [13].

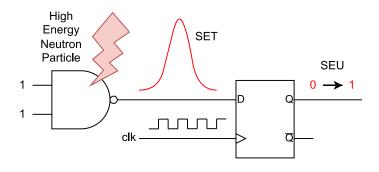

- 4. **Single Event Transient (SET)**: A voltage pulse in combinational logic which can result in erroneous results if captured by a memory cell at the correct moment.

- 5. **Single Event Latchup (SEL)**: a short circuit which disrupts the functioning of the IC, it could lead to permanent destruction.

- 6. **Single Event Burnout (SEB)**: A destructive burnout of the drain-source in a power MOSFET.

- Single Event Gate Rupture (SEGR) caused by high-energy particles damaging the gate oxide of MOS transistors, leading to malfunction or permanent failure.

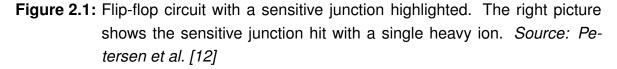

SEL, SEB and SEGR are destructive forms of SEEs, which means they involve the physical destruction or irreversible changes in the device's component. On the other hand, Non-Destructive Single Event Effects refer to temporary or transient disruptions in the regular operation of an electronic device. SEUs, SEMBUs and SETs are forms of non-destructive SEEs and will be the focus of this thesis. An example of a particle hitting a memory cell can be seen in figure 2.2. A particle has hit a 16-bit word and depending on the technology this can result in a SEU or SEMBU.

Figure 2.2: Example of a 16-bit memory array hit by an ionizing particle

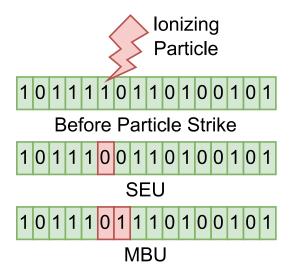

Figure 2.3: A SET in a combinational logic cell resulting in a SEU

If a particle hits a sensitive node of a logic gate cell it produces a SET [14]. This SET can propagate through the logic data path and be captured by a flip-flop or latch. The duration of the SET pulse is important since it must be sufficiently long to ensure its capture and precisely timed to be captured at the correct moment. Once the SET is stored within a memory cell, it transforms into a Single Event Upset (SEU). An illustration of this concept can be seen in Figure 2.3. Consider a NAND gate with both inputs set to 1, a situation that ordinarily produces an output of 0. However, an unexpected scenario unfolds when a high-energy neutron particle collides with the NAND gate. This collision generates a short voltage peak at the output of the gate. Notably, the connected D-type Flip-Flop (DFF) records this voltage wave, resulting in the transformation of what was originally a SET into a SEU.

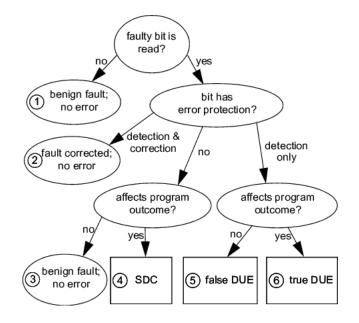

Detected errors are called Detected Unrecoverable Error (DUE), and undetected errors are called Silent Data Corruption (SDC). Not every faulty bit will result in a visible as shown in figure 2.4. A faulty bit which is never read is not classified as an error, because it does not have any effect on the outcome of the system. When a faulty bit is read and there is error detection and correction, the bit can be corrected and the faulty is not classified as an error. When the faulty bit can only be detected, the question needs to be answered if it has any effect on the program outcome. When it has no effect, it will be classified as a false DUE, otherwise as a true DUE. When there is no error detection and it does not affect the program outcome the faulty bit is classified as no error, because it is never detected. When it changes the program outcome and is not detected, the classification SDC is used.

#### 2.1.4 Architecturally Correct Execution (ACE)

Not all faults in a microarchitectural structure affect the final outcome of a program. For instance, a single-bit fault in the branch predictor will not affect the sequence or results of any committed instructions. The AVF is defined as the probability that a fault in that particular structure will result in an error [16]. So the AVF of the branch predictor is 0%. In contrast, the AVF of the program counter is effectively 100%.

Figure 2.4: Possible outcomes of a faulty bit in a microprocessor. *Source: Mukherjee et al.* [15]

The AVFs can also be calculated for storage cells. An error in a storage cell that causes a visible error in the final output of the program in the absence of error correction techniques is an ACE bit [16]. The remaining processor state bits are called un-ACE bits. A fault in an un-ACE bit will not cause a visible error. The AVF for a single-bit storage cell is simply the fraction of the time that it holds ACE bits.

The AVF of a branch predictor is 0% because the branch predictor is always un-ACE bits. All the bits in the PC are always ACE bits, resulting in an AVF of 100%. Processor bits that do not affect the committed instruction path are called **microarchitectural un-ACE bits**, examples of these are:

- 1. **Idle or Invalid State**: there exist instances in a microarchitecture when a status bit is idle or does not contain any valid information. Such data and status bits are un-ACE bits.

- Mispeculated state: a microprocessor can perform different forms of speculative operations. When these speculative operations are found to be incorrect, the bits of these incorrectly speculated operations can be classified as un-ACE bits.

- Predictor Structures: A modern microprocessor can have many predictor structures. A fault in these structures will cause a misprediction. This will affect the performance, but the execution remains correct, therefore these bits can be classified as un-ACE bits.

- 4. Ex-ACE State: are ACE bits that become un-ACE bits after their last use. This

classification contains architecturally dead values, for instance, registers, as well as architecturally invisible states.

Architectural un-ACE bits affect correct-path instruction execution, however, it does not change the output of the system. There are five sources of architectural un-ACE bits [16].

- NOP instructions: most instruction sets have NOP instructions. These NOP instructions are used for instance for aligning instructions to address boundaries or filling VLIW-style instruction templates. The only ACE bit of a NOP instruction is the bits distinguishing the NOP instruction from a non-NOP instruction.

- **Performance-enhancing instructions** non-opcode bits are un-ACE bits, because a fault there may cause the wrong data to be prefetched or may cause an invalid address, in both cases the prefetch will be ignored.

- **Predicated-false instructions** are instructions which will not be committed and discarded. Clearly, all these bits are un-ACE Bits.

- Dynamically dead instructions are those whose results are not used. Transitively

Dynamically Dead (TDD) instructions are instructions whose results are not

read by other instructions. First-Level Dynamically Dead (FDD) instructions

are instructions whose results are only read by other TDD or FDD instructions. Suppose, instruction A writes to register X1. After this write, instruction

B writes to the same register, but X1 was not read, so the output of instruction

A is not used. Therefore instruction A is a FDD instruction. FDD and TDD

instructions can be counted as ACE bits.

- **logical masking** there exist bits that do not influence the output. For instance an OR operation on specific bits with 1's.

#### 2.1.5 Architectural Vulnerability Factor (AVF)

Mukherjee et al. introduced the concept of Architectural Vulnerability Factor (AVF) and ACE analysis [16]. The AVF of a processor is the probability that a fault in this structure will result in a visible error in the program output. It is based on the concept of Architecturally Correct Execution (ACE) bits and un-ACE bits. ACE bits are needed for correct operation, while un-ACE bits are not. The definition of AVF can be found in Equation (2.1).

$$AVF_H = \frac{\sum_{n=0}^{N} (ACE \text{ m-bits in } H \text{ at cycle } n)}{B_R \times N}$$

(2.1)

The Program Vulnerability Factor (PVF) is a metric that measures the vulnerability of an architectural resource to errors [17]. The PVF is given in Equation (2.2) [17]. The difference between PVF and AVF is that PVF focuses on instructions, whereas AVF focuses on clock cycles.

$$PVF_R = \frac{\sum_{i=0}^{I} (ACE \text{ a-bits in } R \text{ at instruction } i)}{B_R \times I}$$

(2.2)

Fang et al. extended the PVF metric and created a dynamic model for predicting whether a particular fault will cause a crash. By performing fault injection they found that the majority of crashes are caused by illegal memory addressing [18]. They observed four types of exceptions resulting in crashes: Segmentation fault, Abort, Misaligned memory access and Arithmetic errors. They discovered that segmentation faults are the predominant source of crashes with a 99% average frequency and a 96% minimum frequency.

#### 2.1.6 Metrics

Both SDC and DUE rates are typically expressed in Failure in Time (FIT). One FIT specifies one failure in  $10^9$  hours, which is a billion hours. FIT rates are additive, so the FIT rate of a system can be computed by summing all the FIT rates of the components. This sum is often referred to as Soft Error Rate (SER). The Mean Time to Failure (MTTF) is often more intuitive but is not additive. MTTF is the average time before the system fails and is inversely related to FIT. A FIT rate of 10,000 is equivalent to an MTTF of:  $10^9/(10,000 * 24 * 365) = 11.42$  years.

The cross-section ( $\sigma$ ) is the standard metric to evaluate the sensitivity to radiation of a device [19]. To understand this metric, it is important to first understand flux and fluence. Flux and fluence are used to describe the radiation environment or the particle beam used for testing. Flux is the rate of particles or energy across or onto a given area. The neutron flux ( $\varphi$ ) is the number of incident particles per unit area and per unit time ( $n/(cm^{-2}s^{-1})$ ).

Fluence is a measure of the quantity of light or radiation falling on a surface, expressed in terms of either particles or energy per unit area. The neutron fluence is defined as the neutron flux integrated of a particular time period, this results in a unit of  $n/cm^{-2}$  (neutrons per centimetre squared).

The cross-section ( $\sigma$ ) is the standard metric to evaluate the sensitivity to radiation of a device [19]. The cross-section represents the radiation-sensitive area of the device. By performing a beam experiment the cross-section can be derived by dividing the number of errors by the total particle fluence. The **fluence** is the number of particles hitting the device per unit area. The cross-section is calculated with the following formula:

$$\sigma = \frac{\text{number of errors}}{\text{fluence}}$$

The Mean Time Between Failure (MTBF) of a system, is defined as the average time between two radiation-induced failures on the system continuously executing a given task. The MTBF is defined as follows:

$$\mathsf{MTBF} = \frac{1}{\sigma * \mathsf{flux}}$$

A more reliable system has a higher MTBF, which means the system can run for a longer time before experiencing a radiation-induced error. However, this metric does not take into account the workload. Therefore, the authors of [20] propose two new metrics. The Mean Execution Between Failures (MEBF), is the number of successful executions of an application between two radiation-induced failures. This value can be computed by dividing the MTBF, with the execution time t:

$$\mathsf{MEBF} = \frac{\mathsf{MEBF}}{t}$$

The author of [20] also proposes the Mean Workload Between Failures (MWBF). Every system is characterized by a workload w, which is the amount of data that needs to be processed for one execution. The MEBF can be even further generalized by multiplying with the workload.

$$\mathsf{MWBF} = \mathsf{MEBF} \ast w$$

#### 2.2 Redundancy techniques

There are two radiation-hardening techniques: at a physical or a logical level. The key to detecting and correcting errors is redundancy, a processor without redundancy cannot detect any errors. Therefore the question becomes what kind of redundancy should be used. There are three classes of redundancy: physical, temporal, and information [21].

#### 2.2.1 Physical Redundancy

Physical (or spatial) redundancy is commonly used for providing error detection. The simplest form of physical redundancy is Dual Modular Redundancy (DMR). With DMR, the module is duplicated and a comparator is added, when the output of the

| Table 2.1: Single bit majority voting for TMR |       |        |   |  |  |  |  |  |

|-----------------------------------------------|-------|--------|---|--|--|--|--|--|

|                                               | Input | Output |   |  |  |  |  |  |

|                                               | 000   | 0      | - |  |  |  |  |  |

|                                               | 001   | 0      |   |  |  |  |  |  |

|                                               | 011   | 1      |   |  |  |  |  |  |

|                                               | 111   | 1      |   |  |  |  |  |  |

modules mismatch an error has occurred. A Triple Modular Redundancy (TMR) system can be created by three modules and a voter. For a single error fault, TMR adds error recovery. A general redundancy scheme is N-Modular Redundancy (NMR), which for odd values of N greater than three provides better detection and protection than TMR. In table 2.1 an example of a single-bit majority voting for TMR is shown.

Physical redundancy can be implemented at various granularities. At a coarse level, the entire processor or core can be replicated. For a more finer grain, the ALU or a register can be triplicated. For a finer grain, TMR can be applied on a flip-flop level. The primary cost of physical redundancy is the hardware cost and power and energy consumption. TMR uses three times more hardware compared to an unprotected system.

#### 2.2.2 Temporal Redundancy

Temporal redundancy can be achieved by performing an operation twice or more after each other and comparing the result afterwards. Therefore, the total time is doubled, but the hardware remains the same in contrast to the physical redundancy. However, the energy consumption is doubled, because twice as much work is performed. This redundancy can be implemented in both hardware and software. Pipelining can be used to reduce the latency, however, the throughput will still be penalized. Note that this strategy only protects the pipeline against SETs. De Sio et al. propose a software solution for replicating data and computations to cope with SEUs affecting the memory where the binary is stored [22].

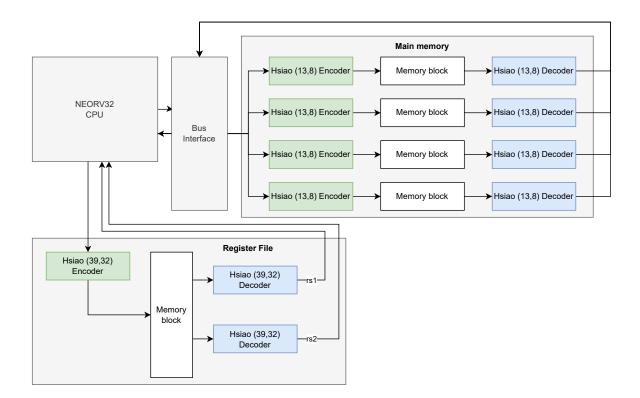

#### 2.2.3 Information Redundancy

The idea of information redundancy is adding redundant bits to a dataword to detect when an error has occurred. Error-Correction Code (ECC) detect and can sometimes correct single or multiple-bit errors. Single Error Correcting (SEC) codes can detect and correct one single-bit in a *n*-bit codeword. An Error-Detecting Code (EDC) checks the data and the parity bits for errors. There also exist Single-Error Correcting and Double-Error Detecting (SECDED) codes which can detect and correct a single bit and are able to detect double-bit errors. The codeword bits n are constructed by adding parity bits p to the dataword bits m.

$$n = m + k$$

The distance between any two codewords is called the *Hamming Distance (HD)*. The Hamming Distance is denoted as dist(x, y) and is equal to the number of places where they differ. For instance:

$$dist(1001, 1000) = 1, \ dist(1100, 1010) = 2$$

The *hamming weight* of a vector  $x = x_1x_2...x_n$  is the number of  $x(i) \neq 0$  and is defined as wt(u). For instance:

$$wt(1000) = 1, wt(1011) = 3$$

The *minimum distance* of codeword, is the minimal Hamming distance between its codewords. The distance of a codeword can be computed with the Hamming weight:

$$dist(x, y) = wt(x - y)$$

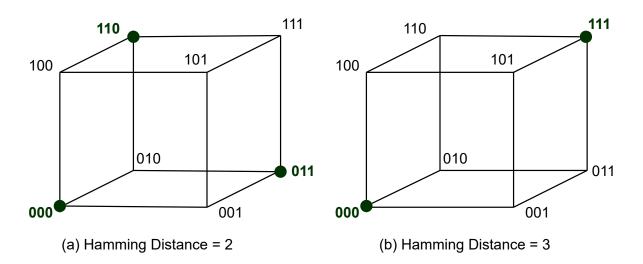

The minimum Hamming Distance of a block code is equal to the minimum Hamming weight among all non-zero codewords. Figure 2.5 shows two different Hamming Distances for the same codeword. Figure 2.5 (a) shows a Hamming Distance of 2, every axis represents a single bit in the three-bit codeword. With a Hamming Distance of 2, there are three valid codewords. These codewords both share a Hamming Distance of 2. Figure 2.5 (b) shows a Hamming Distance of 3, now there are only 2 valid options, namely 000 and 111.

The minimum distance tells something about the error detection and correction ability. A minimum Hamming Distance of 2, belongs to a Single Error Detecting (SED) code, for instance, Parity encoding. With this code, an error can be detected, but cannot be corrected, because the position of the invalid bit is unknown. With a Hamming Distance of 3 a SEC, code can be realized, which can correct a single-bit error. An example of a SEC code already discussed is TMR. With TMR a single bit is replicated, and this is also shown in Figure 2.5 (b). There are only 2 valid words with a codeword of 3 bits. Another famous SEC code is the Hamming encoding. With a minimum distance of 4, a SECDED code can be achieved, for instance, Extended Hamming.

Figure 2.5: Hamming Distance 2 (a) and 3 (b) for a 3-bit codeword. The codewords marked with green are valid codewords.

#### Parity encoding

The simplest and most common form of EDC is parity. Parity adds one parity bit to a data word to convert it to a codeword. The parity bit indicates whether the amount of 1's is even or odd. When the number of 1's is even, the parity bit is 0, otherwise the parity bit is 1. Parity has a Hamming Distance of 2, resulting in single-bit error detection. An illustration of HD=2 with an example can be seen in Figure 2.5 (a)). Consider a valid codeword '110'. If a Single Event Upset (SEU) occurs, affecting the first bit, it results in '010'. If the SEU affects the second and third bits, we get '100' and '111' as possible outcomes. Importantly, these altered codewords are invalid, this invalidity allows the fault detection.

While parity-based EDC can detect single-bit errors, it cannot correct them. For instance, '010' can be connected to three valid codewords, making it impossible to determine which one it was originally.

#### Hamming

The Hamming code was invented by Richard W. Hamming in 1950 to address errors caused by punched card readers. This code is considered perfect because it achieves the highest possible efficiency for codes of their block length and minimum distance, which is three. Unlike simple parity codes, Hamming codes have the ability to not only detect but also correct errors. The extended Hamming code, on the other hand, incorporates an additional parity bit, resulting in a Hamming Distance of four. This expanded capability allows the decoder to differentiate between scenarios where only one bit has been corrupted and cases where two bits have been corrupted. Consequently, extended Hamming codes are known as SECDED codes.

| Bit number      | 1  | 2  | 3  | 4  | 5  | 6  | 7  |  |

|-----------------|----|----|----|----|----|----|----|--|

| Transmitted bit | p1 | p2 | d1 | р3 | d2 | dЗ | d4 |  |

| p1              | Т  | F  | Т  | F  | Т  | F  | Т  |  |

| p2              | F  | Т  | Т  | F  | F  | T  | Т  |  |

| p3              | F  | F  | F  | Т  | Т  | Т  | Т  |  |

**Table 2.2:** Hamming (7.4) Code: Parity coverage of the transmitted bits

Table 2.3: Hamming (7,4) Code: Parity coverage of the data bits

|    | d1 | d2 | dЗ | d4 |

|----|----|----|----|----|

| p1 |    | Т  | F  | Т  |

| p2 | Т  | F  | Т  | Т  |

| рЗ | F  | Т  | Т  | Т  |

#### Hamming (7,4) Encoding & Decoding example

This example shows the encoding and decoding of Hamming (7,4). This Hamming encoding can detect and correct every single-bit error. Table 2.2 shows for every parity bit which transmitted bits are covered. For instance, parity bit  $p_1$  provides an even parity bit for the transmitted bits: 1  $(p_1)$ , 3  $(p_3)$ , 5  $(d_2)$  and 7  $(d_4)$ . Every data bit  $(d_1, d_2, d_3, d_4)$  is covered by 2 parity bits. Table 2.3 is created by removing the parity bits column from table 2.2. The parity-check matrix H is defined as table 2.2:

$$H = \begin{bmatrix} 1 & 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix}$$

The code generator matrix G is constructed as follows, rows 1, 2 and 4 of the matrix **G** correspond to the contents of Table 2.3. This table is placed at those rows because  $p_1$  is transmitted as  $b_1$ ,  $p_2$  is transmitted as  $b_2$  and  $p_4$  is transmitted as  $b_4$ . The remaining rows map the data to their position in encoded form. Therefore rows: 3,5,6 and 7 form the identity matrix. This results in the following matrix:

$$G = \begin{bmatrix} 1 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}$$

Suppose we want to transmit the message (**p**) "1001". The bits for the transmission codeword (x) can be computed by multiplying the generator matrix G with the message (**p**):

$$x = G \times p = \begin{bmatrix} 1 & 1 & 0 & 1 \\ 1 & 0 & 1 & 1 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 1 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix} \times \begin{bmatrix} 1 \\ 0 \\ 1 \\ 1 \\ 0 \\ 1 \end{bmatrix} = \begin{bmatrix} 2 \\ 2 \\ 1 \\ 1 \\ 0 \\ 0 \\ 1 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 1 \\ 1 \\ 0 \\ 0 \\ 1 \end{bmatrix}$$

Modulo 2 is taken of the product of **G** and **p** to determine the transmitted codeword  $\mathbf{x}$ . This means that "0011001" would be transmitted instead of "1001".

When no errors occur during the transmissions the received codeword  $(\mathbf{r})$  is identical to the transmitted codeword  $\mathbf{x}$ .

$$r = x$$

The receiver multiples the parity-check matrix  $\mathbf{H}$  with the received codeword  $\mathbf{r}$  to compute the syndrome vector ( $\mathbf{s}$ ). This syndrome vector indicates whether an error has occurred. When an error has occurred this syndrome vector also indicates which codeword bit is wrong.

$$s = H \times r = \begin{bmatrix} 1 & 0 & 1 & 0 & 1 & 0 & 1 \\ 0 & 1 & 1 & 0 & 0 & 1 & 1 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix} \times \begin{bmatrix} 0 \\ 0 \\ 1 \\ 1 \\ 0 \\ 0 \\ 1 \end{bmatrix} = \begin{bmatrix} 2 \\ 2 \\ 2 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \\ 1 \end{bmatrix}$$

In this case, the syndrome vector is a null vector, which means no error has occurred during the transmission. The data bits at positions (3,5,6 and 7) of the received codeword correspond to the original message "1001".

Suppose there is a single-bit error at  $b_2$ , the received codeword therefore becomes: "0111001" instead of "0011001":

$$r = x + e_5 = \begin{bmatrix} 0\\0\\1\\1\\1\\0\\0\\1 \end{bmatrix} = \begin{bmatrix} 0\\1\\0\\0\\0\\0\\1 \end{bmatrix} = \begin{bmatrix} 0\\1\\1\\1\\0\\0\\1 \end{bmatrix}$$

$$S = H \times R = \begin{bmatrix} 1 & 0 & 1 & 0 & 1 & 0 & 1\\0 & 1 & 1 & 0 & 1 & 0 & 1\\0 & 1 & 1 & 0 & 0 & 1 & 1\\0 & 1 & 1 & 0 & 0 & 1 & 1\\0 & 0 & 0 & 1 & 1 & 1 & 1 \end{bmatrix} \times \begin{bmatrix} 0\\1\\1\\0\\0\\1 \end{bmatrix} = \begin{bmatrix} 2\\3\\2 \end{bmatrix} = \begin{bmatrix} 0\\1\\0 \end{bmatrix}$$

The syndrome vector is non-zero, which means that there was an error. The value of the syndrome is the bit place where the error is, namely 2.

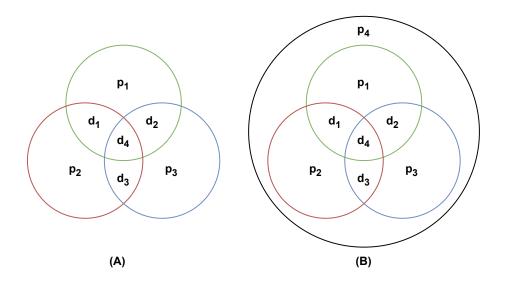

Hamming codes can also be used for detecting dual-bit errors, by adding one overall parity bit as can be seen in Figure 2.6. In this figure a fourth parity bit has been added, resulting in an extended Hamming (8,4) presentation. To decode this code, first, the overall parity bit needs to be checked. If the parity bit indicates an error, the single error correction will indicate the error location.

**Figure 2.6:** Venn diagram of the four data bits  $d_1$  to  $d_4$  and the parity bits  $p_1$  to  $p_3$

#### Hsiao

M. Y. Hsiao optimized the Hamming SEC-DED codes in 1970 [23]. The Hsiao SEC-DED code is an error correction code that introduces specific conditions for constructing the parity-check matrix.

The conditions of the **H** matrix for a SECDED code are:

- 1. There are no columns that contain only 0's.

- 2. Each column is distinct from every other column.

- 3. Each column contains an odd quantity of 1's.

- 4. The total count of 1's is minimized.

- 5. Each row in the H-matrix should have a number of 1's that is equal to or as close as possible to the average number, which is calculated as the total number of 1's in H divided by the number of rows.

The advantage of Hsiao over Hamming is that the number of 1's in the paritycheck matrix is minimized resulting in faster calculations. Another advantage is when the odd-weight column-vectors are close to the average number of 1's in a row, therefore the amount of logic gate levels can be reduced, resulting in less delay. G. Tshagharyan et al. [24] demonstrated that Hsiao is more effective in terms of logic levels and area for larger word sizes.

### 2.3 RISC-V and FPGA Integration for Single Event Effects Mitigation

In addition to implementing redundancy techniques to mitigate SEEs, another critical aspect of ensuring the reliability and robustness of digital systems lies in the choice of the processor architecture and hardware platform. This consideration becomes particularly important when targeting Field-Programmable Gate Arrays (FP-GAs), which offer flexibility and reconfigurability for various applications.

#### 2.3.1 RISC-V Instruction Set Architecture

The RISC-V processor is an open-source instruction set architecture (ISA) designed for computer processors. This instruction set is based on the Reduce Instruction Set Computer (RISC) principles, which prioritize simplicity, efficiency, and modularity in processor design. The key concept of a RISC processor is that each instruction performs only one function, for instance, copying a value from memory to a register. Compared to a complex instruction set architecture (CISC), a RISC processor might require more instructions in order to compute a particular task, but due to the simpler instructions these instructions can be executed at a higher speed.

The RISC-V project was created at the University of California, Berkeley, in 2010. In contrast to other academic designs, which are typically optimized for simplicity for teaching purposes, the designers of RISC-V intended it to be used in real-world processors.

One of the key advantages of RISC-V is its open standard, therefore anyone is able to access, use, modify and contribute to its specifications without any licensing fees or restrictions. This openness resulted in a vibrant community of developers, researchers, and companies actively contributing to the architecture's evolution. The RISC-V Foundation, a non-profit organization, manages and promotes the RISC-V ISA. Its mission is to drive the adoption of RISC-V by facilitating collaboration, providing education and support, and managing the architecture's specifications. Numerous companies, ranging from established semiconductor manufacturers and emerging startups, have embraced RISC-V and developed compatible processors and related technologies.

## **Chapter 3**

# **Related Work**

This chapter shows the related work about neutron radiation testing of FPGAs with softcores and ASICs. Neutron beam experiments of custom RISC-V soft-cores and COTS SoCs have been performed thoroughly in the literature.

The work of Wilson et al. [25] compares the neutron soft-error reliability of an unmitigated and TMR version of a Taiga RISC-v soft processor on a Xilinx SRAMbased FPGA. The TMR version showed a 33x reduction in the neutron cross section for a cost of around 5.6x resource utilization. The authors introduce two experimental designs on the Xilinx Kintex Ultrascale KU040 FPGA. One design contained 20 unmitigated processors and the other contained 20 TMR processors. The Dhyrstone benchmark was run during the neutron radiation tests. After every iteration, the checksum and iteration count were reported as the CPU status over a JTAG interface. These values were compared to a golden for correctness. The BYU BL-TMR tool was used to triplicate the Taiga processor.

Besides RISC-V there also exist literature about the LEON3. Keller et al. [26] compares a variety of mitigation techniques of the LEON3 soft processor with fault injection and neutron radiation testing. They show that fault injection can be a good way to estimate the cross-section of a design before going to a radiation test. They have tested 5 mitigation variants: an unmitigated version, TMR without scrubbing, TMR with BRAM scrubbing, TMR with CRAM scrubbing and TMR with BRAM & CRAM scrubbing. For the fault injection, the TMR & CRAM scrubbing resulted in a 27.28x improvement, by adding BRAM scrubbing the improvement was even increased to 51.30x. The numbers of the neutron radiation tests are closely related, the TMR & CRAM scrubbing resulted in a 26.94x improvement and the fully mitigated variant has an improvement of 48.85. During the test, the Dhyrstone 2.1 benchmark was run in a continuous loop. Fine-grain TMR was applied, which means that all flip-flops are triplicated.

In addition to utilizing SRAM-FPGAs for radiation tests, flash-based FPGAs have been used. Santos et al. [27] tested their own developed low-cost Riscv CPU Hard-

ened Risc-V (HARV). HARV has some basic hardening features to provide an alternative with competitive silicon and power overheads. It is a single-cycle processor and applies ECC on all internal registers and data, increasing the width by 7 bits. TMR is applied on the Arithmetic Logic Unit (ALU) and control unit. CoreMark was used as a benchmark during the radiation test. The design was implemented on the Microchip M2S010 SmartFusion2 Flash-FPGA. The authors have tested four configurations: without hardening, only hardening the processor, only hardening the memory, and hardening the processor and the memory. The latter one executed the CoreMark benchmark without errors in all 221 CoreMark executions. Each execution took 12 minutes to compute. The non-protected variant has a success rate of 73.08.

Besides FPGAs, ASICs also have been tested with neutron radiation. Dos Santos et al. investigate the error rate of a commercial RISC-V ASIC to a neutron beam [28]. They tested the GAP8 platform from GreenWaves, it has a cluster of 8 RISC-V cores. They show that code with more synchronization actions between the main core and the cluster of cores and more memory operations, for instance, FIR, have a higher DEU rate. They show that in computations for Convolutional Neural Networks (CNN) the error rate can be 3.2x higher than the average error rate. In addition, the majority of the errors (96.12%) on the CNN do not generate misclassifications.

Canizzaro et al. [29] evaluate the SEU susceptibility of two commercial RISC-V processors, the Microchip PolarFire SoC and the SiFive HiFive Unmatched, in the presence of neutron radiation. Both devices are compared with the flight-proven Xilinx Zynq-7020 system-on-chip, which has an ARM Cortex-A9 processor integrated. The ARM Cortex-A9 architecture, released in 2008, has been used in flight-proven devices such as the CHREC Space Processor (CSP) and the SHREC Space Processor (SSP). Bot CSP and SSP have performed missions in the ISS successfully. Both systems are not radiation-hardened but are fault-tolerant devices that use radhard power management and a watchdog subsystem. Both the RISC-V SoCs have parity detection for the L1 caches and SECDED and ECC available for their L2 caches. The DDR memory ECC capabilities were not enabled by the platform vendors. The ARM Cortex-A9 provide parity detection for its L1 and L2 caches, which was enabled for both memories. The ECC on the DDR memory is available but like the RISC-V boards not enabled. The EEMBC CoreMark and SHREC SpaceBench benchmarks were used to evaluate the presence of data and execution errors. CoreMark is a synthetic benchmark developed by the Microprocessor Benchmark Consortium (EEMBC) used to evaluate single-core performance. Originally, it was designed to be an improvement of the popular Dhrystone benchmark. The authors did not use CoreMark for performance but only counted the successful

execution of the benchmark. SHREC was developed by Dr Tyler Lovelly and is a suite of nine kernel benchmarks, containing matrix multiplication, addition, convolution and transposition. The datatype selection is configurable and provides parallel processing support. All the benchmarks ran on the Linux operating system, which was booted from an SD card. The PolarFire and the Unmatched had no errors in 99.70% and 99.59% of the operations. The Zynq had only 65.23% error-free operations. The PolarFire, Unmachted, and Zynq experience data errors in 0.02%, 0.03%, and 16.10% of the operations. These results and the radiation data of the following cross sections were found for PolarFire, Unmatched and Zynq:  $8.033 * 10^{-12} cm^2$ ,  $8.342 * 10^{-12} cm^2$ , and  $3.759 * 10^{-9} cm^2$ . The cross-section of the Zynq is much larger compared to the RISC-V platforms, therefore the commercial RISC-V devices have much lower SEU susceptibility compared to the flight-proven Zynq platform.

The related work in table 3.1 provides a comprehensive overview of the key elements discussed in this section. This table summarizes the tested cores, platforms, enhancements, tests and evaluations from the various research works.

| Core &        | Redu  | n-  | Test         |                 | Communication |      |       | Benchmark     |                |       |  |

|---------------|-------|-----|--------------|-----------------|---------------|------|-------|---------------|----------------|-------|--|

| Platform      | dancy | /   | 1001         |                 | 00111         |      |       | Denominaria   |                |       |  |

|               | TMR   | ECC | Neut-<br>ron | Sim-<br>ulation | Uart          | Jtag | Other | Core-<br>Mark | Dhry-<br>stone | Other |  |

| Taiga on      |       |     |              |                 |               |      |       |               |                |       |  |

| Xilinx Kintex | x     |     | х            |                 |               | x    |       |               | x              |       |  |

| Ultrascale    | ^     |     | ^            |                 |               |      |       |               | ^              |       |  |

| KU040         |       |     |              |                 |               |      |       |               |                |       |  |

| LEON3 on      | х     | х   | х            | х               |               | х    |       |               | х              |       |  |

| Xilinx KC705  | ^     | ^   | ^            | ^               |               | ^    |       |               | ^              |       |  |

| HARV on       |       |     |              |                 |               |      |       |               |                |       |  |

| Microsemi     | Х     | X   | Х            |                 | Х             |      |       | X             |                |       |  |

| M2S010        |       |     |              |                 |               |      |       |               |                |       |  |

| GreenWaves    |       |     | х            |                 |               |      | х     |               |                | x     |  |

| GAP8          |       |     | ^            |                 |               |      | ^     |               |                |       |  |

| Microchip     |       |     |              |                 |               |      |       |               |                |       |  |

| PolarFire     |       | x   | х            |                 | x             |      |       | x             |                | x     |  |

| SoC &         |       | ^   | ^            |                 | ^             |      |       | ^             |                |       |  |

| SiFive HiFive |       |     |              |                 |               |      |       |               |                |       |  |

Table 3.1: Schematic summary of the related work for radiation experiments with

FPGAs and ASICs

# **Chapter 4**

# NEORV32

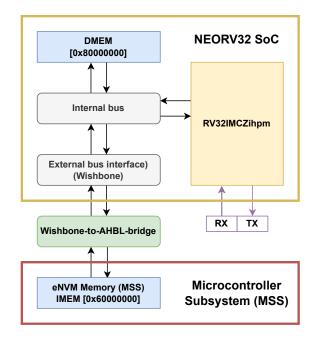

The NEORV32 processor is an upcoming customizable System on Chip (SoC) built around the RISC-V-compatible NEORV32 CPU [30]. This open-source RISC-V processor was released in 2020 and is written in platform-independent VHDL. Platformindependent code does not use any vendor-specific primitives, attributes, macros, or libraries. The goal of NEORV32 is to offer a RISC-V core with execution safety in mind. There are many open-source RISC-V implementations available, and most of them focus on performance or area. Because safety features play a crucial role in ensuring reliable options, particularly in demanding and harsh environments, the NEORV32 has been chosen as the core. Besides safety, it also focuses on documentation, platform independence, portability, RISC-V compatibility, extensibility & customisation, and ease of use.

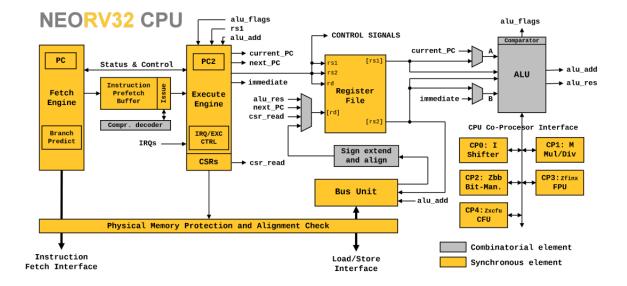

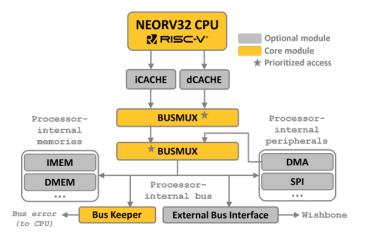

## 4.1 NEORV32 Processor & CPU

The NEORV32 CPU is a 32-bit RISC-V processor based on the rv32i instruction set architecture (ISA). It is designed to be fully compatible with the RISC-V architecture and has successfully passed the official architecture tests, ensuring its compliance and reliability. The NEORV32 CPU offers a rich set of customization options, allowing the user to tailor its functionality to their specific needs. These options include adding privileged architecture, ISA extensions and custom options for design goals. One of the key design goals of the NEORV32 CPU is to support Full Virtualization capabilities for the CPU and SoC, which increases security. The CPU carries an official RISC-V open-source architecture ID for recognition within the RISC-V ecosystem [31].

NEORV32 Processor (SoC) is a complete microcontroller-like processor system with high configurability. It is built upon the NEORV32 CPU architecture. The processor system offers optional serial interfaces, including UARTs, TWI, and SPI, allowing

|                                         | NEORV32 P                                            | rocessor            |                                  | neorv32_top.vhd       |                               |

|-----------------------------------------|------------------------------------------------------|---------------------|----------------------------------|-----------------------|-------------------------------|

| Clock & Reset                           | NEORV32 C<br>RV32 B C<br>Zmmul Zicnt<br>Sdext Sdtrig | EIMUX<br>rZihpmZife | RISC-V On-Chip<br>Debugger (OCD) | JTAG<br>(OpenOCD+gdb) |                               |

|                                         | BUS MUX                                              | BUS KEEPER          | SYSINFO                          |                       | → 1-Wire <sup>™</sup> bus     |

| 32x external>                           | 🔔 XIRQ                                               |                     | 🖨 CFS                            | XIP                   | XIP via SPI                   |

| TWI(I²C™) ◀                             | 👃 тwi                                                | DMEM                | IMEM                             | 🔔 UARTO               | UART                          |

| 64x IN<br>64x OUT                       | GPIO                                                 | dCACHE              | ICACHE                           | 👃 UART1               | ◀──► UART                     |

| 12x PWM <                               | PWM                                                  |                     | 👃 TRNG                           | 🔔 SPI                 | SPI (host)                    |

| WS2812 LEDs<br>(NeoPixel <sup>™</sup> ) |                                                      | 👃 WDT               | BOOTLDROM                        | 👃 SDI                 | SPI (device)                  |

| RX & TX                                 | 🔔 SLINK                                              | 🔔 DMA               | WISH                             | BONE                  | Wishbone (b4)<br>external bus |

| (AXI4-Stream <sup>ne</sup> )            | Core module<br>Optional m<br>Optional u              | -                   | le                               | GPU interrupt         | interface                     |

Figure 4.1: Overview of the NEORV32 Processor. Source: S. Nolting [30]

for versatile communication capabilities. In addition, it provides optional timers and counters, such as the Watchdog timer (WDT) and MTIME. To enhance its functionality, the NEORV32 Processor incorporates optional features like general-purpose IO and Pulse-Width Modulation (PWM). These features empower users to interface with external devices and control various peripherals. Furthermore, the processor system allows for optional caches for the data memory, instruction memory, and bootloader memory. For integration with external memory systems and custom connectivity, the NEORV32 Processor supports an optional external memory interface, namely Wishbone. Additionally, it provides a stream link interface (AXI4-Stream) to accommodate specialized data streaming needs. An optional execute-in-place (XIP) module is also available, enabling the execution of instructions directly from external memory, thereby improving performance. To facilitate debugging and troubleshooting processes, the NEORV32 Processor features an on-chip debugger that is fully compatible with OpenOCD and gdb. An overview of the CPU and SoC can be seen in figure 4.1.

### 4.2 RISC-V Standard Extensions Configurability

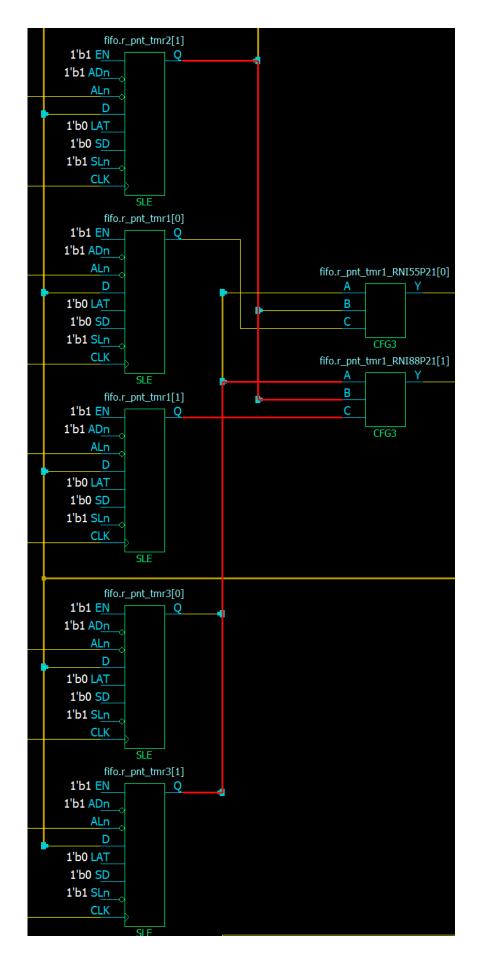

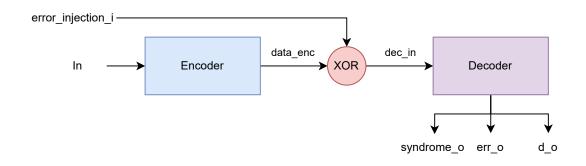

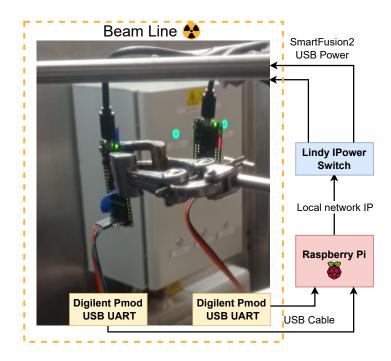

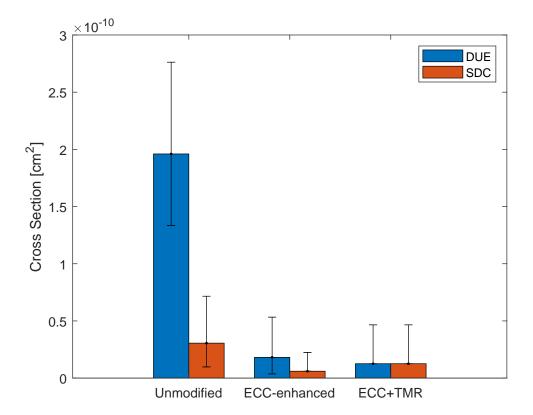

With the Application-Specific Processor Configuration, the SoC can be tailored to application-specific requirements. These configuration options are specified through generics within the top-level entity. By leveraging this flexibility, the SoC can be op-