MASTER THESIS

**CO-SIMULATION BETWEEN C $\lambda$ ASH

AND TRADITIONAL HDLS**

*Author:*

John Verheij

**Faculty of Electrical Engineering, Mathematics and Computer Science (EEMCS)

Computer Architecture for Embedded Systems (CAES)**

*Exam committee:*

Dr. Ir. C.P.R. Baaij

Dr. Ir. J. Kuper

Dr. Ir. J.F. Broenink

Ir. E. Molenkamp

August 19, 2016

**UNIVERSITY OF TWENTE.**

# Abstract

---

CλaSH is a functional *hardware description language* (HDL) developed at the CAES group of the University of Twente. CλaSH borrows both the syntax and semantics from the general-purpose functional programming language Haskell, meaning that circuit designers can define their circuits with regular Haskell syntax.

CλaSH contains a compiler for compiling circuits to traditional *hardware description languages*, like VHDL, Verilog, and SystemVerilog. Currently, compiling to traditional HDLs is one-way, meaning that CλaSH has no simulation options with the traditional HDLs.

Co-simulation could be used to simulate designs which are defined in multiple languages. With co-simulation it should be possible to use CλaSH as a verification language (test-bench) for traditional HDLs. Furthermore, circuits defined in traditional HDLs, can be used and simulated within CλaSH.

In this thesis, research is done on the co-simulation of CλaSH and traditional HDLs. Traditional *hardware description languages* are standardized and include an interface to communicate with *foreign* languages. This interface can be used to include foreign functions, or to make verification and co-simulation possible.

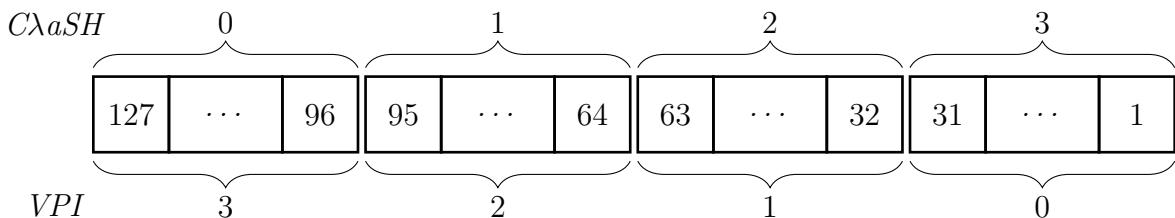

Because CλaSH also has possibilities to communicate with foreign languages, through Haskell *foreign function interface* (FFI), it is possible to set up co-simulation. The *Verilog Procedural Interface* (VPI), as defined in the IEEE 1364 standard, is used to set-up the communication and to control a Verilog simulator. An implementation is made, as will be described in this thesis, to show the practical feasibility of co-simulation of CλaSH and Verilog<sup>1</sup>.

The *VHDL Procedural Interface* (VHPI), as defined in the IEEE 1067 standard, is less popular compared with the VPI. Furthermore, not every VHDL simulator gives support for the VHPI. For example, ModelSim and QuestaSim use a different interface. The VHPI is set up in the same way as the VPI. The expectation is that co-simulation through the VHPI can be implemented in a comparable way.

GHDL, an open-source VHDL simulator, does however give support for the VPI and this interface could be used to set-up co-simulation between CλaSH and VHDL.

---

<sup>1</sup>The VPI can also be used to define co-simulation with SystemVerilog.

---

The co-simulation supports both combinational and synchronous sequential designs. A combinational circuit does not contain memory elements and the output can be seen as a pure function of the present input. This is in contrast to a synchronous sequential design, in which the output also depends on the history of the input.

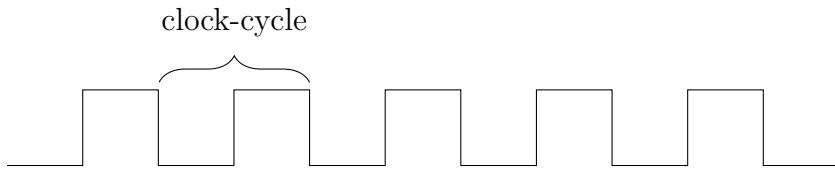

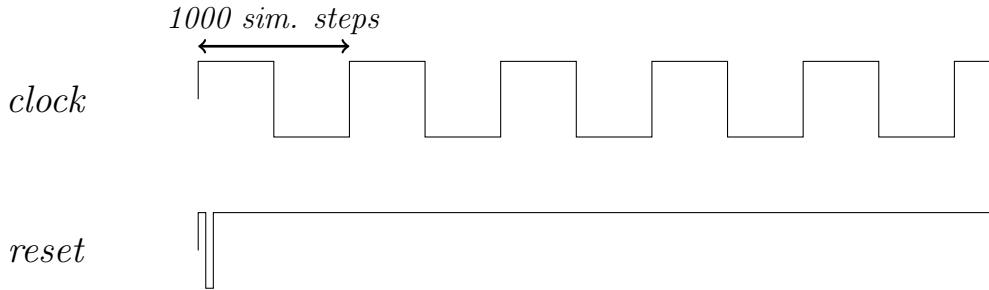

Within a synchronous sequential circuit, the changes in the state of the memory elements are synchronized by a clock signal. A clock is a periodic signal, in which every period is called a clock-cycle, as shown in Figure 1. A clock-cycle consists of multiple simulation steps. A simulation step can be associated with a certain time indication in the Verilog code, for example 1 nanosecond.

Figure 1: A clock signal

In typical *Register Transfer Level* (RTL) code, some events cause other events to occur in the same simulation step. For example, when a clock signal triggers, some signals may change in the same simulation step. To ensure race-free operations, HDLs must differentiate between such events with so-called 'delta' delays. However, CλaSH does not work with delta-delays and signals are defined per clock-cycle.

The defined co-simulation tries to seamlessly communicate with the traditional HDL and thus clock-cycles have the same length in both HDLs. A clock signal will change twice in one clock-signal. The recommendation is to define the clock-signals in the traditional HDL and only exchange the '*functional*' values.

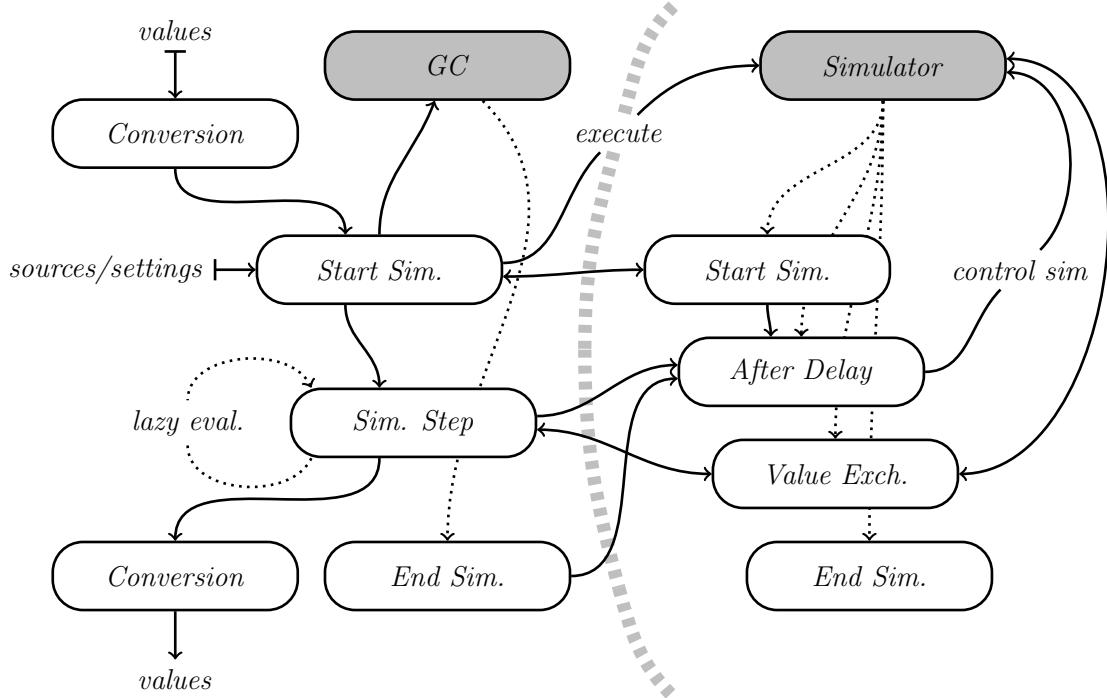

Support for (feedback) loops is created with lazy-evaluation. The implementation uses the *IO-monad* to control and to communicate with the traditional HDL simulators. Lazy IO often has as disadvantage that releasing acquired resources is unpredictable. Foreign memory allocations are connected to the Haskell's *Garbage Collector* (GC). With the use of the GC, foreign functions are invoked when a resource is released, in which a particular co-simulation is finished and the traditional HDL simulator is closed.

With *Quasiquotation*, *Inline-Verilog* is made possible. By using a *Quasiquoter* it is possible to define a *Domain Specific Language* (DSL). With *Inline-Verilog* it is possible to embed Verilog modules in CλaSH or to create a wrapper in which sub-modules (defined in verilog files) are included.

# Acknowledgements

---

After doing the *HBO* study '*Technische Informatica*' at Windesheim (Zwolle), I decided to do the Master study '*Embedded Systems*'. Input for this decision was conversations with my family, but also discussions with my piano teacher. Looking backwards, I am very happy for this decision and my knowledge, related to *Embedded Systems*, is very extended.

First of all I would like to thank Jan (Kuper) and Christiaan, for offering me this master thesis project and providing support. A year ago my knowledge about functional programming was very limited and I did not expect to learn so much in this field. I am very excited about CλaSH and the '*new*' possibilities on how to program FPGAs.

Furthermore, I would like to thank my exam commission for providing support and *time* during this graduation.

Joris, thanks for the conversations and the time we spend together during this master. I very liked our discussions, which also gave inspiration for this master thesis.

Guus and Rinse, for being my *day-time* room-mates and the conversations about holidays and technical things. The jokes we made together and the fun we had.

Harm, for the discussions on how to improve my implementation.

Bert Molenkamp, for always having time for checking & changing my study progress documents and the insights about VHDL & Verilog. And of course, for being part of my exam commission.

All members of the CAES group, thanks for the conversations and the time together during the breaks. This group also gave me a good impression about performing research and doing a PhD.

Finally I would like to thank my family and girlfriend for their support during my master and this thesis. Although we did not have much conversations about the technical part; I much appreciate the help with for example my car and all the other needed things.

John,

't Harde, August 2016

# Acronyms

---

|                                 |                                            |

|---------------------------------|--------------------------------------------|

| <b>C<math>\lambda</math>aSH</b> | CAES Language for Synchronous Hardware     |

| <b>CAES</b>                     | Computer Architecture for Embedded Systems |

| <b>Cocotb</b>                   | COroutine based COsimulation TestBench     |

| <b>DPI</b>                      | Direct Programming Interface               |

| <b>DSL</b>                      | Domain Specific Language                   |

| <b>EDA</b>                      | Electronic Design Automation               |

| <b>FFI</b>                      | Foreign Function Interface                 |

| <b>FLI</b>                      | Foreign Language Interface                 |

| <b>FPGA</b>                     | Field programmable Gate Array              |

| <b>GHC</b>                      | Glasgow Haskell Compiler                   |

| <b>GHDL</b>                     | G Hardware Design Language                 |

| <b>HDL</b>                      | Hardware Description Language              |

| <b>HVL</b>                      | Hardware Verification Language             |

| <b>IVI</b>                      | Icarus Verilog Interactive                 |

| <b>MAC</b>                      | Multiply ACCumulate                        |

| <b>PLI</b>                      | Program Language Interface                 |

| <b>RTL</b>                      | Register Transfer Level                    |

| <b>TH</b>                       | Template Haskell                           |

| <b>VHDL</b>                     | VHSIC Hardware Description Language        |

| <b>VHPI</b>                     | VHDL Procedural Interface                  |

| <b>VHSIC</b>                    | Very High Speed Integrated Circuit         |

| <b>VPI</b>                      | Verilog Procedural Interface               |

# Contents

---

|          |                                   |           |

|----------|-----------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>               | <b>1</b>  |

| 1.1      | Problem statement and approach    | 3         |

| 1.2      | Outline                           | 4         |

| <b>2</b> | <b>Background</b>                 | <b>5</b>  |

| 2.1      | C $\lambda$ aSH                   | 6         |

| 2.1.1    | Foreign Function Interface        | 9         |

| 2.1.2    | Template Haskell & QuasiQuotation | 11        |

| 2.2      | Related Work                      | 13        |

| 2.2.1    | MyHDL                             | 14        |

| 2.2.2    | Cocotb                            | 17        |

| 2.3      | Verilog & VHDL interfaces         | 19        |

| 2.3.1    | Verilog Procedural Interface      | 20        |

| 2.3.2    | VHDL Procedural Interface         | 21        |

| 2.3.3    | Other Foreign Interfaces          | 24        |

| <b>3</b> | <b>VPI</b>                        | <b>25</b> |

| 3.1      | Compiletf & Calltf                | 27        |

| 3.2      | Simulation Events & Callbacks     | 29        |

| 3.3      | Traversing hierarchy              | 33        |

| 3.4      | Reading & Modifying Values        | 36        |

|                                        |               |

|----------------------------------------|---------------|

| <b>4 Implementation .....</b>          | <b>39</b>     |

| 4.1 Overview .....                     | 39            |

| 4.2 CλaSH .....                        | 42            |

| 4.2.1 Type Conversion .....            | 43            |

| 4.2.2 Type Classes .....               | 46            |

| 4.2.3 Foreign Function Interface ..... | 51            |

| 4.3 VPI .....                          | 58            |

| 4.3.1 Simulation Callbacks .....       | 59            |

| 4.3.2 Analysing Design .....           | 61            |

| 4.3.3 Reading & Writing Values .....   | 65            |

| 4.4 Inline Verilog .....               | 67            |

| 4.5 Clock Cycles .....                 | 69            |

| <br><b>5 Results .....</b>             | <br><b>72</b> |

| 5.1 Simulators .....                   | 72            |

| 5.1.1 Icarus Verilog .....             | 73            |

| 5.1.2 ModelSim .....                   | 74            |

| 5.1.3 GHDL .....                       | 74            |

| 5.2 Examples and Benchmarks .....      | 75            |

| 5.2.1 Multiplier .....                 | 75            |

| 5.2.2 FIR filter .....                 | 78            |

| 5.2.3 GFSK demodulator .....           | 81            |

| <br><b>6 Recommendations .....</b>     | <br><b>86</b> |

| 6.1 IO monad .....                     | 86            |

| 6.2 Co-Simulation with VHDL .....      | 88            |

| 6.3 Multiple clock-domains .....       | 90            |

| 6.4 Inline Verilog .....               | 91            |

|                                        |            |

|----------------------------------------|------------|

| <b>7 Conclusion .....</b>              | <b>93</b>  |

| <b>A Higher Order Functions .....</b>  | <b>96</b>  |

| <b>B VPI system function pow .....</b> | <b>97</b>  |

| <b>C Marshalling functions .....</b>   | <b>99</b>  |

| <b>D Installation Simulators .....</b> | <b>101</b> |

| D.1 Icarus Verilog .....               | 101        |

| D.2 GHDL .....                         | 102        |

| D.3 ModelSim.....                      | 103        |

| <b>Bibliography .....</b>              | <b>104</b> |

# List of Figures

---

|     |                                                                                               |    |

|-----|-----------------------------------------------------------------------------------------------|----|

| 1   | A clock signal .....                                                                          |    |

| 1.1 | Sequential versus parallel implementation of a tap filter [21] .....                          | 1  |

| 2.1 | The mealy machine hardware representation .....                                               | 6  |

| 2.2 | The multiply accumulate operation .....                                                       | 7  |

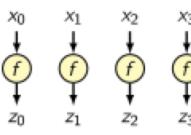

| 2.3 | The <i>mapAccumL</i> function .....                                                           | 7  |

| 2.4 | Co-simulation between C and VHDL using the FLI [18] .....                                     | 13 |

| 2.5 | The Cocotb overview [49] .....                                                                | 17 |

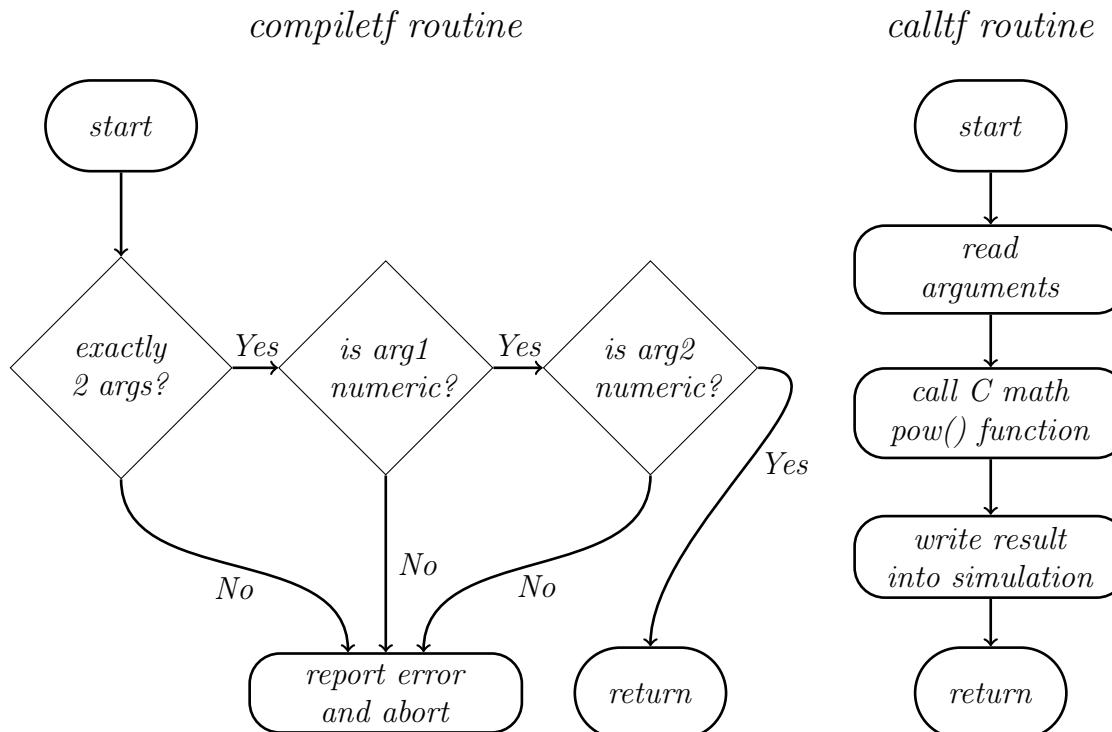

| 3.1 | The schematic overview of the <i>\$pow</i> -function [1] .....                                | 28 |

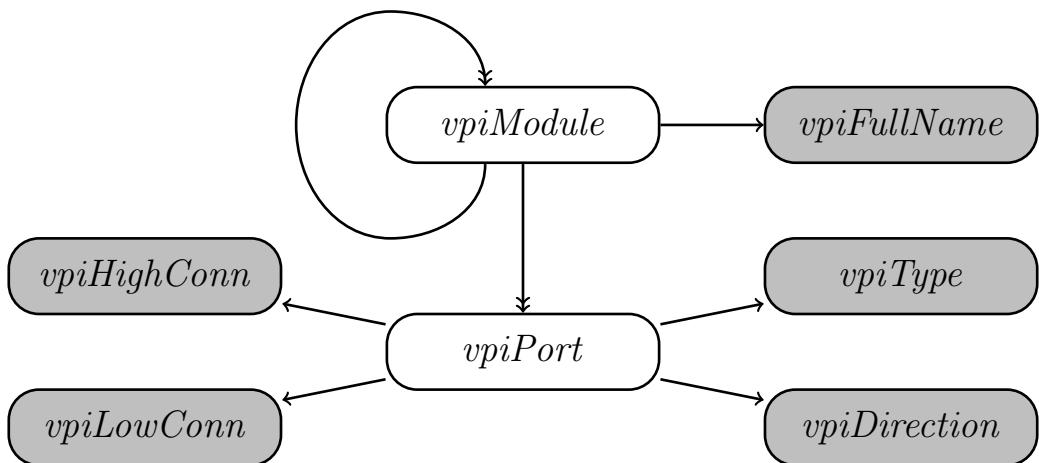

| 3.2 | A part of the VPI object diagram .....                                                        | 35 |

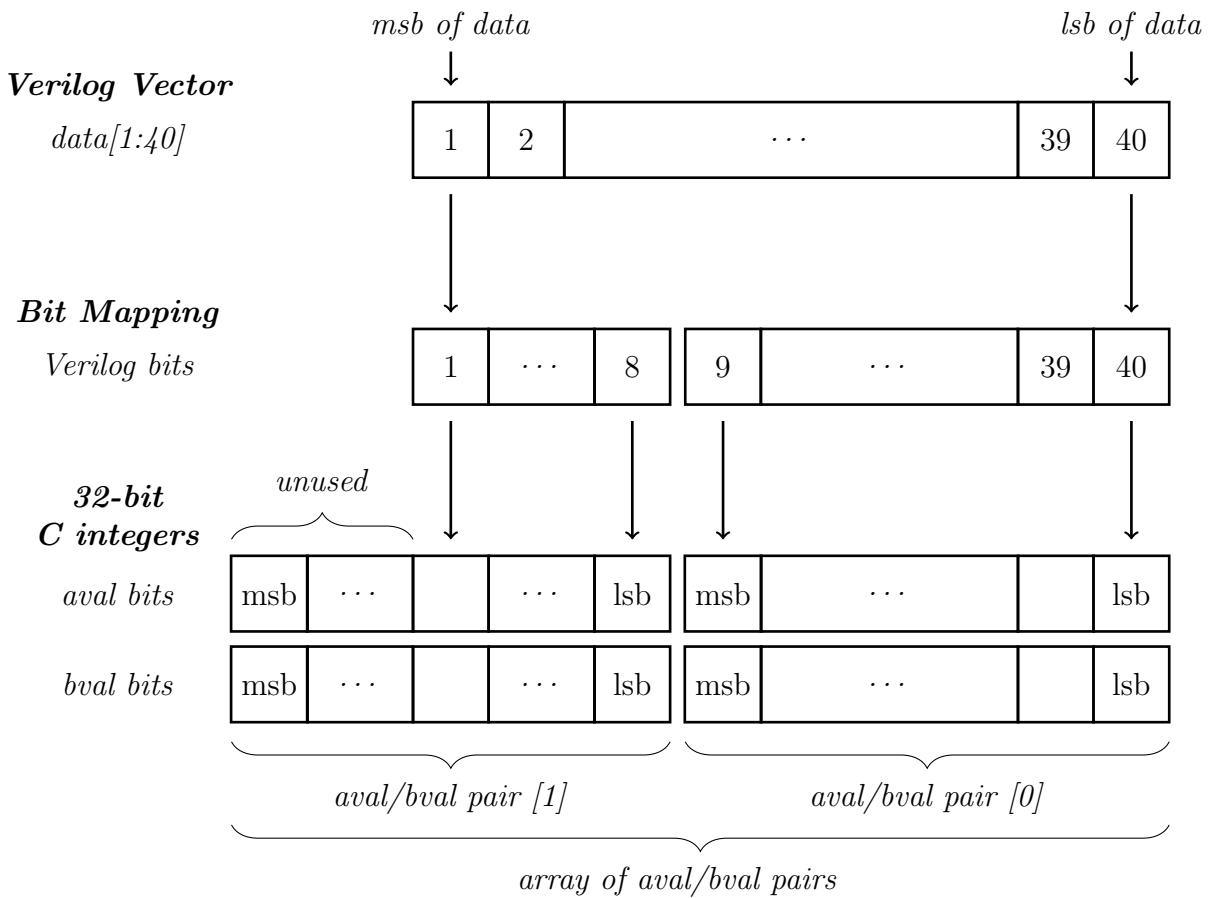

| 3.3 | The conversion from a Verilog vector to a <i>vpiVectorVal</i> [1] .....                       | 37 |

| 4.1 | The schematic overview of the co-simulation implementation .....                              | 40 |

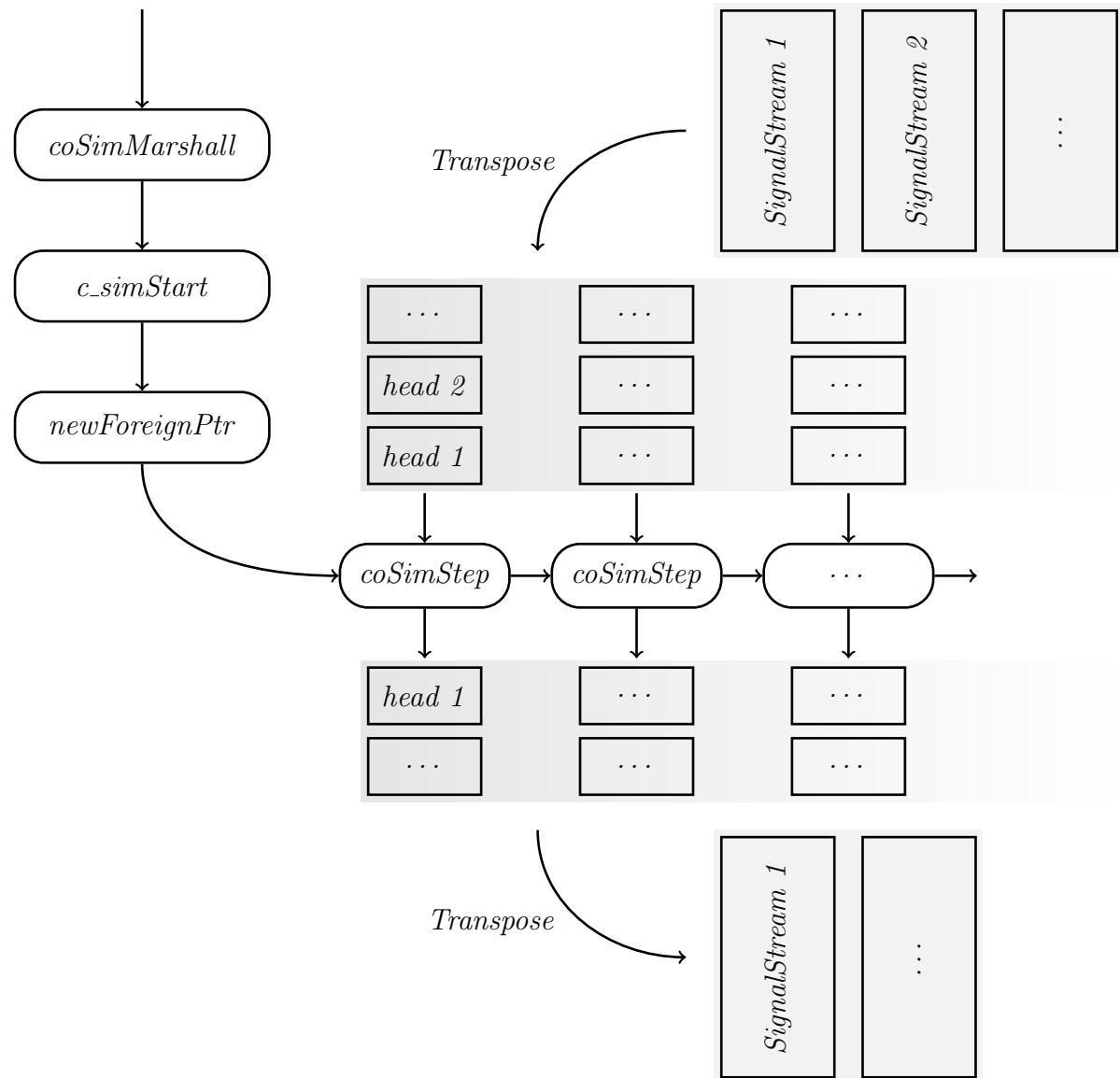

| 4.2 | The schematic overview of the input and output conversions .....                              | 50 |

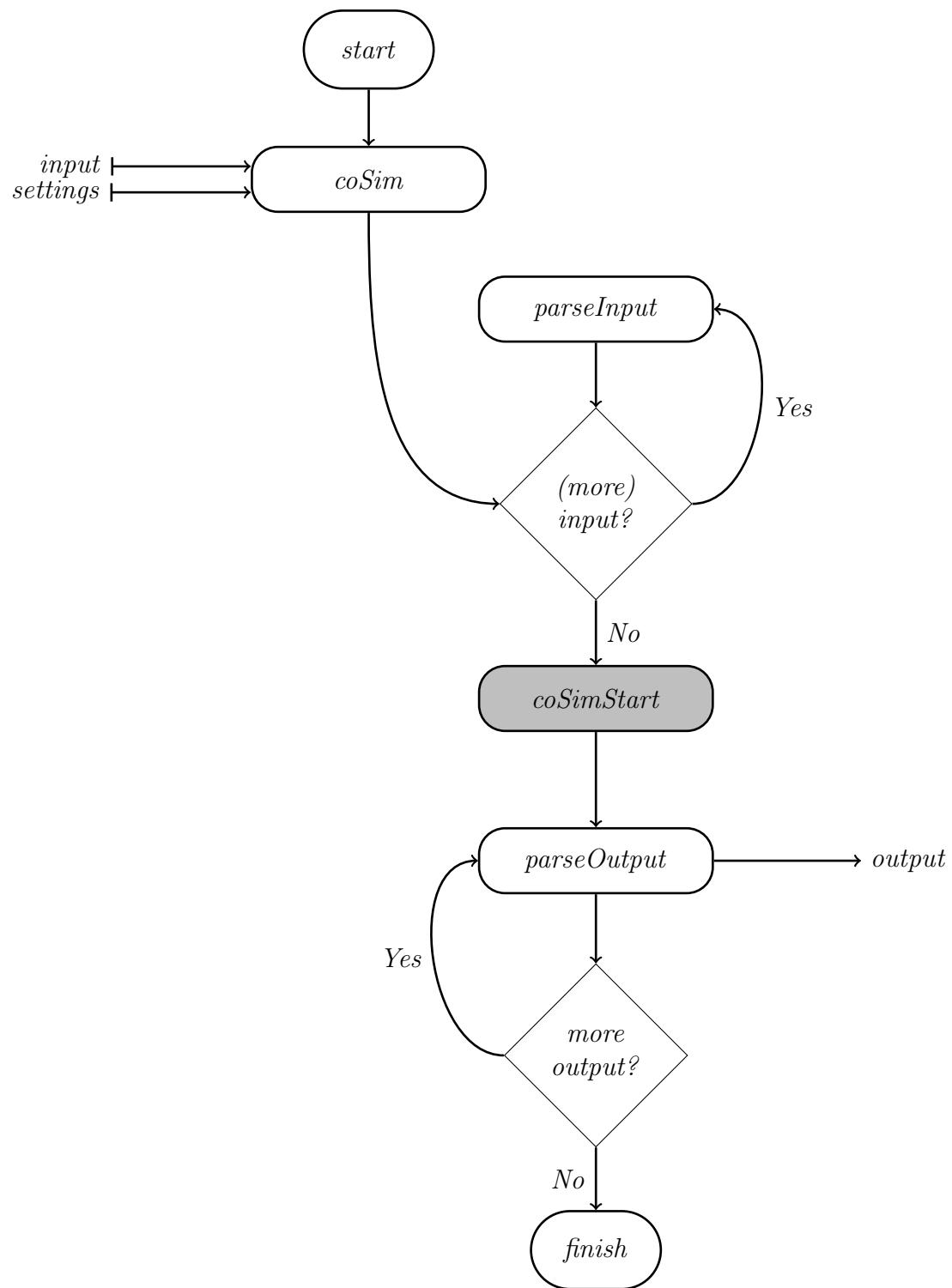

| 4.3 | The schematic overview of the function <i>coSimStart</i> .....                                | 55 |

| 4.4 | The ordering of the <i>Int32</i> values .....                                                 | 57 |

| 4.5 | Overview of the VPI application .....                                                         | 58 |

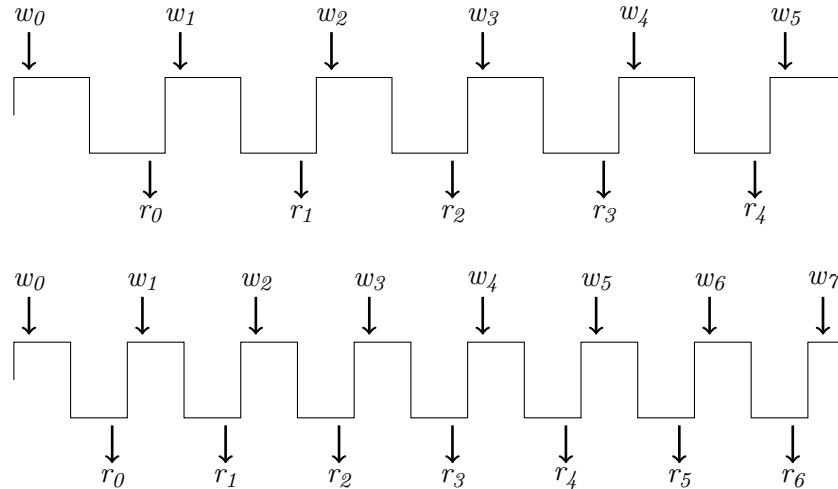

| 4.6 | Clock signal definitions .....                                                                | 70 |

| 5.1 | The <i>multiplier</i> example .....                                                           | 75 |

| 5.2 | The <i>FIR</i> filter example .....                                                           | 78 |

| 5.3 | The <i>clock</i> and <i>reset</i> used in the <i>FIR</i> filter example (co-simulation) ..... | 79 |

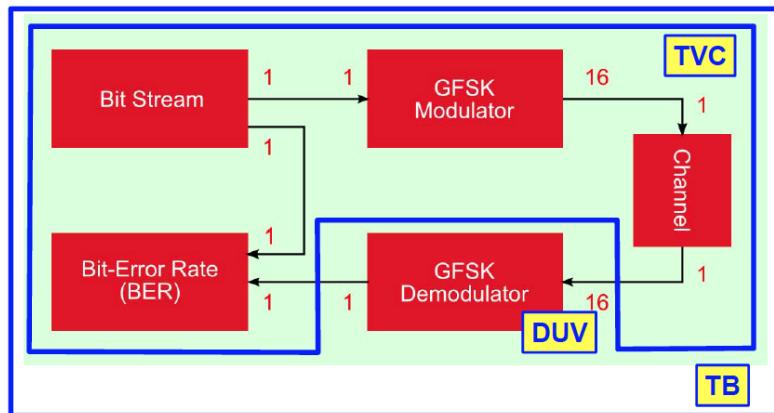

| 5.4 | The schematic overview of the GFSK design testbench [71] .....                                | 81 |

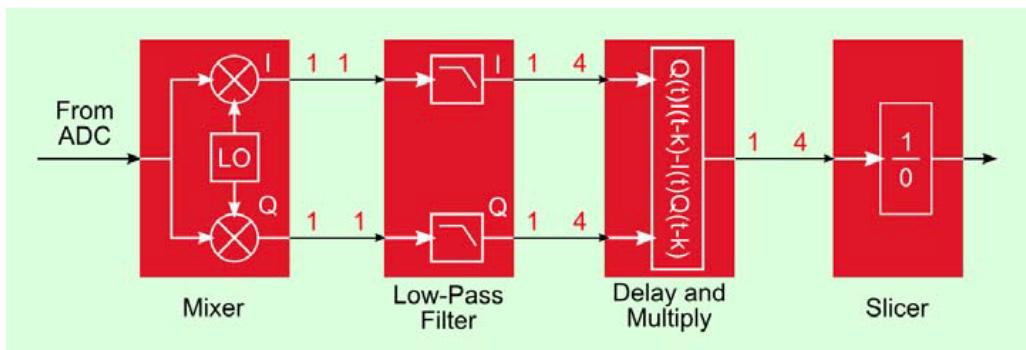

| 5.5 | The schematic overview of the GFSK demodulator [71] .....                                     | 81 |

| 5.6 | The <i>Mixer</i> .....                                                                        | 82 |

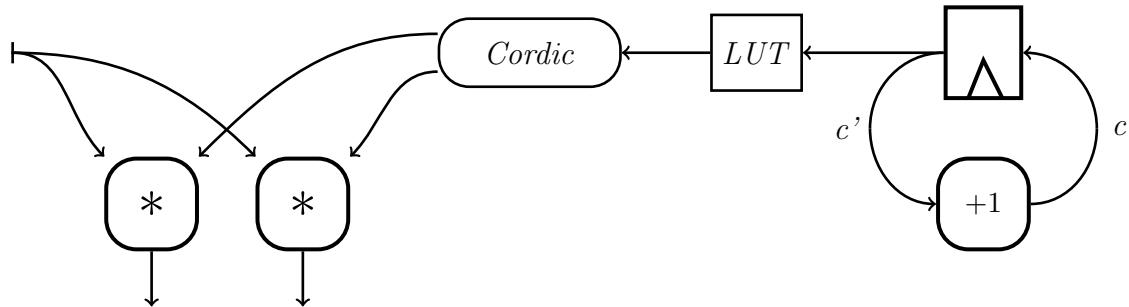

| 5.7 | The <i>Delay</i> and <i>Multiply</i> operation .....                                          | 82 |

| 5.8 | The <i>Slicer</i> .....                                                                       | 83 |

| 6.1 | Two different clock signals .....                                                             | 90 |

| A.1 | Structural representation of higher-order functions in Haskell .....                          | 96 |

# List of Tables

---

|     |                                                                      |    |

|-----|----------------------------------------------------------------------|----|

| 2.1 | Template Haskell's <i>Exp</i> constructors [53] .....                | 11 |

| 3.1 | VPI flags to control a simulation .....                              | 26 |

| 3.2 | The components of the struct <i>s_vpi_systf_data</i> .....           | 27 |

| 3.3 | The components of the struct <i>s_cb_data</i> .....                  | 29 |

| 3.4 | The VPI simulation time-related callbacks .....                      | 30 |

| 3.5 | The VPI simulation event-related callbacks .....                     | 32 |

| 3.6 | The VPI module-object properties .....                               | 33 |

| 4.1 | The components of the tuple <i>CoSimSettings</i> .....               | 42 |

| 5.1 | The execution times for simulating the <i>Multiplier</i> .....       | 77 |

| 5.2 | The execution times for simulating the <i>FIR</i> filter .....       | 80 |

| 5.3 | The execution times for simulating the <i>GFSK</i> demodulator ..... | 83 |

| 6.1 | Comparable VPI and VHPI routines .....                               | 88 |

| 6.2 | Comparable VPI and VHPI callbacks .....                              | 89 |

| 6.3 | Comparable VPI and VHPI properties .....                             | 89 |

# List of Listings

---

|      |                                                               |    |

|------|---------------------------------------------------------------|----|

| 2.1  | The <i>mealy</i> function with the MAC operation in CλaSH     | 7  |

| 2.2  | The function <i>main</i> with the <i>do notation</i>          | 8  |

| 2.3  | The execution of the <i>main</i> function                     | 8  |

| 2.4  | The imported Haskell-function <i>c_exp</i>                    | 9  |

| 2.5  | The commands to compile C code into a shared library          | 9  |

| 2.6  | The exported Haskell function <i>triple</i>                   | 10 |

| 2.7  | The imported FunPtr <i>p_free</i>                             | 10 |

| 2.8  | The <i>newForeignPtr</i> function                             | 10 |

| 2.9  | A <i>Template Haskell</i> example                             | 11 |

| 2.10 | The data type <i>QuasiQuoter</i> [54]                         | 12 |

| 2.11 | An example QuasiQuoter [52]                                   | 12 |

| 2.12 | Execution of the example QuasiQuoter [52]                     | 12 |

| 2.13 | An example generator [47]                                     | 14 |

| 2.14 | Executing the example generator [47]                          | 14 |

| 2.15 | A clock driver example [47]                                   | 14 |

| 2.16 | A hello world example using the clock driver [47]             | 15 |

| 2.17 | Executing the hello world example [47]                        | 15 |

| 2.18 | Registration of signals in Verilog [47]                       | 15 |

| 2.19 | Cosimulation object in Python [47]                            | 15 |

| 2.20 | Reset the DUT [49]                                            | 18 |

| 2.21 | A reset test [49]                                             | 18 |

| 2.22 | The declaration of a foreign function subprogram [9]          | 21 |

| 2.23 | VHPI callback registration [11]                               | 22 |

| 2.24 | The <i>register_cb</i> function [11]                          | 22 |

| 2.25 | The VHDL code which is connected to the VPHI application [11] | 23 |

| 2.26 | The imported C function <i>sin</i> in SystemVerilog           | 24 |

| 3.1  | The user-defined pow-function                                 | 28 |

| 3.2  | A possible uncertain event interleaving                       | 31 |

| 3.3  | Iterating through the VPI modules                             | 34 |

| 3.4  | Iterating through the VPI ports                               | 34 |

| 3.5  | Valid vector declarations [1]                                 | 37 |

| 3.6  | The VPI routines <i>vpi_get</i> & <i>vpi_get_value</i>        | 38 |

| 3.7  | The VPI routine <i>vpi_put_value</i>                          | 38 |

| 3.8  | The scheduled event                                           | 38 |

| 4.1  | A co-simulation example between CλaSH and Verilog             | 41 |

| 4.2  | Execution of the <i>verilog_mult</i> function                 | 41 |

---

|      |                                                                                         |    |

|------|-----------------------------------------------------------------------------------------|----|

| 4.3  | The type <i>CoSimSettings</i> . . . . .                                                 | 42 |

| 4.4  | Conversion to a list of 32-bit integers with the function <i>wordPack</i> . . . . .     | 43 |

| 4.5  | Conversion to <i>BitVector n</i> and <i>[Int32]</i> . . . . .                           | 44 |

| 4.6  | Influence of sign extension . . . . .                                                   | 44 |

| 4.7  | Conversion from a list of 32-bit integers with the function <i>wordUnpack</i> . . . . . | 45 |

| 4.8  | Conversion from <i>[Int32]</i> . . . . .                                                | 45 |

| 4.9  | The class <i>CoSimType t</i> . . . . .                                                  | 46 |

| 4.10 | The required type for a CλaSH value . . . . .                                           | 46 |

| 4.11 | The instance for a single CλaSH value . . . . .                                         | 46 |

| 4.12 | The instance for a CλaSH Signal . . . . .                                               | 47 |

| 4.13 | The instance for list with <i>Integer</i> values . . . . .                              | 47 |

| 4.14 | The <i>parseInput</i> function . . . . .                                                | 47 |

| 4.15 | The <i>parseOutput</i> function . . . . .                                               | 47 |

| 4.16 | The class <i>CoSim r</i> . . . . .                                                      | 48 |

| 4.17 | The <i>CoSim</i> instance for collecting all the input arguments . . . . .              | 49 |

| 4.18 | The <i>CoSim</i> instance for converting multiple outputs values . . . . .              | 49 |

| 4.19 | The <i>CoSim</i> instance for converting one output value . . . . .                     | 49 |

| 4.20 | The <i>coSim</i> function . . . . .                                                     | 51 |

| 4.21 | The foreign import of the <i>c_simStart</i> and <i>c_simEnd</i> functions . . . . .     | 51 |

| 4.22 | The function <i>coSimStart</i> . . . . .                                                | 52 |

| 4.23 | The <i>fromIntegral</i> function . . . . .                                              | 53 |

| 4.24 | String conversion . . . . .                                                             | 53 |

| 4.25 | Array conversion . . . . .                                                              | 53 |

| 4.26 | The struct <i>coSimState</i> . . . . .                                                  | 54 |

| 4.27 | The function <i>coSimStep</i> . . . . .                                                 | 56 |

| 4.28 | Foreign pointer functions . . . . .                                                     | 57 |

| 4.29 | Sending the input values to the Verilog simulator . . . . .                             | 57 |

| 4.30 | Retrieving the output values from the Verilog simulator . . . . .                       | 57 |

| 4.31 | The <i>vlog_startup_routines</i> . . . . .                                              | 59 |

| 4.32 | Registration of the <i>cbStartOfSimulation</i> callback . . . . .                       | 59 |

| 4.33 | The <i>registerCB</i> function . . . . .                                                | 60 |

| 4.34 | The <i>cbStartOfSimulation</i> callback function . . . . .                              | 61 |

| 4.35 | Traversing Verilog design . . . . .                                                     | 62 |

| 4.36 | Iterating through the module ports . . . . .                                            | 62 |

| 4.37 | The Verilog module <i>mult</i> . . . . .                                                | 63 |

| 4.38 | The struct <i>vpiState</i> . . . . .                                                    | 63 |

| 4.39 | The <i>cbEndOfSimulation</i> callback function . . . . .                                | 64 |

| 4.40 | The <i>synchStep</i> function . . . . .                                                 | 64 |

| 4.41 | Writing a value into the simulator . . . . .                                            | 65 |

| 4.42 | The <i>registerRD</i> function . . . . .                                                | 66 |

| 4.43 | Reading a value from the simulator . . . . .                                            | 66 |

| 4.44 | The function <i>createQuasiQuoter</i> . . . . .                                         | 67 |

| 4.45 | The Verilog <i>QuasiQuoter</i> . . . . .                                                | 67 |

| 4.46 | The generation of the <i>CoSimSettings</i> . . . . .                                    | 68 |

| 4.47 | The function definitions for updating the <i>CoSimSettings</i> . . . . .                | 68 |

|      |                                                                                   |     |

|------|-----------------------------------------------------------------------------------|-----|

| 4.48 | Conversion of clock-domains with the function <i>unsafeSynchronizer</i> . . . . . | 69  |

| 4.49 | A clock and reset signal defined in Verilog . . . . .                             | 71  |

| 5.1  | The multiplier example defined in CλaSH . . . . .                                 | 76  |

| 5.2  | The execution of the multiplier example in CλaSH . . . . .                        | 76  |

| 5.3  | The multiplier example defined with co-simulation . . . . .                       | 76  |

| 5.4  | The execution of the multiplier example using Icarus Verilog . . . . .            | 77  |

| 5.5  | The execution of the multiplier example using ModelSim . . . . .                  | 77  |

| 5.6  | The <i>FIR</i> filter example defined in CλaSH [3] . . . . .                      | 78  |

| 5.7  | The execution of the <i>FIR</i> filter example in CλaSH . . . . .                 | 79  |

| 5.8  | The <i>FIR</i> filter example defined with co-simulation . . . . .                | 79  |

| 5.9  | The execution of the <i>FIR</i> filter example using co-simulation . . . . .      | 80  |

| 5.10 | The failed assertion in the <i>malloc</i> source . . . . .                        | 84  |

| 5.11 | The <i>GFSK</i> demodulator example defined with co-simulation . . . . .          | 84  |

| 5.12 | The <i>GFSK</i> test-bench . . . . .                                              | 85  |

| 5.13 | The execution of the <i>GFSK</i> test-benches . . . . .                           | 85  |

| 6.1  | A possible implementation of the <i>mapAccumLM</i> . . . . .                      | 87  |

| 6.2  | The implemented <i>mapAccumLM</i> function . . . . .                              | 87  |

| 6.3  | An <i>AntiQuotation</i> example . . . . .                                         | 91  |

| 6.4  | An Inline-C example . . . . .                                                     | 91  |

| 6.5  | An Inline-R example . . . . .                                                     | 92  |

| 6.6  | A spliced Haskell function in R . . . . .                                         | 92  |

| 6.7  | A co-simulation example with AntiQuotation . . . . .                              | 92  |

| B.1  | The registration of the pow-function . . . . .                                    | 97  |

| B.2  | The calltf routine needed for the pow-function (part A) . . . . .                 | 97  |

| B.3  | The calltf routine needed for the pow-function (part B) . . . . .                 | 98  |

| B.4  | The compiletf routine needed for the pow-function . . . . .                       | 98  |

| C.1  | The function <i>coSimMarshall</i> . . . . .                                       | 99  |

| C.2  | The function <i>pokeArray'</i> . . . . .                                          | 99  |

| C.3  | The function <i>peekArray'</i> . . . . .                                          | 99  |

| C.4  | Foreign imports . . . . .                                                         | 100 |

| C.5  | The function <i>coSimInput</i> . . . . .                                          | 100 |

| C.6  | The function <i>coSimOutput</i> . . . . .                                         | 100 |

| D.1  | Installing Icarus Verilog . . . . .                                               | 101 |

| D.2  | Installing GHDL . . . . .                                                         | 102 |

| D.3  | Installing ModelSim . . . . .                                                     | 103 |

| D.4  | Vsim settings . . . . .                                                           | 103 |

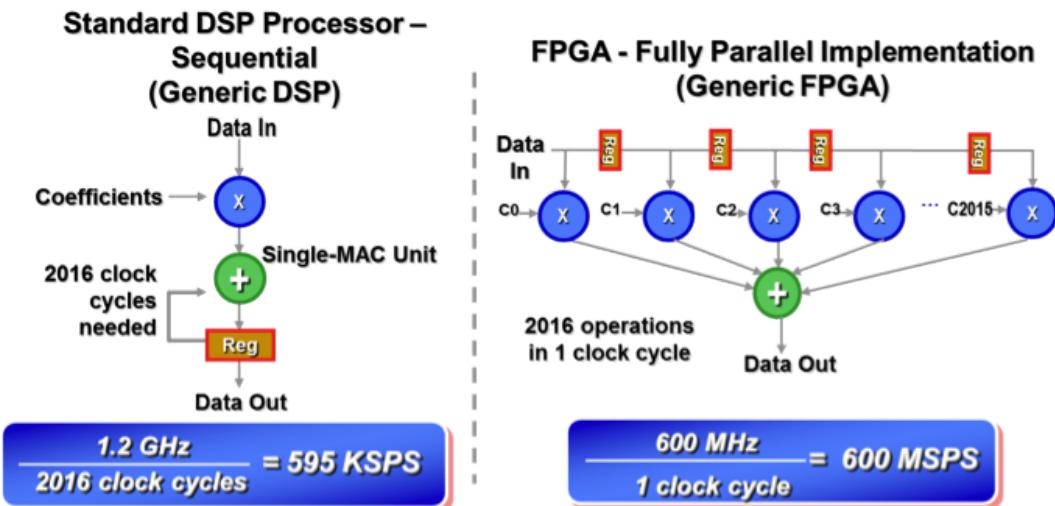

A *Field Programmable Gate Array* (FPGA) is a reprogrammable silicon chip, which can be configured with prebuilt logic blocks and programmable routing resources to implement custom hardware functionality. Unlike processors, FPGAs are truly parallel in nature and different processing operations can function deterministically and do not have to compete for resources [21].

A processor-based system often consists of several layers of abstraction, to perform scheduling tasks, and share resources for multiple processes. A processor core can only execute a few instructions at a time (instruction pipelining) and processor-based systems have continuously the risk of time-critical tasks pre-empting each other [21].

Figure 1.1: Sequential versus parallel implementation of a tap filter [21]

As visible in Figure 1.1, FPGAs can be used to speed up calculations, because of their parallel nature. Using such accelerators often leads to discussions of using FPGAs versus using *Graphics Processing Units* (GPUs). GPUs are mainly known for doing calculations related to 3D computer graphics, but GPUs are also used to accelerate scientific, analytics, engineering, consumer, and enterprise applications [22].

A paradigm shift is going on related to metric for procurements, system design, and application development. In the past *Floating-point Operations Per Second* (FLOPs) were used as measure for computer performance, which is now changing to FLOPs per watt. Energy costs become more and more important, and *performance at any cost* is no longer viable. The operational costs of supercomputer clusters become more dominant compared with the acquisition costs [24].

Research to device-energy-efficiency, related to application performance, showed that FPGAs are more energy efficient compared to GPUs, but FPGAs are considered hard to program [23]. Organisations, like Microsoft's Bing, are investing in FPGA-based codings, because of power efficiency. Microsoft Research touted that a *convolutional neural networks* (CNNs) implementation on a FPGA can achieve a three times better performance-to-power advantage compared to running on GPUs [24].

In the past, FPGA technology was only available for engineers with solid understanding of digital hardware design. With the rise of high-level tools and *Hardware Description Languages* (HDLs), new technologies became available to convert graphical block diagrams or even languages like C or Python into a digital hardware circuit.

C $\lambda$ SH is a high-level functional HDL, which borrows both the syntax and semantics from the functional programming language Haskell. With this language, hardware can be described and compiled to traditional HDLs, like VHDL, Verilog, and SystemVerilog.

Co-simulation of C $\lambda$ SH and traditional HDLs is not supported currently. With co-simulation, different subsystems can be simulated in a distributed manner. The execution of these subsystems, and the data-exchange between them, often happen in a black-box manner. This gives the user the idea of simulating, for example, two different languages in one system.

In this thesis, the issue of supporting co-simulation between C $\lambda$ SH and traditional HDLs is addressed. The main focus will be on co-simulation with Verilog, because the *Verilog Procedural Interface* (VPI), part of the IEEE 1364 standard, is popular and widely accepted. For example with VHDL, simulators use different standards and in some cases licenses are needed.

Defining co-simulation between a functional and a traditional HDL is more complicated than defining co-simulation between two different traditional HDLs. In a functional HDL like C $\lambda$ SH, there is no notion of delays and clocks are only used as annotations for signals. Signals are simulated as streams of values, in which transitions happen on the same moments. Furthermore, the co-simulation is only possible through the C-programming language, which does not support the same data types as in C $\lambda$ SH and memory management has to be implemented manually. The two HDLs has to be synchronized and the lazy evaluation of signals has to be transformed to the appropriate simulation cycles.

## 1.1 Problem statement and approach

The ability to perform co-simulation with (traditional) HDLs is desirable within CλaSH. In other high-level HDLs, like *MyHDL* and *Cocotb*, co-simulation is possible to a certain level.

CλaSH does not have the functionality to perform co-simulation with, for example, VHDL or Verilog currently. This is considered as a shortcoming by some CλaSH users [25].

In this thesis, research is conducted to the *Verilog Procedural Interface* and the Haskell standard, to be able to support co-simulation. The research question central to this thesis will therefore be:

» *How can co-simulation with traditional HDLs be supported within CλaSH?*

This central research question gives rise to other questions and design choices, such as: which information has to be exchanged between CλaSH and a traditional HDL? Does the IEEE 1364 standard give possibilities for this communication and how can a simulation/simulator be controlled?

Furthermore, the possibilities and limitations of a (theoretical) co-simulation with CλaSH has to be identified. For example, traditional HDLs uses delta-delays to ensure race-free operations. CλaSH, on the other hand, uses a functional approach and support for (delta-)delays is very limited.

Finally, an implementation, using the VPI, will be made to show the feasibility of the co-simulation between CλaSH and Verilog.

## 1.2 Outline

In chapter 2, the background and related work with respect to co-simulation is presented. This chapter also gives a background on CλaSH. The *Foreign Function Interface* (FFI) and *QuasiQuotation*, both part of the Haskell language, are explained. Furthermore, related work, like *Cocotb* and *MyHDL*, is described. In the last part of this chapter, research is performed about the available Verilog and VHDL interfaces.

In chapter 3, the *Verilog Procedural Interface* (VPI) is presented. This interface is part of the IEEE 1364 standard and gives possibilities for communication with the C programming language. The needed information for defining co-simulation, like synchronizing with the simulator and data exchange, is explained in detail.

Chapter 3 and sections from chapter 2, the related work and the Verilog/VHDL interfaces, are described using literature study. The book [1] and the IEEE standards are used as the main resources for this research.

Chapter 4 shows how co-simulation between CλaSH and *Icarus Verilog*, an open-source Verilog simulator, could be implemented by using the VPI standard. Design choices are explained and additional information about Haskell's FFI and QuasiQuotation possibilities are given.

In chapter 5, results of the implemented co-simulation are presented and benchmarks are shown. Furthermore, the implementation is tested with other simulators, ModelSim and GHDL, to show the portability of the co-simulation. An implemented GFSK demodulator is compiled to Verilog and with the co-simulation compared to the CλaSH implementation.

In chapter 6, recommendations and ideas for future work are presented. One of the main points will be co-simulation with other HDLs and the feasibility of the needed implementations. Furthermore, ideas on how to give support for multiple clock domains are given. Recommendations with respect to *Inline Verilog* are made. *Inline Verilog* is one of the final goals of co-simulation, which gives support for embedding Verilog, as *Domain Specific Language*, in CλaSH.

Finally, in chapter 7, conclusions are drawn and a small evaluation of this master project is made.

# 2

# Background

---

*Hardware Description Languages* (HDL) describe the structure and behavior of electronic circuits. The description of a circuit can be synthesised into a *netlist*, which can be *placed* & *routed* to produce the *mask set*, used to create an integrated circuit.

In this master thesis, the focus will be on a *sub-set* of the *Hardware Description Languages*, which is needed to define co-simulation between CλaSH and traditional HDLs. Traditional HDLs, like VHDL, Verilog, and SystemVerilog, are standardized. These standards describe interfaces to communicate with foreign languages, which can be used to define co-simulation. Standards are needed to increase the quality and also the compatibility to work with different simulators, like Icarus Verilog and Modelsim.

HDLs are also defined in *high level* languages like Python and C. Popular implementations are *MyHDL* and *Cocotb*, both written in Python. MyHDL is defined as an HDL and a *Hardware Verification Language* (HVL), having co-simulation possibilities with Icarus Verilog and Cver (both open-source Verilog-simulators). Cocotb is mainly defined as a HVL and has support for a wide range of simulators.

In 2011 it was stated that verification consumes approximately 75% of the design resources and time scheduling [34]. *Electronic Design Automation* (EDA) companies try to increase the verification productivity with foreign interfaces, which can be used for co-simulation.

The options for co-simulation depends heavily on the available interfaces. The *Verilog Procedural Interface* (VPI) is the commonly used and recommended interface for Verilog, mainly because it is standardized and supported by many Verilog tool vendors. The *Programming Language Interface* (PLI 1.0), the precursor of VPI, is also still commonly used because of its widely documented interface.

For VHDL there are fewer possibilities compared to Verilog. Vendors often provide functionality that is similar to the VPI, but these are mainly vendor specific interfaces. An example is the *Foreign Language Interface* (FLI) of Modelsim. The recommended interface is the standardized *VHDL Procedural Interface* (VHPI), but this interface is not as popular as the VPI and there is less support from vendors [33]. The *Direct Programming Interface* (DPI) is available for SystemVerilog, but the VPI is also fully supported.

## 2.1 CλaSH

*CAES Language for Synchronous Hardware* (CλaSH) is a functional hardware description language defined within the *Computer Architecture for Embedded Systems* (CAES) group (University of Twente). CλaSH borrows both the syntax and semantics from Haskell, a general purpose functional programming language. Designers can define their circuits with regular Haskell syntax and use strong typing & higher order functions.

A functional programming language treats computation as the evaluation of mathematical functions. Combinational circuits can often be modelled as mathematical functions. Within CλaSH, functions are used to describe hardware. As in Haskell, a set of functions are provided in the CλaSH prelude library. With these functions, both combinational and synchronous sequential hardware can be designed.

An important type within CλaSH is the *Signal* type, an *infinite* stream of values used in a synchronous sequential circuit design. For example the *Mealy* machine, a classic machine model, uses the Signal types. The mealy machine is defined as the function *mealy* in the CλaSH prelude library.

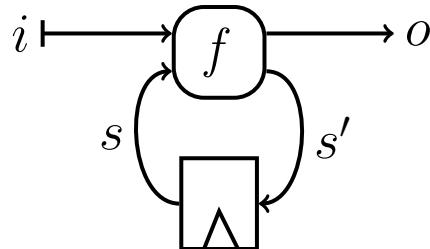

Figure 2.1: The mealy machine hardware representation

The input  $i$  and the output  $o$  are both signals. The signal  $i$  and the state  $s$  is fed into the function  $f$ , from which the updated state  $s'$  and signal  $o$  is defined: This is also visible in the type definition of the *mealy* function.

$$\text{mealy} :: (s \rightarrow i \rightarrow (s, o)) \rightarrow s \rightarrow \text{Signal } i \rightarrow \text{Signal } o$$

The identifiers  $s$ ,  $i$ , and  $o$ , used in the type definition of the *mealy* function, denote the types of input and output variables. This is in contrast to Figure 2.1, where they denote several variables. The first argument is a function, called  $f$ , which will be executed by the *mealy* function. The function  $f$  has as input a state with the type  $s$  and a input with the type  $i$ . Furthermore,  $f$  produces a tuple containing a updated state, with the same type  $s$ , and a output with the type  $o$ .

The second argument of the *mealy* function is given as initial state to the function  $f$ , after which  $f$  is mapped over the signal  $i$  to produce the signal  $o$ .

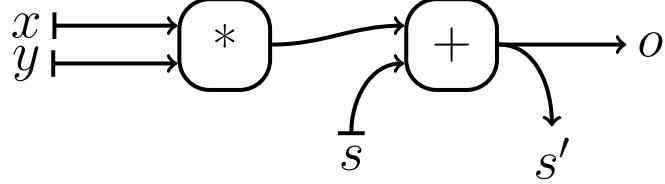

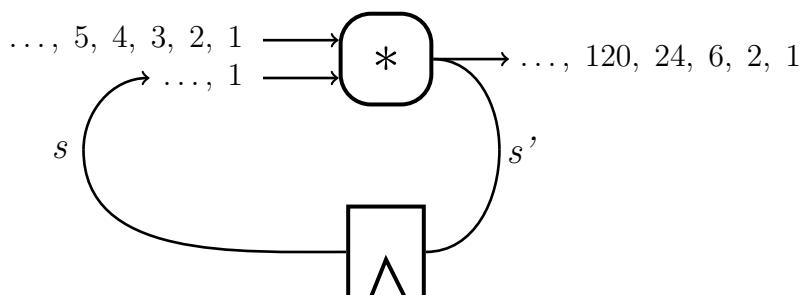

The function  $f$  is a combinational function, in which the output directly depends on the input without any memory elements. An example of such a function is the *Multiply Accumulate* (MAC) operation. Within the MAC operation, two values will be multiplied together and summed with the previous output value, as visualized in Figure 2.2. The CλaSH definition of the mealy machine with the MAC operation is shown in Listing 2.1.

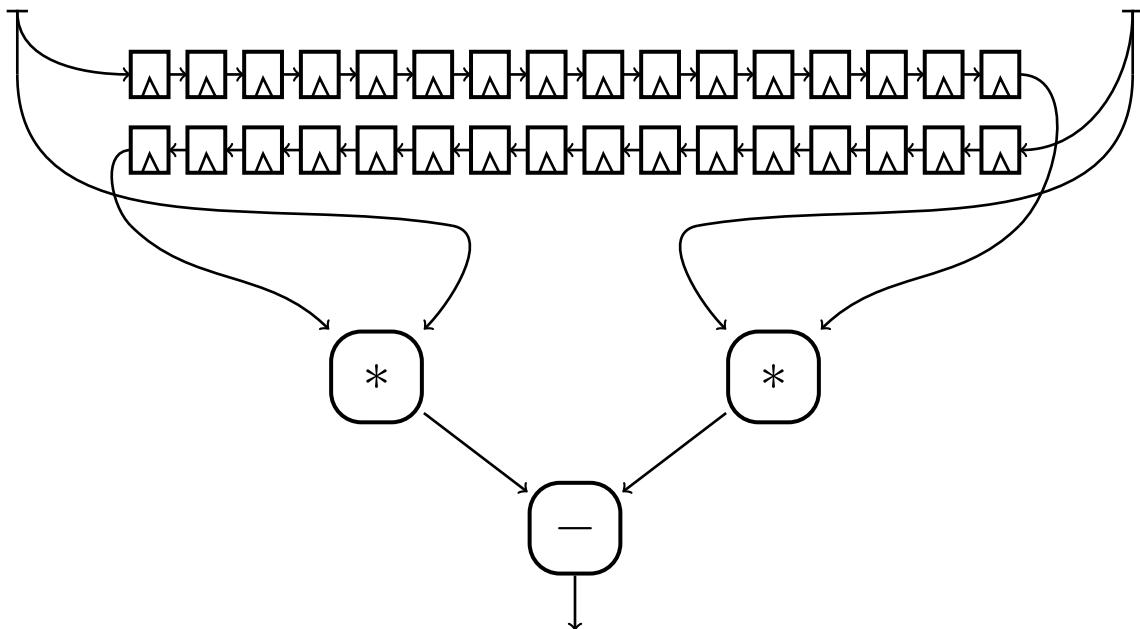

Figure 2.2: The multiply accumulate operation

```

topEntity :: t ~ Signed 16 => Signal (t, t) → Signal t

topEntity      = mealy mac 0

mac s (x,y) = (s', o)

where

s' = x * y + s

o = s'

```

Listing 2.1: The *mealy* function with the MAC operation in CλaSH

The types for the function *topEntity* are defined explicitly. In this case every sample, inside the signals, is defined as a 16 bits wide signed value. Specifying the types with their sizes (bounds) is needed to make compilation to synthesizable code possible. Currently the CλaSH compiler supports the generation of VHDL, Verilog, and SystemVerilog code.

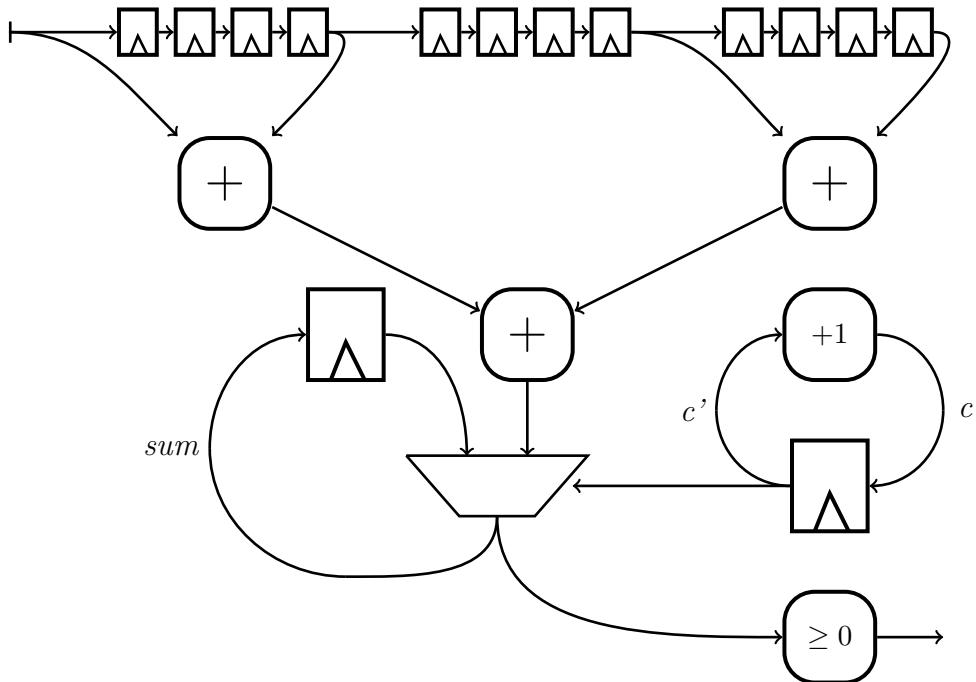

The function *mealy* is called a *higher-order* function, because it takes a function as an argument. Other examples of higher-order functions are: *map*, *zipWith*, *foldl*, *scnl*, and *mapAccumL*, as visualized in Appendix A.

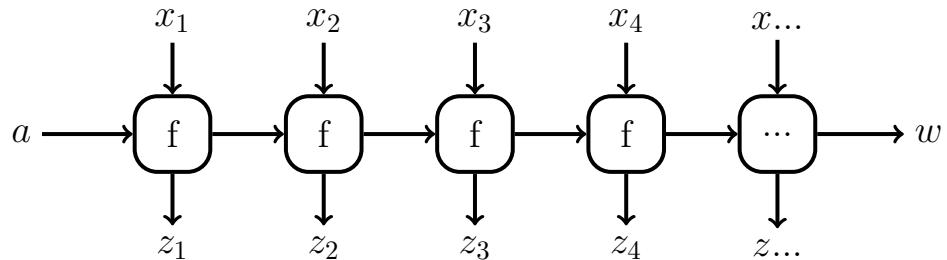

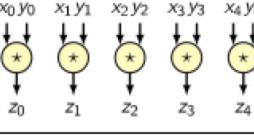

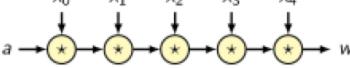

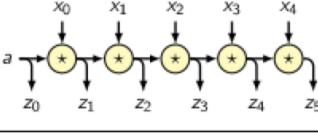

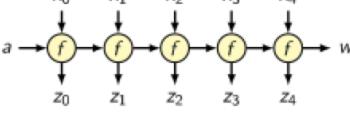

Figure 2.3: The *mapAccumL* function

The function  $f$ , used in the *mapAccumL* function, has as input an initial state  $a$  and the value  $x_i$ . It produces the output value  $z_i$  and an updated state  $a'$ , which is passed to the next  $f$  function.

Within CλaSH, the full Haskell environment can be used. This environment can be useful for extending the simulation possibilities in CλaSH (for example reading inputs from file), but for defining co-simulation it is actually a requirement. For example, the execution of C code, as will be explained in subsection 2.1.1, is needed to communicate with a (Verilog) simulator.

Haskell is a *pure* language, meaning that functions will always return the same outputs for the same inputs, without any side-effects. But it is possible to define *impure* functions with the usage of the so called *monads*. Monads allow a programmer to define computations using sequential building blocks. For example, the *Maybe* monad represent computations which may fail and the *List* monad represent computations with multiple values.

To define co-simulation, the IO monad becomes important. This monad makes (low-level) IO operations possible. Many of the possible functions in the IO monad are not *pure*, because they depend on the *external world* (e.g. operation system or other processes). The *do notation* is often used to combine multiple (IO) statements, as show in Listing 2.2.

```

main :: IO ()

main = do

putStrLn "What is your name? "

getLine >>= putStrLn . (P.++) "Hello "

```

Listing 2.2: The function *main* with the *do notation*

The function *putStrLn* will write *"What is your name? "* to the standard output, after which the function *getLine* is used to read a line from the standard input. The function *getLine* return an *IO String*, but with the pipe forward operator ( $>>=$ ) the encapsulated string is forwarded to the *putStrLn* function. The  $(.)$  operator denotes function composition. The string *"Hello "* will be concatenated with the input string, after which they are written to the standard output.

```

λ> main

What is your name? John

Hello John

```

Listing 2.3: The execution of the *main* function

To define a *Domain Specific Language* (DSL) in Haskell, the *Q* (abbreviation of Quotation) monad can be used. This monad is part of Template Haskell, as will be explained in subsection 2.1.2. A DSL could be interesting to include Verilog or VHDL code in the CλaSH code.

### 2.1.1 Foreign Function Interface

To define co-simulation, C $\lambda$ ASH has to perform IO operations, which can be done using the IO monad. Examples of IO operations are the creation of processes (e.g. the execution of the Verilog/VHDL simulator) and defining pipes to these processes. The Haskell package *process* contains libraries for dealing with these system processes, and gives support for IO operations [12]. This package and its dependency, the *unix* package, internally use the *Foreign Function Interface*. For example, the function *createProcess* is used to spawn an external process and the function *createPipe* is used to create a pipe for interprocess communication.

The *process* package does not provide enough functionality to control and communicate with a (traditional) HDL-simulator. As will be explained in section 2.3, the control and communication will not be done directly with the simulator, but through an interface; which is compiled to object code and loaded into the simulator at runtime.

The *Foreign Function Interface* (FFI) is an extension to the Haskell language and can be used to communicate with '*foreign*' languages (often C). The FFI is introduced by the 'Haskell 2010' revision and from then on further improvements are made [14].

The interface contains two concepts: the possibility to import and to export function(s). As example, to import a C function *exp* into Haskell, with as input and output argument a *double*, the following code can be defined:

```

foreign import ccall "exp" c_exp :: CDouble → CDouble

```

Listing 2.4: The imported Haskell-function *c\_exp*

In this case the function *c\_exp* acts like a normal Haskell function, but actually it calls the C function *exp* and returns the result of that function.

As a remark, in older versions of GHC (6.8.3 and earlier) it was needed to include the header file (in this case 'math.h').

Only C code, which is compiled to an object file, can be imported [13]. Furthermore, the option *Position Independent Code* (PIC) must be given to the C compiler. Code compiled with *-fPIC* is suitable for inclusion in a library, because the library must be re-located from its preferred location in memory to another address. The created object file must be compiled into a shared library, after which it can be loaded into the interpreter.

```

gcc -O2 -fPIC -c -Wall -o ffi.o ffi.c

gcc -O2 -shared -o libffi.so ffi.o

clash --interactive MyDesign.hs -lffi -L/tmp/ffi

```

Listing 2.5: The commands to compile C code into a shared library

The export functionality looks similar; instead of using the keyword *import*, the keyword *export* will be used. Listing 2.6 shows an example of an exported Haskell function.

```

triple :: Num a => a -> a

triple = (*3)

foreign export ccall triple :: CInt -> CInt

```

Listing 2.6: The exported Haskell function *triple*

Although the function *triple* will look like a normal C function in the C code, it is a binding to the Haskell function. The Haskell runtime environment must be initialized (with a call to *hs\_init*) and released (with a call to *hs\_exit*), in order to use the function *triple*.

Loading the code, as shown in Listing 2.6, in the interactive interpreter without any C code will give the error: *"Illegal foreign declaration: requires unregistered..."*. GHCi fails to link, because object-files are missing. By default, GHCi only generates byte-code. The flag *-fobject -code* can be used to have GHCi generate object-code instead of byte-code [15].

Besides using *objects*, like integers, it is also possible to use *pointers*. Within Haskell, a pointer will have the type *Ptr a*. The type *a* is often an instance of the class *Storable*, which provides marshalling operations. The FFI library also contains marshalling functions, for example to marshall Haskell lists to and from C arrays.

The *Ptr a* is used as pointer to a foreign object. To use pointers to functions, the type *FunPtr a* can be used. This pointer is callable from the foreign code, but with a *dynamic* stub the *FunPtr* can be converted to a corresponding Haskell function.

```

type Func a = Ptr a -> IO ()

foreign import ccall "&free" p_free :: FunPtr (Func a)

foreign import ccall "dynamic" c_dynamic :: FunPtr (Func a) -> (Func a)

```

Listing 2.7: The imported *FunPtr p\_free*

Function pointers can be used to connect *finalizers* to *object* pointers. Normally foreign objects are not managed by the Haskell storage manager (garbage collector) and the memory management has to be performed manually. By creating a *ForeignPtr*, the finalizer will be executed after the last reference to the foreign object is dropped.

```

type FinalizerPtr a = FunPtr (Ptr a -> IO ())

newForeignPtr :: FinalizerPtr a -> Ptr a -> IO (ForeignPtr a)

```

Listing 2.8: The *newForeignPtr* function

In the co-simulation implementation, as will be explained in subsection 4.2.3, C functions will be imported and finalizers will be used to interact and control a Verilog-simulator.

### 2.1.2 Template Haskell & QuasiQuotation

*Template Haskell* (TH) is a *Glasgow Haskell Compiler* (GHC) extension, which can be used in two main areas of application: compile-time meta programming and embedding domain specific languages [56][57].

Template Haskell provides features to convert between concrete syntax (normal Haskell code) and *Abstract Syntax Trees* (AST). Haskell values can be spliced into an AST and be manipulated at compile time. The abstract syntax tree can be spliced back into the concrete syntax [56][57].

TH programs are built inside the *Quotation* monad *Q*. Within Haskell, state monads like *Q* and *IO* are used to perform operations which can have side effects. Within the abstract syntax tree, a program is described using algebraic data types. The TH library provides the following algebraic data types: *Exp*, *Pat*, *Dec*, and *Type*, which can be used to represent expressions, patterns, declarations, and types, respectively. A possible operation within the *Q* monad is the name-generation operation, as shown in Listing 2.9 [53].

```

f = $(do

nm1 ← newName "x"

nm2 ← newName "y"

return $ LamE [VarP nm1, VarP nm2] $ UIInfixE (VarE nm1)

(VarE $ mkName "+") (VarE nm2))

```

Listing 2.9: A *Template Haskell* example

The function *f* performs an addition, which is implemented in Template Haskell. The functions *newName* and *mkName* functions are used to generate names. The name, as generated with the function *mkName*, can be captured; this in contrast to the function *newName*. Capturing is needed for the '+' operator, to make the summation of the two arguments possible. Finally, the abstract syntax tree is spliced back into concrete syntax using Template Haskell's splice operator \$.

*LamE*, *VarE*, and *UIInfixE* are used as expression constructors. *LamE* can be used as a lambda expression, *VarE* for defining a variable, and *UIInfixE* for performing an operation. *VarP* is used as pattern constructor [53].

| Constructor                    | Expression                     |

|--------------------------------|--------------------------------|

| VarE name                      | <i>x</i>                       |

| UIInfixE <i>Exp Exp Exp</i>    | <i>x + y</i>                   |

| LamE [ <i>Pat</i> ] <i>Exp</i> | $\lambda p1\ p2 \rightarrow e$ |

| TupE [ <i>Exp</i> ]            | ( <i>e1, e2</i> )              |

Table 2.1: Template Haskell's *Exp* constructors [53]

A *QuasiQuoter* is essentially a function which takes a string to an *Abstract Syntax Tree* (AST) [54]. *QuasiQuotation* is often used to write *Domain Specific Languages* (DSL). A parser, defined as *QuasiQuoter*, will transform a string into an AST during compile time.

Template Haskell defines the *QuasiQuoter* data type. This data type is actually a record with four *QuasiQuotors*, defined for the four algebraic data types, as shown in Listing 2.10.

```

data QuasiQuoter = QuasiQuoter {

— | Quasi—quoter for expressions, invoked by quotes like lhs = $[q|...]

quoteExp  :: String → Q Exp,

— | Quasi—quoter for patterns, invoked by quotes like f $[q|... ] = rhs

quotePat  :: String → Q Pat,

— | Quasi—quoter for types, invoked by quotes like f :: $[q|... ]

quoteType :: String → Q Type,

— | Quasi—quoter for declarations, invoked by top—level quotes

quoteDec  :: String → Q [Dec]

}

```

Listing 2.10: The data type *QuasiQuoter* [54]

The most trivial example is to immediately lift a string in the *Q* monad, as shown in Listing 2.11. The function *ex*, as shown in Listing 2.12, shows the execution of this *QuasiQuoter*.

```

qq :: QuasiQuoter

qq = QuasiQuoter { quoteExp = stringE }

```

Listing 2.11: An example *QuasiQuoter* [52]

```

{-# LANGUAGE QuasiQuotes #-}

ex :: String

ex = [qq|Hello|]

ex' :: String

ex' = $(quoteExp qq "Hello")

```

Listing 2.12: Execution of the example *QuasiQuoter* [52]

The expression quotation, as shown in the function *ex*, is written in the so called *Oxford brackets* and automatically spliced in the concrete syntax. This function is equivalent to the function *ex'*, in which the result of the function *quoteExp* is spliced back with Template Haskell's splice operator *\$*. The syntax used in the function *ex* is somewhat more convenient and Haskell will automatically pick the right parser for the context [52].

More advanced *QuasiQuoters* support meta-variables. The convention is to use the keyword *\$* to splice Haskell variables into a quotation. Constructors like *VarE* and functions like *mkName*, as shown in Listing 2.9, can be used to parse the meta-variables.

## 2.2 Related Work

Co-simulation with the standardized *Hardware Description Languages* is also implemented in related work, as will be shown in this chapter. In some cases, simulators are using co-simulation to add, for example, a graphical viewer. This is the case with GHDL, a VHDL simulator, which uses *Icarus Verilog Interactive* (IVI) as graphical viewer [40]. Matlab also defines co-simulation possibilities with ModelSim/QuastaSim and Incisive (Cadence) [43].

Looking at open-source co-simulation possibilities, it becomes visible that most of the implementations are defunct and not under development any more. Examples of these projects are: *PyHVL* (Python) [44], *Ruby-VPI* (Ruby) [45], *Jove* (Java) [46], and the implementation of *Andre Pool* [18]. However, *MyHDL* and *Cocotb* are still under development as will be described in the following two sections.

Most of the projects use the *Verilog Procedural Interface*, which is supported by multiple simulators, for defining co-simulation with Verilog and SystemVerilog.

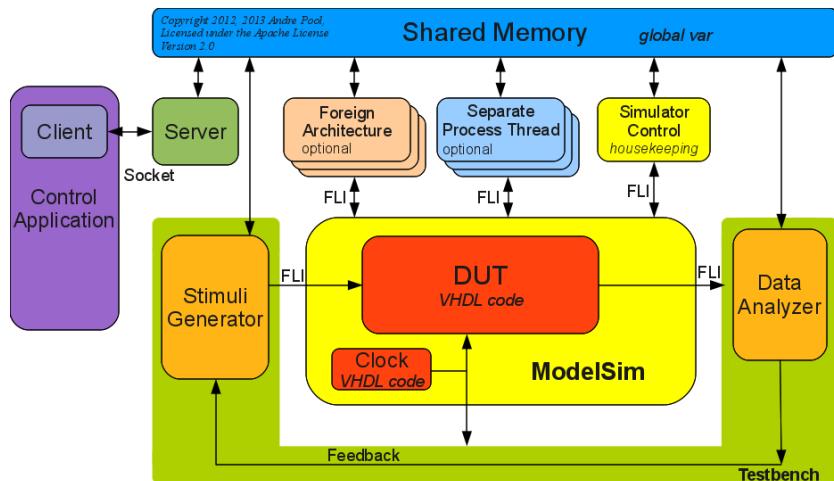

The implementation of *Andre Pool*, with the title '*Using ModelSim Foreign Language Interface for C*', only uses the *Foreign Language Interface* (FLI) of ModelSim, as visualized in Figure 2.4 [18].

Figure 2.4: Co-simulation between C and VHDL using the FLI [18]

The red parts denote a clock and the *Design Under Test* (DUT), both implemented in Verilog. However, the *TestBench*, consisting of a *Stimuli Generator* and a *Data Analyzer*, is implemented in C and connected through the FLI with the Verilog code.

The VHDL can also execute C code, defined as *Foreign Architectures* and *Separate Process Threads*, which are also connected through the FLI.

The other blocks are used to control the simulation and to do the memory management.

### 2.2.1 MyHDL

MyHDL is a hardware description and verification language written in Python. This package is free and open-source. The main goal of MyHDL is modelling and simulation. To some limitations, verification (using co-simulation) and conversion to Verilog and VHDL can be performed [47].

A key concept in MyHDL, but also in other Python-based HDLs, are generators. A generator is an object which contains one or more *yield* calls, and can be called iteratively with its *next* method. The MyHDLs manual gives the following example [47]:

```

def generator():

for i in range(3):

yield i

```

Listing 2.13: An example generator [47]

```

>>> g = generator()

>>> g.next()

0

>>> g.next()

1

>>> g.next()

2

>>> g.next()

Traceback (most recent call last):

File "<stdin>", line 1, in ?

StopIteration

```

Listing 2.14: Executing the example generator [47]

The *yield* values can be made sensitive to values or time, and are used as general sensitivity lists. This can be extended by the use of decorators, a special keyword in front of a function. With this keyword a function can be transformed into a generator. Generators are used to model concurrency. The following examples shows this in more detail.

```

def ClkDriver(clk):

halfPeriod = delay(10)

@always(halfPeriod)

def driveClk():

clk.next = not clk

return driveClk

```

Listing 2.15: A clock driver example [47]

```

def HelloWorld( clk ):

@always( clk . posedge )

def sayHello():

print "%s Hello World!" % now()

return sayHello

```

Listing 2.16: A hello world example using the clock driver [47]

```

clk = Signal(0)

sim = Simulation( ClkDriver( clk ) ,  HelloWorld( clk ) )

sim . run( 50 )

```

Listing 2.17: Executing the hello world example [47]

The decorator *@always* makes the functions sensitive to certain inputs. The function *ClkDriver* is made sensitive to a period of 10 time steps and the function *HelloWorld* is made sensitive to the positive edge of a clock.

Co-simulation between MyHDL and Verilog is defined using the VPI. Only two Verilog simulators are currently supported: Icarus Verilog and Cver. The *regs* and *nets*, which will be used within the co-simulation, must be registered with the functions *\$from\_myhdl* and *\$to\_myhdl*, as visualized in Listing 2.18 [48].

```

module dut_bin2gray;

reg [ `width-1:0] B;

wire [ `width-1:0] G;

initial begin

$from_myhdl(B);

$to_myhdl(G);

end

...

endmodule

```

Listing 2.18: Registration of signals in Verilog [47]

A *Cosimulation* object must be created in the Python code. This object will compile the verilog sources and execute the Verilog-simulator. Furthermore, the Python signals will be connected to the Verilog signals, as visible in Listing 2.19.

```

def bin2gray( B, G):

# compile of Verilog files

os . system( cmd )

# start simulator and connect signals

return Cosimulation( "vvp -m ./myhdl.vpi bin2gray" , B=B, G=G)

```

Listing 2.19: Cosimulation object in Python [47]

The co-simulation possibilities in MyHDL have some limitations [48]. First of all, both languages have to register the signals which will be used in the co-simulation. A more desirable approach would be to only register signals at the Python side and automatically recognize the ports of the top-level module in the Verilog-simulator.

Furthermore, only *passive* Verilog code can be used in the co-simulation, meaning that the Verilog code cannot contain any delay statements. One of the consequences is that clocks must be defined at the Python side [48].

Delta-cycles are only preserved from the MyHDL simulator towards the Verilog-simulator, but not in the opposite direction. Delta-cycles are implemented by making the time granularity in the Verilog simulator a 1000 times smaller than in the MyHDL simulator; meaning that for each MyHDL time step, 1000 Verilog steps are available for MyHDL delta-cycles. The value of 1000 steps is used, because the need for only a few delta-cycles per time step is assumed. Only after performing the 1000 steps, signal changes are returned to the MyHDL simulator [48].

It is unclear why 1000 simulation steps are used, theoretically it seems that less simulation steps would already be sufficient.

Only co-simulation with Verilog is possible and the development for co-simulation with VHDL is on hold (currently). In the MyHDL manual three requirements are given to be able to support co-simulation with VHDL:

1. A procedural interface to the internals of the simulator is needed.

2. The procedural interface should be a widely used industry standard.

3. The VHDL-simulator should be an open-source simulator.

Only the VHPI standard matches this requirement as a procedural interface, but this interface is less popular (compared with the VPI). Furthermore, there is only one credible open-source VHDL simulator (GHDL) and it is unclear whether it has VHPI capabilities that are powerful enough to support co-simulation [48].

An ideal (theoretical) co-simulation implementation between CλaSH and Verilog should not have the limitations which are described in this section. CλaSH should be able to automatically iterate through the Verilog hierarchy and scan for available input and output ports. These ports should be automatically mapped to CλaSH signals. Furthermore, it should be possible to define delay statements (e.g reset and clock streams) in Verilog, and use CλaSH as a pure functional HDL.

### 2.2.2 Cocotb

*COroutine based COsimulation TestBench* (Cocotb) is an environment for verifying VHDL/Verilog RTL using Python. Cocotb uses the VPI for Verilog and VHPI/FLI for VHDL, and gives support for the following simulators [49]:

- Icarus Verilog

- Aldec Riviera-PRO

- Synopsys VCS (only Linux)

- Cadence Incisive (only Linux)

- Mentor Modelsim

A cocotb testbench does not require additional VHDL/Verilog code. The so called Design Under Test (DUT) is instantiated as the toplevel in the simulator without any wrapper. From the python code, cocotb can drive stimulus into the inputs of the DUT and monitor the outputs.

The test environment can be fully defined in Python and the tests are simply Python functions (*coroutines*). With the *yield* keyword (see Listing 2.13) the control of execution can be switched between the simulator and the Python code [49].

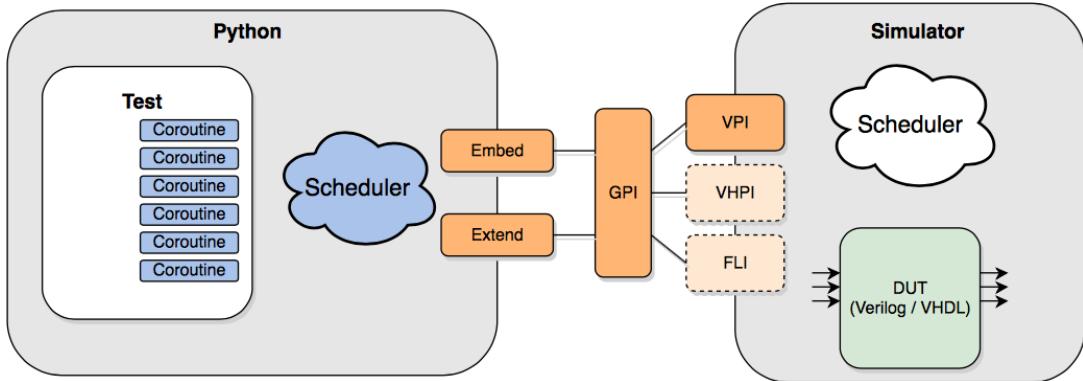

Figure 2.5: The Cocotb overview [49]

The GPI act as *General Purpose Interface*, to make interface independent commands possible at the Python Side. The VPI is used for a Verilog or SystemVerilog design, the VHPI is used for a VHDL design. ModelSim and QuestaSim have its own VHDL foreign interface, the FLI, which is also supported in Cocotb.

It seems that the keywords *Embed* and *Extend* indicate the parallel and sequential possibilities, but these two words are not explained.

Cocotb works with makefiles for specific simulators, such as Icarus Verilog or ModelSim, in which the verilog-sources and the name of the top-entity must be given. When Cocotb initialises, it finds the top-level instantiation in the simulator and creates a handle called *dut*. This handle can be used to access signals inside the design [49].

The usage of the handle *dut* is shown in the following examples. The signal *reset* is accessed inside the design with *dut.reset*. With the *yield* and *fork* commands sequential and parallel Cocotb routines can be executed.

```

@cocotb.coroutine

def reset_dut(reset_n, duration):

reset_n <= 0

yield Timer(duration)

reset_n <= 1

reset_n.log.debug("Reset complete")

```

Listing 2.20: Reset the DUT [49]

```

@cocotb.test()

def parallel_example(dut):

reset_n = dut.reset

# This will call reset_dut sequentially

# Execution will block until reset_dut has completed

yield reset_dut(reset_n, 500)

dut.log.debug("After reset")

# Call reset_dut in parallel with this coroutine

reset_thread = cocotb.fork(reset_dut(reset_n, 500))

yield Timer(250)

dut.log.debug("During reset (reset_n = %s)" % reset_n.value)

# Wait for the other thread to complete

yield reset_thread.join()

dut.log.debug("After reset")

```

Listing 2.21: A reset test [49]

Cocotb does not put any requirements on the VHDL or Verilog sources; delays can be put in both the HDL and Python. Furthermore, the VHDL and Verilog sources can be loaded in Cocotb without any changes. Cocotb automatically recognizes the available signals and creates handles to make them accessible in Python.

There is however one disadvantage: only one co-simulation can be performed at a time.

As will be shown in chapter 5, the implemented co-simulation between CλaSH and Verilog has the advantages of both MyHDL and Cocotb. CλaSH automatically recognizes the DUT and connects automatically CλaSH signals with Verilog ports. Multiple co-simulations in one CλaSH simulation can be performed using lazy evaluation, which is needed to independently define co-simulation in multiple functions. Furthermore, delay statements are allowed in the Verilog code.

## 2.3 Verilog & VHDL interfaces

The *Institute of Electrical and Electronics Engineers* (IEEE) is a leading standards development organization and in the area of *Hardware Description Languages* multiple standards are defined. VHDL is standardized in the IEEE 1076 standard, Verilog in the IEEE 1364 standard, and SystemVerilog in the IEEE 1800 standard. SystemVerilog was first seen as extension to the Verilog language, but since 2009 both languages are merged in the IEEE 1800 standard. SystemC, described as System-Level Modelling Language, can also be used as HDL and is standardized in the IEEE 1666 standard.

The history of interfaces to define communication between the (standardized) HDLs and Foreign Languages sees its origin in the 1980s. Verilog was created by Prabhu Goel and Phil Moorby around 1984, and at that time Verilog represented a tremendous productivity improvement for circuit designers. The Verilog PLI was first introduced in 1985 as part of a digital simulator called Verilog-XL, developed by Gateway Design automation; which later merged into Cadence Design Systems [1].

Around the same time, VHDL was developed commissioned by the U.S. Department of Defense (DoD), to document the behaviour of ASICs. In 1987 VHDL was standardized in the IEEE 1076-1987. Because of the increasing success of VHDL, Cadence decided to make Verilog available for open standardization. In 1995 it was standardized in the IEEE 1364-1995 standard [1].

Although Verilog already has foreign support from the beginning, VHDL was seen as a stand-alone language. Recognizing the Verilog PLI success, the IEEE 1067-1993 standard includes the foreign attribute. The foreign interface, VHPI, is included in the IEEE 1067-2008 standard, but at that time VHDL simulators had often defined their own interfaces.

In the 1990s, the Verilog PLI became very popular and successful. Mixed language simulators, primarily combining VHDL and Verilog, became common and a more generalized and lucid foreign interface with less overhead was desired. This interface, called the *Direct Programming Interface* (DPI), was defined in the SystemVerilog 3.1 standard, which was introduced in 2003. [19].

In 2001, the Verilog PLI was replaced by the *Verilog Procedural Interface* (VPI). In 2005, this interface was also included in the SystemVerilog standard [1][4].

In the following sections, information about the foreign interfaces will be given.

### 2.3.1 Verilog Procedural Interface

The *Verilog Procedural Interface* (VPI) gives possibilities to communicate with Verilog simulator(s) and is primarily intended for the C programming language. How to implement the VPI is explicitly defined in the *IEEE 1364* standard. This gives the advantages that every IEEE compliant Verilog simulator will use the same methods. In 1995 the IEEE chose to standardize the PLI 1.0 and 2.0 interfaces what resulted in VPI. PLI is an abbreviation for the *Program Language Interface* and mainly PLI 1.0 is still commonly used due to its widely documented function interface. In the IEEE 1364-2001 standard, the terms PLI 1.0 and PLI 2.0 do not exist, but they are referred as TF (task/function) and ACC (access) [1][4].

The *TF* library can only access the arguments of a system task or function. For simulators this is an advantage, because at compile time it is possible to exactly predict which information the PLI-application will access. For example, with a TF library it is not possible to traverse design hierarchy, analyze design structure, modify delays or access RTL code. In the beginning, the TF library was very small and contained a few C functions. Without any specification, the library evolved over the years and currently it contains more than 110 C functions. This give cause to inconsistency and redundancy. Furthermore, the library has problems with portability to different simulators and operation systems [1][4].

The *ACC* library is an extension of the TF library. In this library it is possible to access structural objects in a simulation data structure. This is done by using routines which can search for the structural objects, but it is limited to only accessing structural (netlist) based designs. The library cannot access all types of objects, like verilog procedures, continuous assignments, and memory arrays.

Performance is a limitation, because of the possible arbitrary access to objects. The simulator cannot predict what will be accessed and can thus not optimize the data structure. The ACC library suffers from many of the same problems as the TF library, like inconsistency and problems with the portability to different simulators [1][4].

The *VPI* library replaces the more than 220 C functions (that are complex, inconsistent and have portability problems) by 37 C functions in the IEEE 1364-2001 standard. The VPI provides full access to the RTL and the behavioral code. The functions are divided in three categories [1][4]:

- Locating objects

- Reading and modifying information about objects

- Utility routines for tasks (e.g. controlling simulation and file I/O)

These functions, as further explained in chapter 3, are used to define co-simulation between Verilog and high-level HDLs, like MyHDL and Cocotb.

### 2.3.2 VHDL Procedural Interface

The *VHDL Procedural Interface* (VHPI), as defined the IEEE 1076 standard, gives support for foreign communication with VHDL and is based on the *Verilog Procedural Interface*. Compared to VPI, VHPI has less support from vendors and some of them stick to their own interface, like ModelSim & QuestaSim with its *Foreign Language Interface* (FLI).

VHDL is a *Hardware Description Language* (HDL) and largely based on the programming language Ada. Originally, the associated mindset was that the language will mainly be used stand-alone, and would be self-contained. In the VHDL 93 revision the need for including non-VHDL code was recognized and resulted in the *Foreign* attribute.

```

package P is

function F return INTEGER;

attribute FOREIGN of F: function is "implementation-dependent info";

end package P;

```

Listing 2.22: The declaration of a foreign function subprogram [9]

The *Foreign* attribute was very limited in practice. This attribute gave possibilities for including non-VHDL sub-programs, but there was no support for traversing a VHDL hierarchy or synchronizing to simulation events. Looking at the capabilities of the Verilog PLI, vendors often provide mechanisms to communicate with foreign code. Most of these foreign functionalities are vendor specific and the capabilities vary across products. One of these interfaces is the *Foreign Language Interface*, as will be described in the next section.

In 2007, as an amendment to the VHDL 2002 standard, the *VHDL Procedural Interface* was introduced. The VHPI is an application-programming interface to VHDL simulators, which provides access to a VHDL model during its analysis, elaboration, and execution [10].

The VHPI consist of two aspects. The first aspect is an *information model* that represent the topology and the state of a VHDL model. This model is expressed in an object-orientated manner as a set of classes with relationships between them. A class is a data type that have data properties and sub-program operations.

The second aspect is a number of functions that can operate on the *information model* to access or affect the state of the VHDL model, and to control the VHDL simulator [10].

An *information model* is also referred as *Static VHDL Design Data*, which contains the behavioural and structural parts of the elaborated model. A VHPI application can traverse the hierarchy of this model, fetch the properties of VHDL objects, and navigate between these objects [10][11].

A VHPI application can access values of *Dynamic VHDL Objects*, such as signals and variables. These values can be fetched and modified using different formats as described in the IEEE standard [10][11].

Callbacks are used to create interaction with the simulation. A callback can be defined object related (e.g. executed when a value changes) or time related (connected to a simulation phase or executed after a number of simulation steps) [11].

The VHPI also provides *foreign* mechanisms to execute C code in a VHDL design. A VHPI application must be registered during simulation startup in order to work properly [11]. The following examples are copied from [11], to show a small VHPI example.

```

PLI_VOID startup() {

vhpiForeignDataT foreignData = {vhpiProcF, "test.dll", "test_init",

NULL, register_cb};

vhpi_register_foreignf(&foreignData);

}

PLI_VOID (*vhpi_startup_routines[])() = { startup, 0L };

```

Listing 2.23: VHPI callback registration [11]

The function-pointer array *vphi\_startup\_routines* is the starting point of a VHPI application. The functions in this array will be executed during simulation startup and can be used to register callbacks or foreign functions.

The function *startup* registers a *foreign procedure*, which is connected to the function *register\_cb* and can be executed in the VHDL code, as shown in Listing 2.23.

```

PLI_VOID register_cb ( const struct vhpiCbDataS* cb_p ) {

vhpiCbDataT      cbDataAction;

vhpiValueT       *Value;

vhpiTimeT        *Time;

vhpiHandleT hnd      = vhpi_handle_by_name("top.memory_var", NULL);

vhpiHandleT hnditr   = vhpi_iterator(vhpiIndexedNames, hnd);

Value = (vhpiValueT*) malloc ( sizeof(vhpiValueT) );

...

Value->format      = vhpiStrVal;

cbDataAction.value  = Value;

cbDataAction.cb_rtn = ValueChangeEvent;

cbDataAction.reason = vhpiCbValueChange;

while ( vhpiHandleT hndByIdx = vhpi_scan (hnditr) ) {

cbDataAction.obj   = hndByIdx;

vhpi_register_cb (&cbDataAction, vhpiReturnCb);

}

}

```

Listing 2.24: The *register\_cb* function [11]

The function *register\_cb*, as shown in Listing 2.24, iterates through the VHDL hierarchy (with the function *vhpi\_handle\_by\_name*) to get a handle to the array *memory\_var*. The *vhpiCbValueChange* callback is registered to every element of this array, with the format defined as *vphiStrVal*. When an element of *memory\_var* changes, the function *ValueChangeEvent* will be executed, with as argument the changed value (defined as string).

The VHDL code, as shown in Listing 2.25, defines the C function *register\_cb* as a foreign procedure with the name *callback\_event*. This foreign procedure is executed at the beginning of the process *proc1*. Within the function *register\_cb*, *vhpiCbValueChange* callbacks are connected to the array *memory\_var*. The other VHDL statements (in the process *proc1*) modify elements of the *memory\_var* array after certain delays. Each time that an element is modified, the C function *ValueChangeEvent* will be executed.

```

library ieee;

entity top is

end;

architecture top of top is

procedure callback_event;

attribute foreign of callback_event: procedure is "VHPI test;

test_init";

type MEM is array ( NATURAL range <> ) of BIT_VECTOR( 7 downto 0 );

signal memory_var : MEM( 3 downto 0 );

begin

proc1: process

begin

callback_event;

wait for 1 ps;      memory_var(0) <= "00111000";

wait for 1 ps;      memory_var(2) <= "10010010";

wait for 1 ps;      memory_var(3) <= "01101000";

wait;

end process;

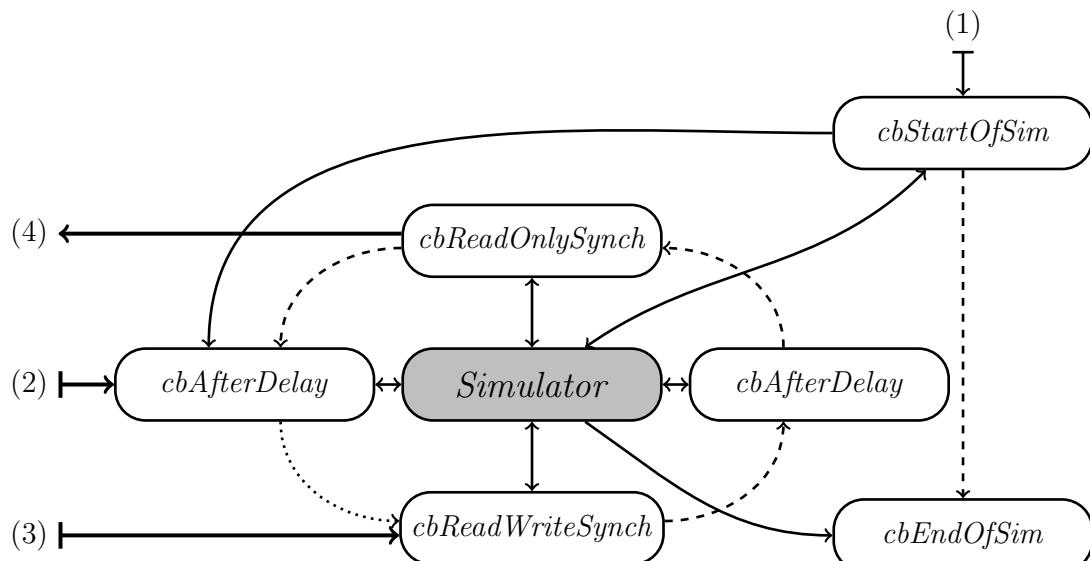

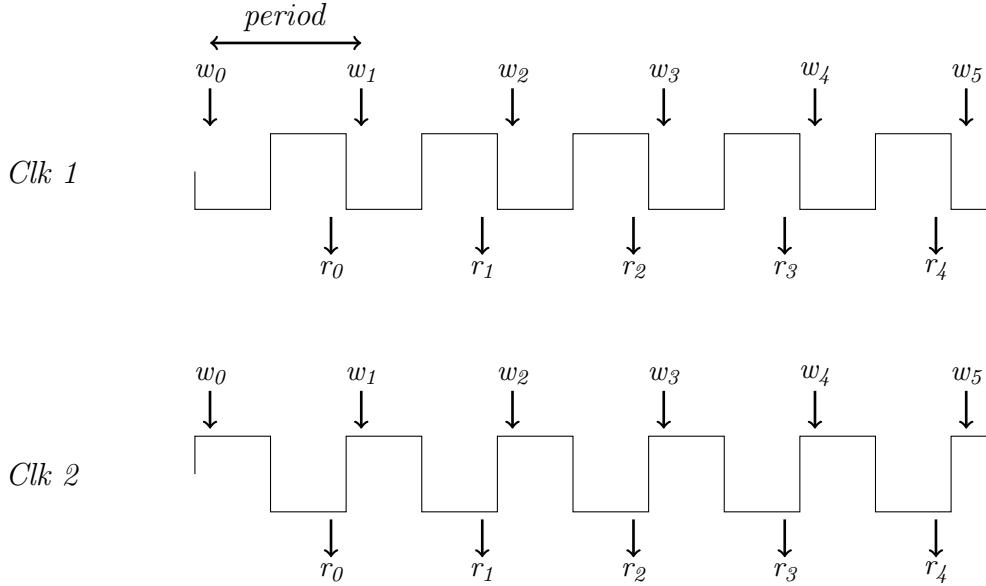

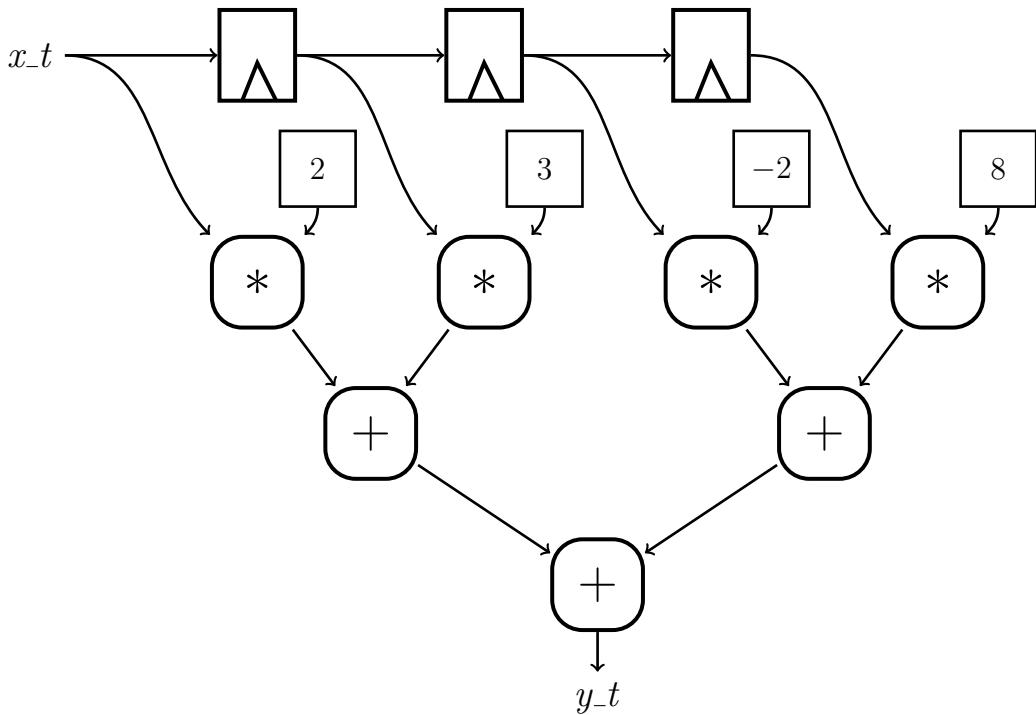

end;